# School of Electrical Engineering and Computing Department of Electrical and Computer Engineering

# Design and Synthesis of Reversible Logic

**Chua Shin Cheng**

This thesis is presented for the Degree of

Doctor of Philosophy

of

Curtin University

March 2016

## **DECLARATION**

| To the best | of my   | knowledge   | and b | belief, | this  | thesis | contains | no  | material   | previou  | sly |

|-------------|---------|-------------|-------|---------|-------|--------|----------|-----|------------|----------|-----|

| published b | y any o | ther person | excep | ot whe  | re du | e ackn | owledge  | mei | nt has bee | en made. |     |

This thesis contains no material which has been accepted for the award of any other degree or diploma in any university.

| Signature | : |                   |  |

|-----------|---|-------------------|--|

| C         |   | (CHUA SHIN CHENG) |  |

Date: March 2016

#### **ABSTRACT**

Power dissipation in modern technologies plays an important role and overheating is a serious issue to consider for both manufacturers and consumers. In the near future, manufacturer would face difficulty in implementing more advanced technology due to the limited operating temperature range for smaller devices such as smartphone, tablet and wearable devices. This issue is mainly caused by the use of the irreversible logic system in current technology devices which each logic gate dissipates heat during computations. To overcome this issue, new logic system, namely reversible logic has been investigated and has been identified to be one of the most promising solutions.

Reversible logic is an emerging research area and has been historically motivated by its theoretical research in low-power computing devices. Recently, it has attracted interest as part of components in these fields: quantum computing, optical computing and nanotechnology. However due to its intrinsic properties, design and synthesis methods used for traditional irreversible logic cannot be carried out on reversible logic. Therefore, new circuit designs and synthesis algorithms are being developed to incorporate the reversible logic based applications.

For a circuit to be reversible, the inputs and outputs of the circuit have to form a unique one-to-one mapping. At times, constant ancilla inputs and garbage outputs are added to create that unique one-to-one mapping to keep the circuit reversible. Parameters such as ancilla input, garbage output, quantum cost and delay play an important role in the evaluation of reversible circuits. Thus for any reversible logic design, it is important to minimize these parameters to achieve better efficiency. To design reversible synthesis algorithm, majority of the benchmark circuits have been optimized in terms of ancilla input and garbage output, hence minimizing gate count and quantum cost are the current focus in the field of reversible logic.

Although the research of reversible logic has achieved major breakthrough in design and synthesis, but various problems still exist and solution remains elusive. The biggest challenges face in the synthesis of reversible logic is that the existing synthesis algorithm is not able to full balance the gate count and quantum cost to achieve optimal solution for all synthesized reversible function. Recently with the

new quantum realization of the mixed-polarity Toffoli gate, synthesis algorithm is able to achieve one step further in scaling reversible function better and achieves close optimal result. Although several research works using this gate has been proposed, but further research can still be done to improve existing algorithms. For the research in designing reversible logic based arithmetic application, research attention has always been focused only on quantum cost, ancilla input and garbage output. Parameter such as propagation delay which is crucial in achieving fast executing time which is often neglected. As fast arithmetic is crucial it should not be neglected in any high speed arithmetic design. Thus these issues are addressed towards the finding of this research.

The first contribution of this dissertation is the design of a reversible logic synthesis algorithm. The proposed synthesis algorithm uses search-based technique that synthesizes reversible function into reversible circuits using NCT (NOT, CNOT, Toffoli) based library gates with positive and negative control lines. As taken into account, the proposed synthesis algorithm is designed to provide better quantum cost scaling which most existing synthesis algorithms fail to take care of. As per literature review, this is the first attempt to integrate Toffoli gate with mixed polarity control capability into search-based synthesis algorithm. Through the synthesis results obtained, it is concluded that the proposed algorithm is able to achieve close optimal result using the mixed-polarity Toffoli gate for all three and four variables based reversible functions.

The second contribution is the novel design of a new reversible gate which is developed to serve as a reversible full adder circuit. The proposed reversible gate mainly targets to overcome garbage output issue faced by existing designs while keeping other important parameters equal as compared to the existing designs. The proposed reversible full adder is designed using a mixture of various techniques. It is first designed using our proposed synthesis algorithm. The result obtained is then further optimized in term of quantum cost and propagation delay until its final form is achieved. Experimental result has shown that the proposed reversible full adder design outperforms existing design in terms of ancilla input, garbage output, quantum cost and propagation delay. As full adder circuit is required in almost all

digital arithmetic design, the proposed reversible full adder circuit will find its application in corresponding area.

The third contribution is the design of minimal delay reversible BCD adder. The reversible BCD adders are designed to delay the need of the carry input  $C_{in}$  and generate the required carry output  $C_{out}$  for the next BCD digit faster. This method allows simultaneous run of multiple BCD digits and achieves high speed BCD sum. This objective behind this method is to overcome the poor propagation delay exist in existing reversible BCD adder designs. As fast executing time is essential for arithmetic unit, propagation delay should not be neglected. Hence the proposed BCD adder designs will be beneficial in reversible arithmetic area requiring fast BCD sum. Experimental result has shown that the proposed BCD adder designs outperform existing designs in term of propagation delay while maintaining other important parameter at reasonable range.

The last contribution in this dissertation is the design of low quantum cost reversible BCD adders. As quantum cost remain as the most important parameter to consider for all reversible logic designs. Applications with lower quantum cost value are likely to be more advantageous over the others. As research on reversible logic continues to advance, better tools and reversible gates are available to help achieving lower quantum cost value. Hence a reversible BCD adder design with low quantum cost value is proposed. The BCD adders are designed with the combination of the proposed reversible full adder circuit and other reversible gate such as Peres and TR gate to achieve best quantum cost value. Parallelism technique has been applied to keep propagation delay at minimal. Experimental results are shown that the proposed BCD adder designs have less quantum cost value than other existing designs.

#### **ACKNOWLEDGEMENT**

I would like to give thanks to God for providing me the opportunity to pursue my doctoral studies. Throughout the time He constantly reminds me to walk faithfully in His path. When I was weak, He constantly provides me with strength and wisdom to overcome any obstacle faced. Thank you for being there with me throughout my darkest time.

To my dear parents thank you for your unfailing love and kind understanding that make me feel blessed and proud to have them. Thank you for supporting me and being there with me always.

I would like to express my deepest gratitude to my supervisors Professor Ashutosh Kumar Singh, Dr Lenin Gopal and Dr Amandeep S. Sidhu for their valuable advices and guidance throughout the years of my research. Without their continuous support and guidance, I would not have gotten so far.

In addition, I would like to thank Curtin University Sarawak Campus for providing me with the scholarship and facilities. Without it, I would not have the opportunity to take up the doctoral program.

Last but not least, I would like to thank all my friends whom I met and share good moments together throughout the time. I would also like to thank my church especially members from Curtin Ministry (Aunty, Uncle and friends) for their great companion, encouragements, prayers and support. Thank you very much.

#### **PUBLICATIONS**

#### **Journal Papers**

- S. C. Chua and A. K. Singh, "Heuristic Synthesis of Reversible Logic-A Comparative Study," Advances in Electrical and Electronic Engineering, vol. 12, pp. 210-225, 2014.

- S. C. Chua and A. K. Singh, "Design of Quick Reversible Binary Coded Decimal (BCD) Adder," International Journal of Electronics, 2015. (Under review, ISI indexed)

- S. C. Chua and A. K. Singh, "Search-Based Reversible Logic Synthesis Using Mixed-Polarity Toffoli Gate," Turkish Journal of Electrical Engineering & Computer Sciences, 2015. (Under review, ISI indexed)

- 4. S. C. Chua and A. K. Singh, "Design of Efficient Reversible BCD Adder Circuits," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2015. (Under review, ISI indexed)

#### **Conference Papers**

- S. C. Chua, A. K. Singh, and L. Gopal, "Efficient Three Variables Reversible Logic Synthesis Using Mixed-polarity Toffoli Gate," Procedia Computer Science, vol. 70, pp. 362-368, 2015.

- S. C. Chua, L. Gopal, A. S. Sidhu, and A. K. Singh, "Design of Low Quantum Cost Reversible BCD Adder," in Proceedings of the 5th IEEE International Conference On Control System, Computing and Engineering (ICCSCE2015), Penang, Malaysia, 2015.

## TABLE OF CONTENT

| Abstra  | ct     |                                  | I    |

|---------|--------|----------------------------------|------|

| Acknov  | wled   | gement                           | IV   |

| Publica | tion   | s                                | V    |

| Table o | of Co  | ontent                           | VI   |

| List of | Figu   | res                              | X    |

| List of | Tabl   | les                              | XII  |

| Abbrev  | viatio | ons                              | XIII |

| Chapte  | r 1    | Introduction                     | 1    |

| 1.1     | The    | esis Objective                   | 3    |

| 1.2     | Pro    | blem Statement                   | 4    |

| 1.3     | The    | esis Contributions and Overview  | 4    |

| Chapte  | er 2   | Background                       | 8    |

| 2.1     | Re     | versible Function                | 8    |

| 2.2     | Re     | versible Circuit                 | 8    |

| 2.3     | Re     | versible Gates                   | 10   |

| 2.3     | 3.1    | The NOT Gate                     | 10   |

| 2.3     | 3.2    | The CNOT Gate                    | 11   |

| 2.3     | 3.3    | The Toffoli Gate                 | 11   |

| 2.3     | 3.4    | The Toffoli4 Gate                | 12   |

| 2.3     | 3.5    | The Mixed-Polarity Toffoli Gate  | 12   |

| 2.3     | 3.6    | The Mixed-Polarity Toffoli4 Gate | 14   |

| 2.3     | 3.7    | The SWAP Gate                    | 16   |

| 2.3     | 3.8    | The Fredkin Gate                 | 17   |

| 2.3     | 3.9    | The Peres Gate                   | 17   |

| 2.3     | 3.10   | The Inverse-Peres Gate           | 18   |

| 2.4     | De     | lay of Reversible Gates          | 19   |

| 2.5     | Re     | presentation Model               | 20   |

| 2.5     | 5.1    | Truth Table                      | 20   |

| 2.5     | 5.2    | Permutation Matrix               | 20   |

| 2.5     | 5.3    | Binary Decision Diagram          | 21   |

| 2.5     | 5.4    | Reed Muller Expansion            | 22   |

| Chapter         | · 3 | Literature Review                                             | . 23 |

|-----------------|-----|---------------------------------------------------------------|------|

| 3.1             | Rel | ated Work on Synthesis of Reversible Logic                    | . 23 |

| 3.1.            | 1   | Transformation Based Synthesis Algorithm                      | . 23 |

| 3.1.            | .2  | Rule Based Synthesis Algorithm                                | . 24 |

| 3.1.            | .3  | Cycle Based Synthesis Algorithm                               | . 25 |

| 3.1.            | 4   | Binary Decision Diagrams Based Synthesis                      | . 26 |

| 3.1.            | .5  | Search Based Synthesis Algorithm                              | . 27 |

| 3.1.            | .6  | Graph Based Synthesis Algorithm                               | . 28 |

| 3.1.            | .7  | Optimal Based Synthesis Algorithm                             | . 28 |

| 3.1.            | .8  | Summary                                                       | . 29 |

| 3.2             | Rel | ated Work on Reversible Full Adder Circuit                    | . 31 |

| 3.3             | Rel | ated Work on Reversible BCD Adder                             | . 33 |

| Chapter         |     | Search-Based Reversible Logic Synthesis using Mixed-Polarity  |      |

|                 |     | <u>.</u>                                                      |      |

| 4.1             |     | erview                                                        |      |

| 4.2             |     | nverting Logic Function into PPRM Expansion                   |      |

| 4.3             | •   | nthesis Algorithm                                             |      |

| 4.3.            |     | Gate Substitutions                                            |      |

| 4.3.            |     | Hamming Distance                                              |      |

| 4.3.            |     | Algorithm                                                     |      |

| 4.3.            |     | Example                                                       |      |

| 4.4             | •   | nthesis Result                                                |      |

| 4.4.            |     | Three-Variable Based Reversible Functions                     |      |

| 4.4.            | _   | Benchmark Functions                                           |      |

| 4.5             |     | apter Summary                                                 |      |

| Chapter Circuit | : 5 | The Proposed Reversible Gate and Its Application As Full Adde |      |

| 5.1             | Ove | erview                                                        |      |

| 5.2             | Pro | posed Reversible Gate                                         | . 55 |

| 5.3             |     | sign Methodology                                              |      |

| 5.4             |     | antum Realization Verification of the Reversible Chua Gate    |      |

| 5.5             | _   | mparison of Reversible Full Adder Circuit                     |      |

| 5.6             |     | apter Summary                                                 |      |

| Chapter         |     | Design of Minimal Delay Reversible BCD Adder                  |      |

| 6.1    | Ove | erview                                                            | . 63 |

|--------|-----|-------------------------------------------------------------------|------|

| 6.2    | ВС  | D Adder                                                           | . 64 |

| 6.2    | 2.1 | Basic                                                             | . 64 |

| 6.2    | 2.2 | Proposed BCD Adder Design with Carry Input                        | . 65 |

| 6.2    | 2.3 | Proposed BCD Adder Design with No Carry Input Required            | . 67 |

| 6.3    |     | sign Methodology of Reversible BCD Adder without using Mixed-     |      |

|        | •   | offoli Gate                                                       |      |

| 6.3    |     | Design 1 of Reversible BCD Adder with Carry Input                 |      |

| 6.3    |     | Design 1: Reversible BCD Adder with No Carry Input Required       | 74   |

| 6.4    |     | sign Methodology of Reversible BCD Adder with Mixed-Polarity  ate | 78   |

| 6.4    |     | Design 2 of Reversible BCD Adder with Carry Input                 |      |

| 6.4    |     | Design 2 of Reversible BCD Adder with No Carry Input Required     |      |

| 6.5    |     | aluation of the Proposed Designs                                  |      |

| 6.6    |     | nulation and Verification                                         |      |

| 6.7    |     | apter Summary                                                     |      |

| Chapte |     | Design of Low Quantum Cost Reversible BCD Adder                   |      |

| 7.1    |     | erview                                                            |      |

| 7.2    |     | sign of Reversible BCD Adder                                      |      |

| 7.3    |     | sign of Reversible BCD Adder with Carry Input                     |      |

| 7.3    |     | Proposed Reversible 4-Bit Binary Adder                            |      |

| 7.3    |     | Proposed Reversible Detection Circuit                             |      |

| 7.3    | 3.3 | Proposed 3-Bit Binary Adder                                       |      |

| 7.3    | 3.4 | Overall Circuit                                                   |      |

| 7.4    | Des | sign of Reversible BCD Adder with No Carry Input                  | 96   |

| 7.4    | l.1 | Proposed Reversible 4-Bit Binary Adder                            | 97   |

| 7.4    | 1.2 | Overall Circuit                                                   | 97   |

| 7.5    | Opt | timization in Terms of Propagation Delay                          | 98   |

| 7.5    | 5.1 | QC-BCD1 Optimized in Terms of Propagation Delay                   | 98   |

| 7.5    | 5.2 | QC-BCD2 Optimized In Terms of Propagation Delay                   | 100  |

| 7.6    | Eva | aluation of the Proposed Designs                                  | 101  |

| 7.7    | Sin | nulation and Verification                                         | 102  |

| 7.8    | Cha | apter Summary                                                     | 103  |

| Chapte | r 8 | Conclusion And Future Work                                        | 104  |

| References             | 10- |

|------------------------|-----|

| 8.2 Future Works       |     |

| 8.1 Concluding Remarks |     |

## LIST OF FIGURES

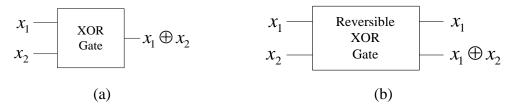

| Figure 1.1. (a) Conventional XOR gate (b) Reversible XOR gate                         | 2    |

|---------------------------------------------------------------------------------------|------|

| Figure 2.1. NOT gate                                                                  | . 10 |

| Figure 2.2. CNOT gate                                                                 | . 11 |

| Figure 2.3. (a) Toffoli gate symbol (b) Quantum realization of the Toffoli gate       | . 11 |

| Figure 2.4. (a) Toffoli4 gate symbol (b) Quantum realization of the Toffoli4 gate     | . 12 |

| Figure 2.5. (a) Mixed-polarity Toffoli gate symbol with first bit as negative bit (b) | 1    |

| Quantum realization of the mixed-polarity Toffoli gate with first bit as negative bi  | t13  |

| Figure 2.6. (a) Mixed-polarity Toffoli gate symbol with second bit as negative bit    | (b)  |

| Quantum realization of the mixed-polarity Toffoli gate with second bit as negative    | •    |

| bit                                                                                   | . 13 |

| Figure 2.7. (a) Mixed-polarity Toffoli gate symbol with two negative bits (b)         |      |

| Quantum realization of the mixed-polarity Toffoli gate with two negative bits         | . 14 |

| Figure 2.8. (a) Mixed-polarity Toffoli4 gate symbol with one negative bit (b)         |      |

| Quantum realization of the mixed-polarity Toffoli4 with one negative bit              | . 15 |

| Figure 2.9. (a) Mixed-polarity Toffoli4 gate symbol with two negative bits (b)        |      |

| Quantum realization of the mixed-polarity Toffoli4 with two negative bits             | . 15 |

| Figure 2.10. (a) Mixed-polarity Toffoli4 gate symbol with three negative bits (b)     |      |

| Quantum realization of the mixed-polarity Toffoli4 with three negative bits           | . 16 |

| Figure 2.11. (a) SWAP gate symbol (b) Quantum realization of the SWAP gate            | . 16 |

| Figure 2.12. (a) Fredkin gate symbol (b) Quantum realization of the Fredkin gate      | . 17 |

| Figure 2.13. Toffoli gate with CNOT gate connected to both its control line           | . 18 |

| Figure 2.14. (a) Peres gate symbol (b) Quantum realization of the Peres gate          | . 18 |

| Figure 2.15. (a) TR gate symbol (b) Quantum realization of the TR gate                | . 19 |

| Figure 2.16. Reversible circuit                                                       | . 20 |

| Figure 2.17. BDD for Boolean function $x3 + x1x2$                                     | . 22 |

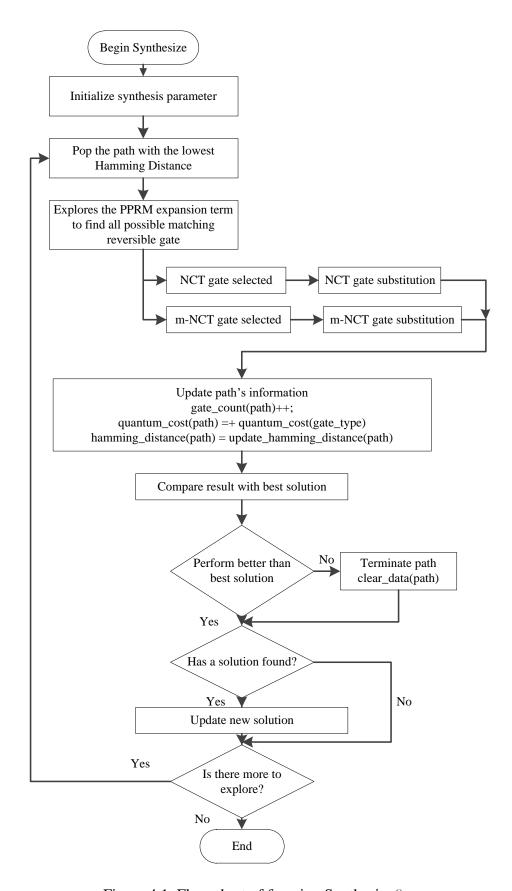

| Figure 4.1. Flow chart of function Synthesize()                                       |      |

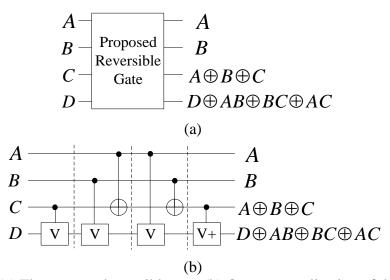

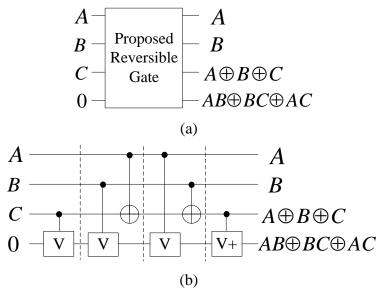

| Figure 5.1. (a) The proposed revesible gate (b) Quantum realization of the propose    | ed   |

| revesible gate                                                                        |      |

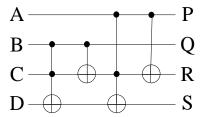

| Figure 5.2. Realized reversible full adder                                            |      |

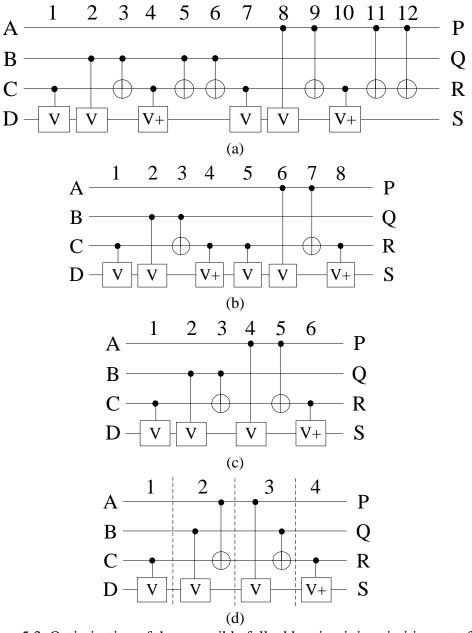

| Figure 5.3. Optimization of the reversible full adder circuit in primitive gate form  |      |

| Figure 5.4. Verification of output P, Q, R                                            | . 60 |

| Figure 5.5. (a) The propsed reversible gate as reversible full adder circuit (b)      |      |

| Quantum realization of the propsed reversible gate as reversible full adder circuit.  |      |

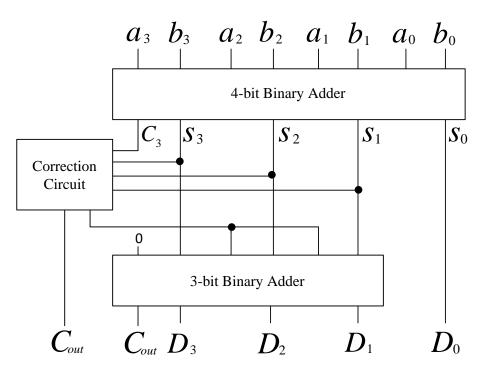

| Figure 6.1. BCD Adder Circuit                                                         |      |

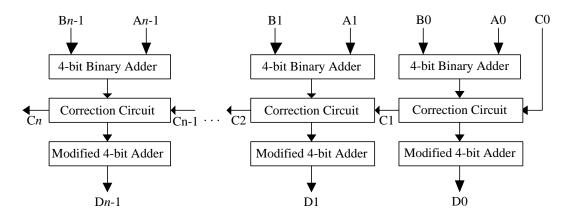

| Figure 6.2. Proposed Reversible BCD Adder with Carry Input                            | . 66 |

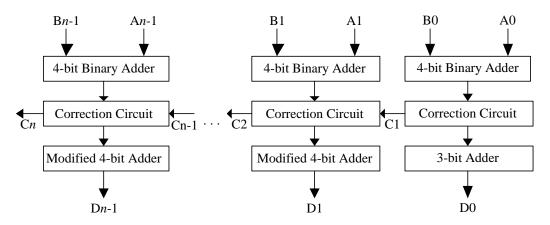

| Figure 6.3. Proposed Reversible <i>n</i> Digit BCD Adder with Carry Input             |      |

| Figure 6.4. Proposed Reversible BCD Adder with No Carry Input                         |      |

| Figure 6.5. Proposed Reversible <i>n</i> Digit BCD Adder with No Carry Input          |      |

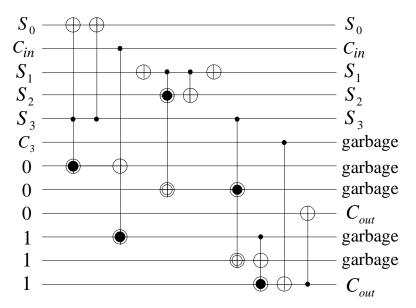

| Figure 6.6. Proposed Reversible 4-Bit Binary Adder                                    |      |

| Figure 6.7. Proposed Reversible Correction Circuit                                    | .71  |

| Figure 6.8. Proposed Reversible Modified 4-Bit Binary Adder                     | 71 |

|---------------------------------------------------------------------------------|----|

| Figure 6.9. Proposed Reversible BCD Adder with Carry Input (C-BCD1)             | 72 |

| Figure 6.10. Propagation Delay Optimized for C-BCD1                             | 74 |

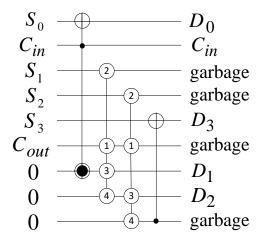

| Figure 6.11. Proposed Reversible Correction Circuit                             | 75 |

| Figure 6.12. Proposed Reversible 3-Bit Binary Adder                             | 75 |

| Figure 6.13. Proposed Reversible BCD Adder with No Carry Input Required (NC-    |    |

| BCD1)                                                                           | 76 |

| Figure 6.14. Propagation Delay Optimized for NC-BCD1                            | 78 |

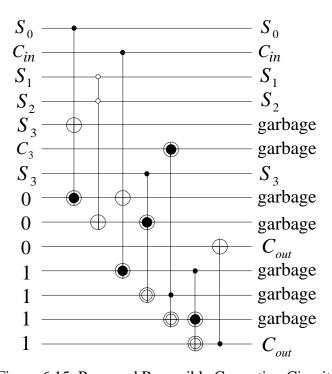

| Figure 6.15. Proposed Reversible Correction Circuit                             | 79 |

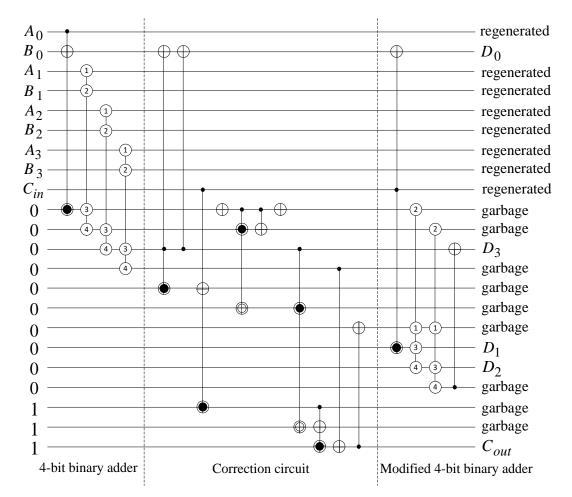

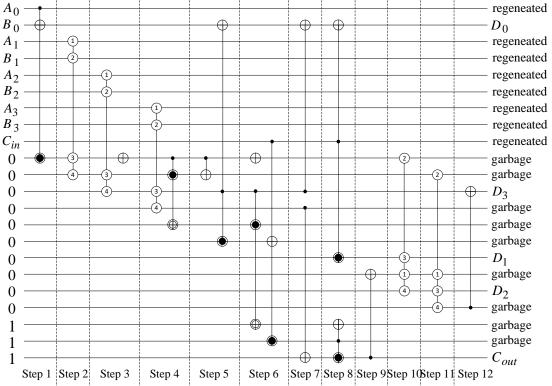

| Figure 6.16. Proposed Reversible BCD Adder with Carry Input (C-BCD2)            | 80 |

| Figure 6.17. Propagation Delay Optimized for C-BCD2                             | 82 |

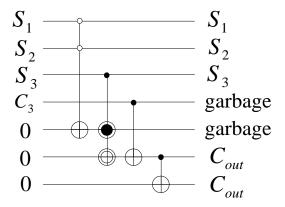

| Figure 6.18. Proposed Reversible Correction Circuit                             | 83 |

| Figure 6.19. Proposed Reversible BCD Adder with No Carry Input Required (NC-    |    |

| BCD2)                                                                           | 84 |

| Figure 6.20. Propagation Delay Optimized for NC-BCD2                            | 85 |

| Figure 6.21. Simulation flow of the proposed reversible BCD adder designs using |    |

| VHDL                                                                            | 90 |

| Figure 6.22. Test bench waveform verification                                   | 90 |

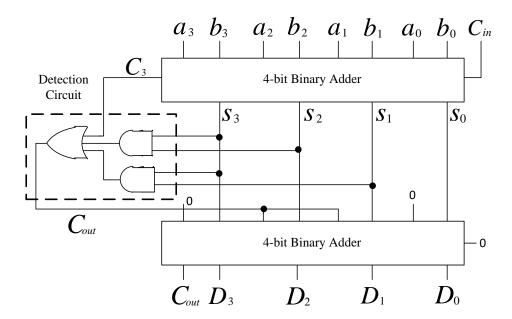

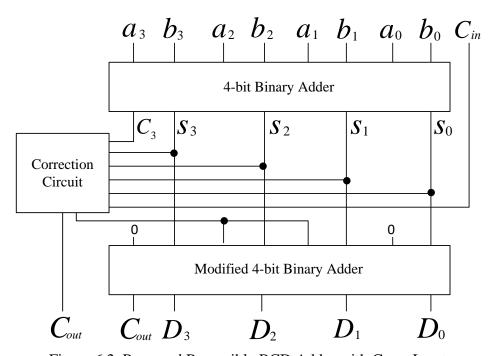

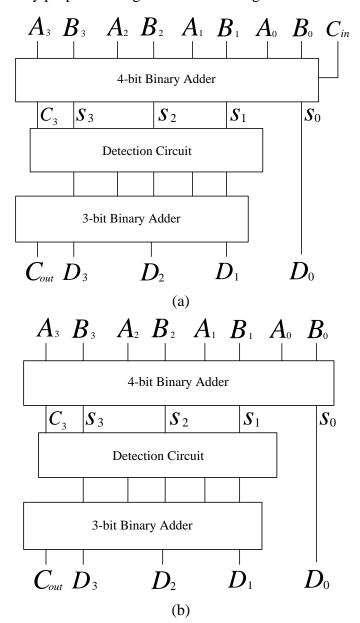

| Figure 7.1. (a) Proposed reversible BCD adder design with Cout (b) Proposed     |    |

| reversbile BCD adder design without Cout                                        | 93 |

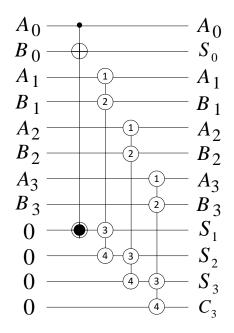

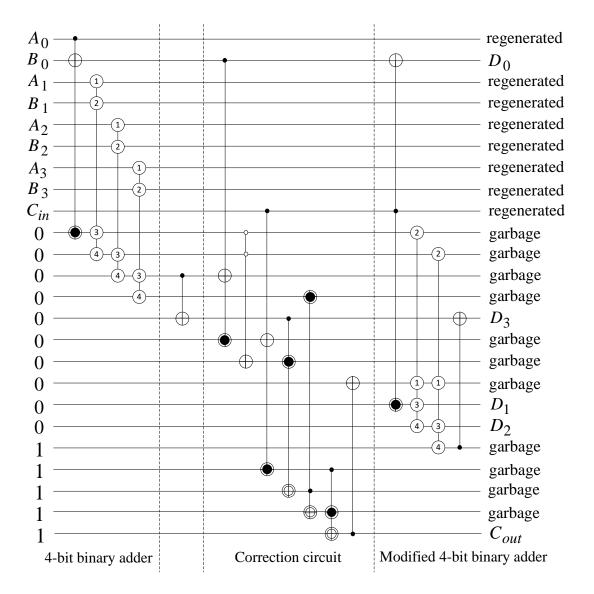

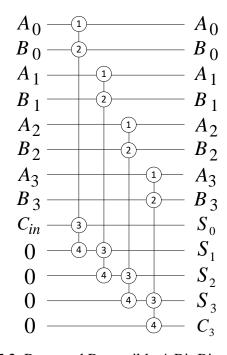

| Figure 7.2. Proposed Reversible 4-Bit Binary Adder                              | 94 |

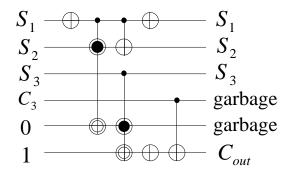

| Figure 7.3. Proposed Reversible Detection Circuit                               | 95 |

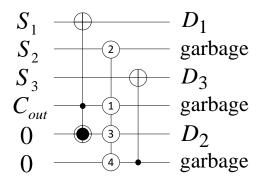

| Figure 7.4. Proposed Reversible 3-Bit Binary Adder                              | 95 |

| Figure 7.5. Proposed Reversible BCD Adder with Carry Input (QC-BCD1)            | 96 |

| Figure 7.6. Proposed Reversible 4-Bit Binary Adder                              | 97 |

| Figure 7.7. Proposed Reversible BCD Adder with No Carry Input (QC-BCD2)         | 98 |

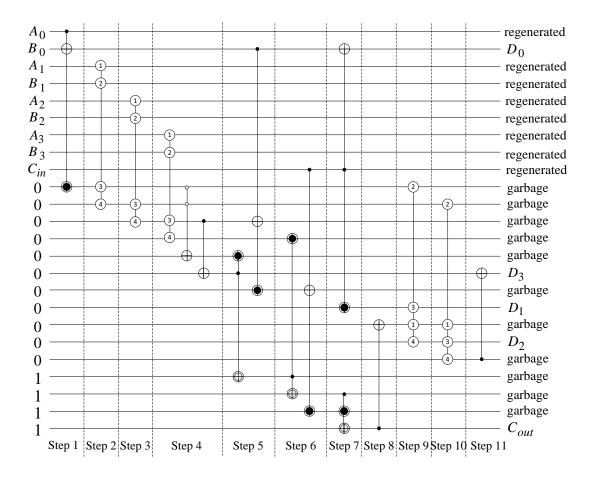

| Figure 7.8. Propagation Delay Optimized for QC-BCD1                             | 99 |

| Figure 7.9. Propagation Delay Optimized for QC-BCD21                            | 01 |

# LIST OF TABLES

| Table 1-1. (a) Truth table for conventional XOR gate (b) Truth table for reversible |      |

|-------------------------------------------------------------------------------------|------|

| XOR gate                                                                            | 2    |

| Table 2-1. Reversible function                                                      | 8    |

| Table 2-2. Half-adder function                                                      |      |

| Table 2-3. Possible reversible half-adder function                                  | 9    |

| Table 2-4. Propagation delay of reversible gate                                     | . 19 |

| Table 2-5. Truth table representation                                               |      |

| Table 2-6. CNOT gate truth table                                                    | . 21 |

| Table 3-1. Comparison table of all discussed synthesis methods                      | . 30 |

| Table 4-1. Benchmark function 3_17 written in PPRM expansion                        | . 43 |

| Table 4-2. After first gate substitution                                            | . 44 |

| Table 4-3. After second gate substitution                                           | . 44 |

| Table 4-4. After third gate substitution                                            | . 45 |

| Table 4-5. After fourth gate substitution                                           | . 45 |

| Table 4-6. After fifth gate substitution.                                           | . 45 |

| Table 4-7. Gate count for all three variable based reversible functions             | . 47 |

| Table 4-8. Gate count and quantum cost comparison                                   | . 48 |

| Table 4-9. Quantum cost result for all three variable based reversible functions    | . 49 |

| Table 4-10. Synthesis result of reversible benchmark functions of size 3            | . 50 |

| Table 4-11. Synthesis result of reversible benchmark functions of size 4            | . 50 |

| Table 4-12. Synthesis result of reversible benchmark functions of size 5            | . 53 |

| Table 4-13. Synthesis result of reversible benchmark functions of size 6 or greater | 54   |

| Table 5-1. Truth table of the proposed reversible gate                              | . 56 |

| Table 5-2. Full adder function                                                      | . 57 |

| Table 5-3. Truth table of the proposed reversible full adder                        |      |

| Table 5-4. Truth table of output S                                                  | . 61 |

| Table 5-5. Comparison of different reversible full adder circuit designs            | . 62 |

| Table 6-1. Comparison of <i>n</i> Digit Reversible BCD Adders                       | . 87 |

| Table 6-2. Propagation Delay Comparison of n Digits Reversible BCD Adders using     | ng   |

| Proposed Design 1                                                                   | . 88 |

| Table 6-3. Propagation Delay Comparison of n Digits Reversible BCD Adders using     | ng   |

| Proposed Design 2                                                                   | . 88 |

| Table 6-4. Propagation Delay Comparison of n Digits Reversible BCD Adders using     | ng   |

| Proposed Design 3                                                                   | . 88 |

| Table 6-5. Propagation Delay Comparison of n Digits Reversible BCD Adders using     | ng   |

| Proposed Design 4                                                                   | . 89 |

| Table 7-1. Comparison of <i>n</i> digit reversible BCD Adders                       | 102  |

#### **ABBREVIATIONS**

BCD Binary Coded Decimal

BDD Binary Decision Diagram

CNOT Controlled-NOT

DD Decision Diagram

ESOP Exclusive OR sum-of-product

FA Full Adder

GC Gate count

HA Half Adder

HD Hamming Distance

MMD Miller-Maslov-Miller

m-NCT Mixed polarity NOT, CNOT, Toffoli based gate

NCT NOT, CNOT, Toffoli based gate

NCTP NOT, CNOT, Toffoli, Peres, inverse-Peres based gate

NCTSF NOT, CNOT, Toffoli, SWAP, Fredkin based gate

PPRM Positive Polarity Reed-Muller

QC Quantum cost

RM Reed-Muller

VHDL Very High Speed Integrated Circuit Hardware Description Language

XOR Exclusive OR

#### CHAPTER 1 INTRODUCTION

Energy lost during computation is an important issue addressed in every low power digital design. According to Landauer [1], every bit of information is lost each time a logic gate performs a logic operation[1]. This information lost is converted into a form of heat and it is around

$$kTln(2)$$

Joule (1.1)

Where k is the Boltzmann constant and T is the absolute temperature [1]. At room temperature, the heat generated is not significant, but still it cannot be neglected [2]. Today, the amount of information loss in the form of heat to the surrounding environment of a chip leads to immense challenges in circuit design [3]. As Moore's law predicts the exponential growth of transistor in an integrated system, the heat generated due to the irreversible system used will be noticeable as more transistors are implemented in a die [4, 5]. However according to Bennett [6], it has been shown that the finite amount of energy loss can be avoided in a fully reversible logic implementation because information lost does not occur in the operation of reversible logic.

Reversible logic is specially designed logic gate which utilize quantum logic theories in realizing its logic operation [7]. Since information in reversible logic is fully permutable from its inputs to outputs and vice versa, it achieves lossless information during this transition. Thus this makes reversible logic essential in the future of circuit design. One of the most interesting applications of reversible logic is in the application of quantum computing [8]. A quantum computer is known to be able to solve exponentially hard problems in polynomial time [8-10]. Quantum computer can be viewed as a quantum network composed of quantum logic gates in which each quantum logic gate performs an elementary unitary operation called qubits [11-13]. All unitary operations are reversible and hence quantum networks must be built using reversible logical components [14]. Thus the research on reversible logic is beneficial to the development of future quantum technologies.

Quantum technologies are not the only sectors that will benefit from reversible logic. There are other technologies where reversible logic can be applied such as in adiabatic CMOS design [15, 16], optical computing [17-19], nanotechnology [20-23],

etc. Further discussion on these different technologies will not be addressed in this dissertation because each of them involves a vast amount of expertise. However, the irreversible logic implementation is common between these technologies.

The existing logic gate used in digital designs such as the AND gate, OR gate, XOR gate, etc. are irreversible. In order for a circuit to be reversible, there has to be a unique one-to-one mapping between the inputs and outputs [24]. Consider an example of a common XOR gate shown in Figure 1.1 (a), it is obvious that the logic gate is not reversible because there is no unique one-to-one mapping between the inputs and outputs. This is because for the input argument 00 and 11 it give rise to the output 0 while input argument 01 and 10 give rise to the output 1 as seen in Table 1-1 (a). Figure 1.1 (b) shows a reversible XOR gate which has a unique one-to-one mapping between the inputs and outputs such that each of its output vector is assigned to a unique input argument as shown in Table 1-1 (b).

Figure 1.1. (a) Conventional XOR gate (b) Reversible XOR gate

Table 1-1. (a) Truth table for conventional XOR gate (b) Truth table for reversible XOR gate

|   | Input $x_1, x_2$ | Output |

|---|------------------|--------|

|   | $x_{1}, x_{2}$   | у      |

| 0 | 0 0              | 0      |

| 1 | 0 1              | 1      |

| 2 | 1 0              | 1      |

| 3 | 1 1              | 0      |

(a)

|   | Input          | Output     |

|---|----------------|------------|

|   | $x_{1}, x_{2}$ | $y_1, y_2$ |

| 0 | 0 0            | 0 0        |

| 1 | 0 1            | 0 1        |

| 2 | 1 0            | 1 1        |

| 3 | 1 1            | 1 0        |

(b)

After the discovery of powerful quantum algorithms in the mid-1990s, research on reversible logic synthesis has begun to attract attention [7]. The research on reversible logic is expanding towards two different directions which are design and synthesis. Over these years, lot of interesting synthesis algorithm has been proposed. The earlier proposed synthesis algorithms synthesize reversible function into a set of

NCT based gate library which consist only of NOT, CNOT and Toffoli gates [25-27]. Over the years, other reversible gates such as SWAP, Fredkin, Peres and inverse-Peres gates have also been used in several synthesis algorithms [28-30]. However, most synthesis algorithms prefer to use the original NCT gate library with extended Toffoli size such as using Toffoli4, Toffoli5 or higher Toffoli size to cope with larger functions. Toffoli gate has been explored and extended and recently researchers have started to integrate Toffoli gate with positive and negative control lines into its operation [31, 32]. This type of Toffoli gate with positive and negative polarity control capability is known as the mixed-polarity Toffoli gate. Usage of this gate for reversible logic synthesis has been extensively studied in a number of works such as in [33-36] and had been proven that it provides better synthesis results. Although various research works using this gate have been proposed, still there is room for improvement. Besides, the usage of this gate for designing reversible arithmetic unit, reversible Binary Coded Decimal (BCD) adder has not yet been reported in any literature work. Thus this leads to the contribution of this research.

#### 1.1 Thesis Objective

The aim of this research is to propose efficient methods for design and synthesis of reversible circuits using reversible gates. The key objectives of the research are to:

- Develop new reversible logic synthesis algorithm in terms of gate count and quantum cost using a set of benchmarking circuit.

- Investigate much efficient reversible gates and use it to design new reversible logic arithmetic applications.

- Optimize the performance of the proposed reversible adder circuits in terms of propagation delay.

- Address the usage of mixed-polarity Toffoli gate for designing reversible logic synthesis algorithm and reversible BCD adders.

#### 1.2 Problem Statement

Although the research of reversible logic has achieved major breakthrough in design and synthesis, but various problems still exist and solution remains elusive. The biggest challenges face in the synthesis of reversible logic is that the existing synthesis algorithm is not able to full balance the gate count and quantum cost to achieve optimal solution for all synthesized reversible function. Recently with the new quantum realization of the mixed-polarity Toffoli gate, synthesis algorithm is able to achieve one step further in scaling reversible function better and achieves close optimal result. Although several research works using this gate has been proposed, but further research can still be done to improve existing algorithms. For the research in designing reversible logic based arithmetic application, research attention has always been focused only on quantum cost, ancilla input and garbage output. Parameter such as propagation delay which is crucial in achieving fast executing time which is often neglected. As fast arithmetic is crucial it should not be neglected in any high speed arithmetic design. Thus these issues are addressed towards the finding of this research.

#### 1.3 Thesis Contributions and Overview

In the design and synthesis of reversible logic, there are a few important points that need to be kept in mind. To further understand the efficiency of reversible logic synthesis algorithm, gate count which denotes the amount of reversible gate required to realize a reversible function and quantum cost which denotes the effort to represent the gate function in quantum realization are the most significant parameters. The efficiency of a synthesis algorithm is determined by these two parameters tested out by synthesizing all three variables based reversible functions and reversible benchmark functions [37-39].

For designing reversible logic circuit based applications, the important parameters to be considered are the ancilla inputs (constant logic input), garbage outputs (unused outputs), quantum cost and propagation delay. These parameters are required to keep at possible minimal. Keeping all parameter at lowest is not possible, because optimizing one parameter may often result in the degradation of other important

parameters. Hence while designing and synthesizing the reversible logic circuits, some parameters should be considered to achieve optimal value with expenses of other parameters.

In this dissertation, the research contributions toward the design and synthesis of reversible logic are as follows:

- The first contribution of this dissertation is the design of a search-based reversible logic synthesis algorithm. The proposed synthesis algorithm synthesizes reversible function into reversible circuits using positive and negative control Toffoli gates. Based on the recent literature work, it can be concluded that this is the first attempt in the reversible logic circuit design to integrate Toffoli gate with mixed polarity control capability into search-based synthesis algorithm. It has the capability to allow the algorithm to synthesize reversible function in term of quantum cost which is a challenging task that most synthesis algorithms are incapable of.

- The second contribution of this dissertation is the design of a novel reversible gate. The proposed reversible gate is designed mainly to serve as a reversible full adder circuit and is proven to be efficient in terms of ancilla input, garbage output, quantum cost and delay. It can be notified that, the proposed reversible full adder circuit implementation does not use any garbage output. Ancilla input, quantum cost and delay of the proposed design are maintained equally as compared to other existing designs.

- The third contribution of this dissertation is the design of minimal delay reversible BCD adders. In the proposed reversible BCD adder design, the delay introduced between the carry input  $C_{in}$  and carry output  $C_{out}$  is reduced; hence the next BCD digit is generated faster. In the BCD adder design, parallelism technique is used to achieve the fast BCD sum.

- The last contribution of this dissertation is the design two quantum cost optimized reversible BCD adders. The proposed design uses a variety of reversible gate such as the earlier proposed reversible full adder circuit, Peres gate and TR gate in building the designs. In addition, parallelism technique has been implemented to reduce the overall delay.

The remainder of this dissertation is organized as follows:

- In Chapter 2, preliminaries on reversible logic are being discussed. It covers

reversible functions and circuits, types of reversible gates and reversible function

representation model. All the important parameters are explained in details to

keep the chapter self-contained.

- In Chapter 3, existing literature work on synthesis of reversible logic, reversible full adder circuit and also reversible BCD adder circuit are being reviewed and discussed. Each of the topics is discussed in a new sub-section to keep the flow in order.

- In Chapter 4, a search-based reversible logic synthesis algorithm using mixed-polarity Toffoli gate has been presented. Search-based reversible logic synthesis algorithm is proven to be able to synthesize any reversible function into reversible circuit. However existing search-based synthesis algorithm are only limited to positive Toffoli gate family. In the proposed algorithm, search-based synthesis technique is integrated with mixed-polarity Toffoli gate. It can be notified that this is the first attempt to use mixed-polarity Toffoli gate for search-based reversible logic synthesis algorithm. Synthesis results are shown that the proposed synthesis algorithm is able to produce result close to the optimal solution.

- In Chapter 5, a new reversible gate is proposed which is capable of realizing the

reversible full adder circuit functions efficiently as compared to the existing

reversible gates. It can be noted that this is the first attempt in literature for a

reversible full adder circuit realization that does not use any garbage output.

- In Chapter 6, a new class of design of reversible BCD adder is proposed with uses of parallelism technique to archive fast BCD sum. In this Chapter, two reversible BCD adder designs are presented such as reversible BCD adder without Carry Input and reversible BCD adder with Carry Input. In each of the proposed design, two reversible logic implementations are presented such as one with using mixed-polarity Toffoli gate and another one without it. The proposed designs are primarily optimized for propagation delay to achieve fast BCD sum. Other important parameters such as the ancilla inputs, garbage outputs and quantum cost are designed at best possible lowest values.

- In Chapter 7, two reversible logic implementations of BCD adder designs are optimized in terms of quantum cost. Quantum cost has always been the most

important parameter to consider for all reversible logic design and synthesis. Other important parameters such as ancilla input, garbage output and propagation delay are not neglected and is kept at best possible lowest value.

In Chapter 8, conclusions of the research findings are drawn and possible future works and interesting research ideas are outlined to improve or extend the current research works.

#### CHAPTER 2 BACKGROUND

To keep the dissertation self-contained, basic preliminaries on reversible logic are discussed in this chapter. Section 2.1 and Section 2.2 discuss about the fundamental theories on reversible logic such as reversible function, reversible circuit, ancilla input and garbage output. Section 2.3 provides a detailed explanation on reversible gates and addressed all reversible gates used in this dissertation. Delays on reversible gates are discussed in Section 2.4 and function representation model of reversible logic is discussed in Section 2.5.

#### 2.1 Reversible Function

A logic function  $f(x_1, x_2, x_3, ..., x_n)$  of n Boolean variables is reversible if it has a mapping of all its input assignment to a unique output assignment [40].

**Example:** Table 2-1 illustrates an example of a three variables reversible function. The function f = (1, 3, 5, 7, 6, 2, 0, 4) is permuted over  $\{0, 1, 2, 3, 4, 5, 6, 7\}$  where there exist a one-to-one relationship between the inputs and outputs, such that f(0) = 1, f(1) = 3, f(2) = 5, f(3) = 7, f(4) = 6, f(5) = 2, f(6) = 0, f(7) = 4. The function is reversible because each of the output is assigned to a unique input with no repeating.

Table 2-1. Reversible function

|   | Input A, B, C | Output P, Q, R | Permutation Function F |

|---|---------------|----------------|------------------------|

| 0 | 0 0 0         | 0 0 1          | 1                      |

| 1 | 0 0 1         | 0 1 1          | 3                      |

| 2 | 010           | 101            | 5                      |

| 3 | 0 1 1         | 111            | 7                      |

| 4 | 100           | 110            | 6                      |

| 5 | 101           | 010            | 2                      |

| 6 | 110           | 0 0 0          | 0                      |

| 7 | 1 1 1         | 100            | 4                      |

#### 2.2 Reversible Circuit

A well-formed reversible circuit is an acyclic combinational logic circuit in which all gates constructed within it are reversible [41]. The usage of fan-out which connects

the output of a gate to multiple inputs and looping which connects the output of a gate directly to its input is not allowed in reversible logic [42, 43]. An irreversible function can be converted into a reversible function by adding extra lines to create a one-to-one mapping between the inputs and outputs. Those added extra lines on the input side are known as the ancilla input and are supplied with constant logic value 0 or 1 [44, 45]. The lines at the output side which is neither a useful output nor a regenerated output are known as the garbage output [46, 47]. In a reversible circuit design, ancilla input and garbage output are essential components that help to keep the circuit reversible [43].

**Example:** To demonstrate the process of converting an irreversible function into a reversible function, logic function of a half-adder is considered in this example. Table 2-2 illustrates the function of a half-adder, where A and B are the inputs to be summed and S is the sum and C is the carry. The function is not reversible as the function contains repeated output vectors (mark with a \* sign). In order for the function to be reversible, an extra line is added to create the unique one-to-one mapping between the inputs and outputs. Table 2-3 illustrates the function after extra line has been added (Input D is an ancilla input of constant value 1 and output G is the garbage output). Now the function is reversible as it has a clear one-to-one mapping between the inputs and outputs.

Table 2-2. Half-adder function

| Input      | Output |   |

|------------|--------|---|

| Input A, B | C,S    |   |

| 0.0        | 0 0    |   |

| 0 1        | 0 1    | * |

| 1 0        | 0 1    | * |

| 1 1        | 1 1    |   |

Table 2-3. Possible reversible half-adder function

| Input   | Output |

|---------|--------|

| D, A, B | G,C,S  |

| 100     | 100    |

| 101     | 0 0 1  |

| 110     | 1 0 1  |

| 111     | 1 1 1  |

#### 2.3 Reversible Gates

A reversible gate realizes a reversible function and has equal amount of input and outputs which form a unique one-to-one mapping between the inputs and outputs. If a reversible gate has k inputs and outputs, it is called a k bits gate or a gate with k lines. All reversible gates are associated with a cost called quantum cost which denotes the effort required to realize the function of the gate [31]. Quantum cost of a reversible gate is measured by the number of elementary quantum gates required to realize the function [48]. The elementary quantum gates generally consist of the NOT gate, the CNOT gate, the Controlled-V, Controlled-V+, Controlled-W and Controlled-W+ gates which are the basic building block of any reversible gate [48-50]. All elementary quantum gates have a quantum cost of 1 [48, 51].

In the sub-sections below, the commonly used reversible gates are discussed in the research field. Few well known reversible gates form the basic NCT gate library such as the NOT, CNOT, Toffoli and Toffoli4 gates. The NCT gate library with positive and negative polarity control line such as mixed-polarity Toffoli and mixed-polarity Toffoli4 gates form the m-NCT gate library when combine together with the NCT gate library. There are other commonly used reversible gate such as the SWAP gate with Fredkin gate and also the Peres gate with inverse-Peres which forms the NCTSF and NCTP gates family respectively.

#### 2.3.1 The NOT Gate

The NOT gate is a one bit reversible gate, it has a quantum cost of 1 [52]. The gate maps a Boolean pattern  $x_1$  to  $\overline{x_1}$ . Figure 2.1 shows the accepted symbol of the gate with its function.

Figure 2.1. NOT gate

#### 2.3.2 The CNOT Gate

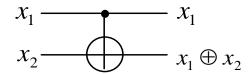

The CNOT gate or the Feynman gate is a two bit reversible gate, it has a quantum cost of 1 [53]. The gate maps a Boolean pattern  $(x_1, x_2)$  to  $(x_1, x_1 \oplus x_2)$ . Figure 2.2 shows the accepted symbol of the gate with its function [52].

Figure 2.2. CNOT gate

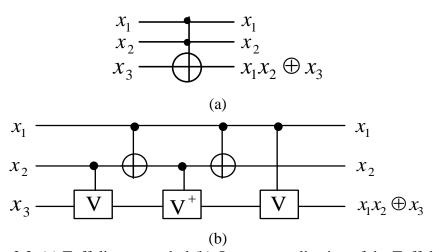

#### 2.3.3 The Toffoli Gate

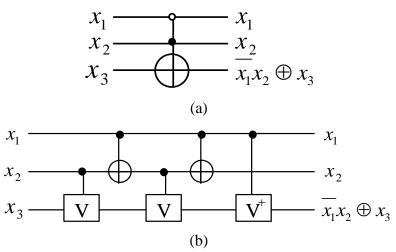

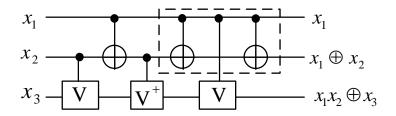

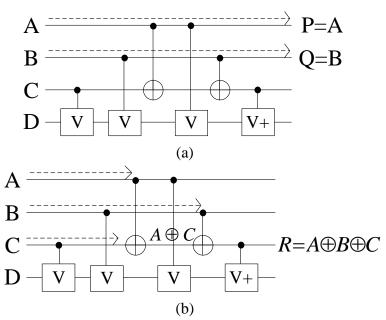

The Toffoli gate is a three bit reversible gate, it has a quantum cost of 5 [52, 53]. The gate maps a Boolean pattern  $(x_1, x_2, x_3)$  to  $(x_1, x_2, x_1x_2 \oplus x_3)$ . Figure 2.3 (a) shows accepted symbol with its function and Figure 2.3 (b) shows the quantum realization of the Toffoli gate [51], where V and  $V^+$  are unitary matrices known as the Controlled-V and Controlled-V+ gate [7, 31]. Where  $V = \frac{1+i}{2} \begin{bmatrix} 1 & -i \\ -i & 1 \end{bmatrix}$  and  $V^+ = \frac{1-i}{2} \begin{bmatrix} 1 & i \\ i & 1 \end{bmatrix}$ , and  $V^2 = (V^+)^2 = NOT$  and  $V^+$  represents the adjoint of V, so  $V \times V^+ = V^+ \times V = I$  [7, 31, 48].

Figure 2.3. (a) Toffoli gate symbol (b) Quantum realization of the Toffoli gate

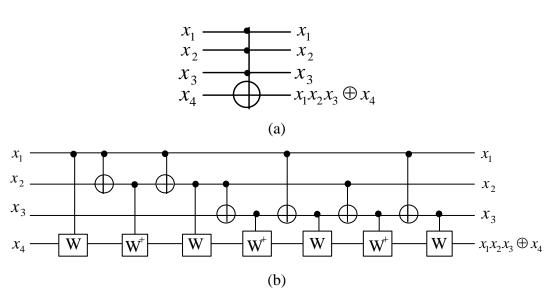

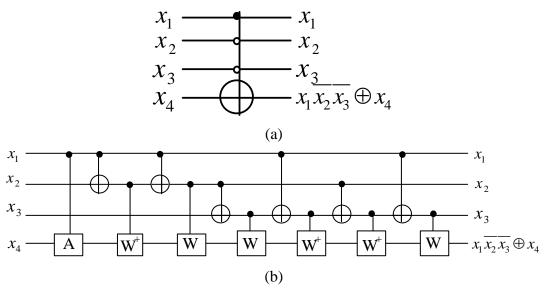

#### 2.3.4 The Toffoli4 Gate

The Toffoli4 gate [53] is a four bit reversible gate, it has a quantum cost of 13 [52]. The gate maps a Boolean pattern  $(x_1, x_2, x_3, x_4)$  to  $(x_1, x_2, x_3, x_1x_2x_3 \oplus x_4)$ . Figure 2.4 (a) shows the accepted symbol for Toffoli4 and Figure 2.4 (b) shows the quantum realization disclosed within, where W and  $W^+$  are unitary matrices known as the Controlled-W and Controlled-W+ gate [31, 50]. Where  $W = \frac{1}{2} \begin{bmatrix} 1 + \sqrt{i} & 1 - \sqrt{i} \\ 1 - \sqrt{i} & 1 + \sqrt{i} \end{bmatrix}$  and  $W^+ = \frac{1}{2} \begin{bmatrix} 1 - i\sqrt{i} & 1 + i\sqrt{i} \\ 1 + i\sqrt{i} & 1 - i\sqrt{i} \end{bmatrix}$ , and such that  $W^4 = (W^+)^4 = NOT$  and  $W \times W^+ = W^+ \times W = I$  [31, 50].

Figure 2.4. (a) Toffoli4 gate symbol (b) Quantum realization of the Toffoli4 gate

#### 2.3.5 The Mixed-Polarity Toffoli Gate

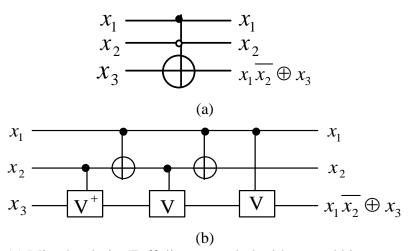

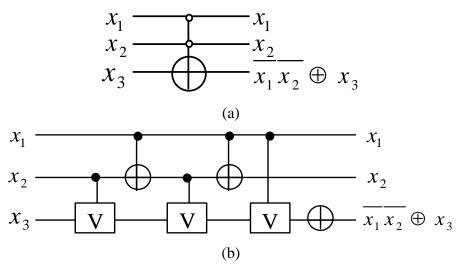

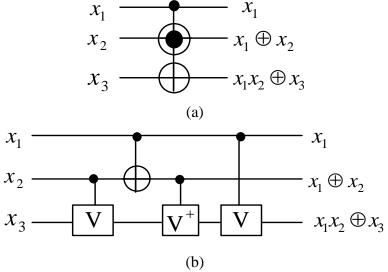

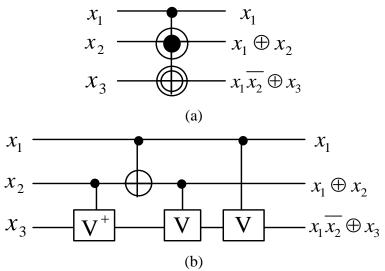

The mixed-polarity Toffoli gate is a three bit reversible gate. For mixed-polarity Toffoli gate with one negative bit, it has a quantum cost of 5 [32, 51]. For mixed-polarity Toffoli gate with two negative bits, it has a quantum cost of 6 [54]. The gate maps the Boolean pattern  $(x_1, x_2, x_3)$  to  $(x_1, x_2, (a_1 \oplus x_1)(a_2 \oplus x_2) \oplus x_3)$ , where  $a_1, a_2$  are coefficients that tells which line is a negative polarity control line. If  $a_x = 1$ , this means that line x is a negative polarity control line. Depending on which input bit to be a negative bit, the mixed-polarity Toffoli gate will result in three combinations. Figure 2.5 (a), Figure 2.6 (a) and Figure 2.7 (a) shows the accepted symbol of these gates with their corresponding function. Figure 2.5 (b), Figure 2.6 (b)

and Figure 2.7 (b) shows the quantum realization disclosed [32, 51, 54]. From the Barenco-type realizations seen in the mixed-polarity Toffoli gates and the Toffoli gate, the positive and negative control signal are formed through different in connection of the V or  $V^+$  elementary gate realizing it [31]. Since pin order of the gate is not considered for theoretical based simulation, the two mixed-polarity Toffoli gates in Figure 2.5 and Figure 2.6 are considered as the same gate.

Figure 2.5. (a) Mixed-polarity Toffoli gate symbol with first bit as negative bit (b) Quantum realization of the mixed-polarity Toffoli gate with first bit as negative bit

Figure 2.6. (a) Mixed-polarity Toffoli gate symbol with second bit as negative bit (b) Quantum realization of the mixed-polarity Toffoli gate with second bit as negative

bit

Figure 2.7. (a) Mixed-polarity Toffoli gate symbol with two negative bits (b) Quantum realization of the mixed-polarity Toffoli gate with two negative bits

#### 2.3.6 The Mixed-Polarity Toffoli4 Gate

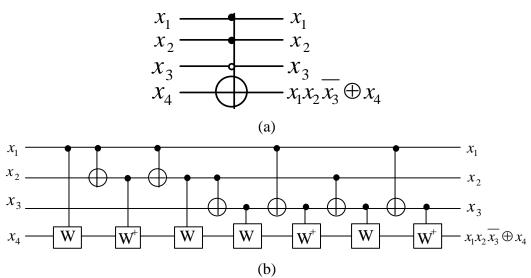

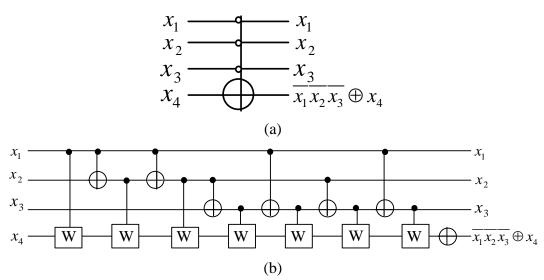

The mixed-polarity Toffoli4 gate is a four bit reversible gate. For mixed-polarity Toffoli4 gate with one or two negative bits, it has a quantum cost of 13. And as for mixed-polarity Toffoli4 gate with three negative bits, it has a quantum cost of 14. The gate the Boolean  $(x_1, x_2, x_3, x_4)$ maps pattern  $(x_1, x_2, (a_1 \oplus x_1)(a_2 \oplus x_2)(a_2 \oplus x_3) \oplus x_4)$ , where  $a_1, a_2, a_3$  are coefficients which tell that which line is a negative polarity control line. If  $a_x = 1$ , this means that line x is a negative polarity control line. Depending on which input bit to be a negative bit, the mixed-polarity Toffoli4 gate will result in three combinations. Figure 2.8 (a), Figure 2.9 (a) and Figure 2.10 (a) show the accepted symbol for these gates. Figure 2.8 (b), Figure 2.9 (b) and Figure 2.10 (b) show their quantum realization disclose within, where A is introduced as a new unitary matrix which is known as the Controlled-A gate. Such that  $A = \frac{1}{2} \begin{bmatrix} 1 - i\sqrt{i} & 1 + i\sqrt{i} \\ 1 + i\sqrt{i} & 1 - i\sqrt{i} \end{bmatrix}$ , which represents  $A = W^3 \times I$ NOT.

Figure 2.8. (a) Mixed-polarity Toffoli4 gate symbol with one negative bit (b) Quantum realization of the mixed-polarity Toffoli4 with one negative bit

Figure 2.9. (a) Mixed-polarity Toffoli4 gate symbol with two negative bits (b) Quantum realization of the mixed-polarity Toffoli4 with two negative bits

Figure 2.10. (a) Mixed-polarity Toffoli4 gate symbol with three negative bits (b) Quantum realization of the mixed-polarity Toffoli4 with three negative bits

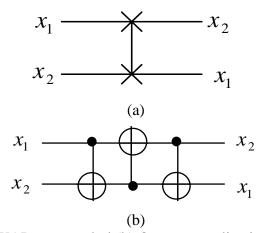

#### 2.3.7 The SWAP Gate

The SWAP gate is a two bit reversible gate, it has a quantum cost of 3 [55]. The gate maps a Boolean pattern  $(x_1, x_2)$  to  $(x_2, x_1)$ . Figure 2.11 (a) shows the accepted symbol of the gate with its function and Figure 2.11 (b) shows the quantum realization disclosed [55]. From its quantum realization connection as shown in Figure 2.11 (b), the SWAP gate is constructed from 3 CNOT gate.

Figure 2.11. (a) SWAP gate symbol (b) Quantum realization of the SWAP gate

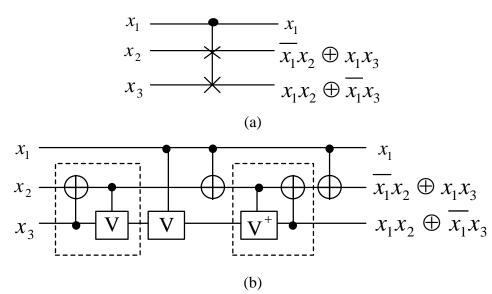

#### 2.3.8 The Fredkin Gate

The Fredkin gate [46] is a three bit reversible gate, it has a quantum cost of 5 [56]. The gate maps a Boolean pattern  $(x_1, x_2, x_3)$  to  $(x_1, \overline{x_1}x_2 \oplus x_1x_3, x_1x_2 \oplus \overline{x_1}x_3)$ . Figure 2.12 (a) shows the accepted symbol of the gate with its function and Figure 2.12 (b) shows the quantum realization disclosed [56-58]. From Figure 2.12 (b), when a CNOT gate is connected head-to-toe with a Controlled-V or a Controlled-V+gate, the quantum cost can be reduced to 1 [59, 60]. The Fredkin gate is known to be an universal gate which means that any logical or arithmetic operation can be solely constructed entirely using Fredkin gate [61, 62].

Figure 2.12. (a) Fredkin gate symbol (b) Quantum realization of the Fredkin gate

#### 2.3.9 The Peres Gate

When two control lines of a Toffoli gate are connected to a CNOT gate as seen in Figure 2.13, the CNOT gate constructed within the Toffoli gate and the external CNOT gate can be cancelled out following the reduction rules explained in [52]. The resulting logic circuit is known as the Peres gate [63]. The Peres gate is a three bit reversible gate, it has a quantum cost of 4 [48]. The gate maps a Boolean pattern  $(x_1, x_2, x_3)$  to  $(x_1, x_1 \oplus x_2, x_1x_2 \oplus x_3)$ . Figure 2.14 (a) shows accepted symbol with its function and Figure 2.14 (b) shows the quantum realization disclosed [64].

Figure 2.13. Toffoli gate with CNOT gate connected to both its control line

Figure 2.14. (a) Peres gate symbol (b) Quantum realization of the Peres gate

#### 2.3.10 The Inverse-Peres Gate

Unlike the CNOT and Toffoli gate, the Peres gate is not a self-reversible gate. This means that the inverse connection of the Peres gate will give different Boolean equation and hence result is a different gate. The inverse connection of the Peres gate is called the inverse-Peres gate or the TR gate in [65, 66]. It is a three bits reversible gate and has a quantum cost of 4. The gate maps a Boolean pattern  $(x_1, x_2, x_3)$  to  $(x_1, x_1 \oplus x_2, x_1 \overline{x_2} \oplus x_3)$ . Figure 2.15 (a) shows the accepted symbol with its function and Figure 2.15 (b) shows the quantum realization disclosed [64].

Figure 2.15. (a) TR gate symbol (b) Quantum realization of the TR gate

#### 2.4 Delay of Reversible Gates

The time required to execute a reversible gate is known as the propagation delay. As research on reversible logic remains on theoretical work, calculation of actual delay in time is not possible. Hence a difference metric for measuring delay is considered. In this dissertation, logical depth is used as delay measurement and is denoted by the symbol  $\triangle$  [44, 67]. Similar to quantum cost calculation, the propagation delay of each elementary quantum gate is considered as  $\triangle$  1 [44, 67]. Propagation delay of a reversible circuit can be measured in parallel. When two or more quantum gates are connected in parallel to one another, they are executed simultaneously; hence the propagation delay is only affected by the quantum gate that contributes to the highest delay. Table 2-4 shows the propagation delay of the reversible gate discussed in Section 2.3.

Table 2-4. Propagation delay of reversible gate

| Reversible Gate                                | Delay △ |

|------------------------------------------------|---------|

| NOT, CNOT                                      | 1       |

| Toffoli                                        | 5       |

| Toffoli4                                       | 13      |

| Mixed-polarity Toffoli (1 negative bit)        | 5       |

| Mixed-polarity Toffoli (2 negative bit)        | 6       |

| Mixed-polarity Toffoli4 (1 and 2 negative bit) | 13      |

| Mixed-polarity Toffoli4 (3 negative bit)       | 14      |

| SWAP                                           | 3       |

| Fredkin                                        | 5       |

| Peres, Inverse-Peres                           | 4       |

#### 2.5 Representation Model

Reversible functions can be described in several ways such as truth table, matrix, binary decision diagram and positive polarity Reed-Muller expansion. Each of these representations is discussed in details in the sub-sections below:

#### 2.5.1 Truth Table

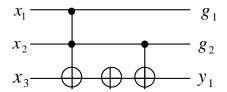

Truth table representation model is the simplest and straight forward method to describe a reversible function [68]. For a reversible function of n variable described using truth table representation, it will be written in a table of n columns and  $2^n$  rows. Figure 2.16 and Table 2-5 show an example of a reversible circuit and its truth table representation.

Figure 2.16. Reversible circuit

Table 2-5. Truth table representation

|   | Input           | Output          |

|---|-----------------|-----------------|

|   | $x_1, x_2, x_3$ | $g_1, g_2, y_1$ |

| 0 | 000             | 0 0 1           |

| 1 | 0 0 1           | 0 0 0           |

| 2 | 010             | 0 1 0           |

| 3 | 011             | 0 1 1           |

| 4 | 100             | 101             |

| 5 | 101             | 100             |

| 6 | 110             | 111             |

| 7 | 111             | 110             |

#### 2.5.2 Permutation Matrix

Permutation matrix based representation reflects the quantum state evolution of a reversible function [12, 69]. It represents the permutation function of a reversible

function in a 0-1 matrix with only one 1 appear in each column. If a reversible function has n variables, it will be represented by a matrix of  $2^n$  rows and columns. The (i,j)-th element of each column of the matrix is set to 1 when the input bit string corresponding to the i-th row is mapped to the output bit string corresponding to the j-th column [57]. Example below shows a matrix representation of a CNOT gate with it truth table defined in Table 2-6.

Table 2-6. CNOT gate truth table

|   | Input      | Output     |

|---|------------|------------|

|   | $x_1, x_2$ | $y_1, y_2$ |

| 0 | 0 0        | 0 0        |

| 1 | 0 1        | 0 1        |

| 2 | 1 0        | 1 1        |

| 3 | 11         | 10         |

The output of the CNOT gate is written as its permutation form

$$|00\rangle = \begin{bmatrix} 1\\0\\0\\0 \end{bmatrix}, |01\rangle = \begin{bmatrix} 0\\1\\0\\0 \end{bmatrix}, |10\rangle = \begin{bmatrix} 0\\0\\1\\0 \end{bmatrix}, |11\rangle = \begin{bmatrix} 0\\0\\0\\1 \end{bmatrix}$$

Writing the outputs into a matrix, the permutation matrix of the CNOT gate is expressed as

$$CNOT = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \end{bmatrix}$$

#### 2.5.3 Binary Decision Diagram

Any Boolean function can be visually represented by different type of Decision Diagrams (DD) [70-72]. A Binary Decision Diagram (BDD) is a directed acyclic graph where a Shannon decomposition ( $f = \overline{x}_t f_{x_i=0} + x_i f_{x_i=1}$ ) is carried out in each non-terminal node [43, 73]. Figure 2.17 shows an example of a BDD for the Boolean function  $x_3 + x_1 x_2$ .

Chapter 2 Background

Figure 2.17. BDD for Boolean function  $x_3 + x_1x_2$

#### 2.5.4 Reed Muller Expansion

Any Boolean function can be described as EXOR sum-of-product (ESOP) expansion [74]. Since most commonly used reversible gates reflect their operation in Reed Muller logic form, this makes Reed Muller expansion suits reversible logic expression better [75]. The positive-polarity Reed-Muller (PPRM) expansion is those un-complemented ESOP expansion which can be written as a polynomial of the form  $a_0 \oplus a_1 x_1 \oplus ... \oplus a_n x_n \oplus a_{1,2} x_1 x_2 \oplus a_{1,3} x_1 x_3 \oplus ... \oplus a_{n-1,n} x_{n-1} x_n \oplus ... \oplus a_{1,2,...,n} x_1 x_2 ... x_n$  where  $a_0, a_1, ..., a_n, a_{1,2}, a_{1,3}, ..., a_{1,2,...,n}$  refer to the Boolean coefficients [76]. The size of a PPRM expansion is  $2^n$  where n denotes the number of variables. To express a Boolean function into the PPRM expansion, the Boolean function is first expressed in their ESOP expansion. Then the un-complement rule  $\overline{x_n} = 1 \oplus x_n$  is applied to all complemented term, where  $\overline{x_n}$  refers to the complemented term. Example below shows a logic function expressed in its ESOP expansion and how it is converted into its PPRM expansion [75].

$y = \bar{a}b \oplus \bar{b}\bar{c}$   $= (1 \oplus a)b \oplus (1 \oplus b)(1 \oplus c)$   $= (b \oplus ab) \oplus (1 \oplus b \oplus c \oplus bc)$   $= 1 \oplus c \oplus ab \oplus bc$

#### CHAPTER 3 LITERATURE REVIEW

In this chapter, existing literature works related to the research work are being discussed. In Section 3.1, review on the commonly used reversible logic synthesis algorithms proposed by various authors over the period has been discussed. In Section 3.2, review on the existing design of reversible full adder circuit has been discussed. In Section 3.3, review on the existing research work on reversible BCD adder has been discussed.

## 3.1 Related Work on Synthesis of Reversible Logic

In this section, overviews of the widely proposed reversible logic synthesis algorithm are discussed. The synthesis algorithms are being categorized into several subsections according to their types and functions.

#### 3.1.1 Transformation Based Synthesis Algorithm

Transformation based synthesis algorithm is one of the earliest developed reversible logic synthesis algorithm. The synthesis algorithm was first introduced by Iwama et al. [25] in which the authors proposed several rules to transform Boolean function into a set of Toffoli based circuits. The proposed work has shown that any circuit can be brought to a canonical form through utilizing their proposed rules. Unfortunately, the proposed work does not provide any practical example thus the proposed work are more for theoretical interest. The algorithm was later extended by Miller et al. [26] by adding transformation rules on a set of predefined patterns called templates. The algorithm works by transforming Boolean function into a set of Toffoli based circuits in the truth table format using the defined transformation rules. After the resulting Toffoli based circuit has been obtained, several simple template matching rules are applied to further simplify the circuit. The synthesis results were considerably good during the era. An extension version to the existing synthesis algorithm given in [25],[26] has been made by Dueck et al. [28] and Maslov et al. [29], respectively, which has added SWAP gate and Fredkin gate into their

transformation database. The algorithm given in [26] was later improved by Maslov et al. [77] by introducing bidirectional algorithm that allows the algorithm to iterate through the truth table looking for difference between the inputs and outputs rather than the traditional method which searches only on the output side. Later Malsov et al. [78] used a mixture of different techniques which includes the MMD (Miller-Maslov-Dueck) developed in [77], template matching, Reed-Muller spectra and resynthesis to synthesize reversible function in term of gate count or quantum cost. The synthesis algorithm drops the traditional truth table representation method use by earlier algorithms and uses the Reed-Muller spectra form which direct reflects the reversible gate's operation from the NCT gate library. Using the Reed-Muller spectra form, it gives better gate substitution as compared to the earlier method and thus improves in the synthesis results. The flow of the algorithm can be broken into three steps. In the first step, the MMD is applied which selects reversible gates for transformation until all identity term is determined. In the second step, template matching is applied which simplify each of the synthesized networks using templates, choosing smaller network. In the last step, resynthesis is applied where a sequence of gates is chosen from the network as an independent problem and computation are preformed to reduce the quantum cost.

# 3.1.2 Rule Based Synthesis Algorithm

Arabzadeh et al. [33] proposed a rule based optimization approach that can be used after transformation based synthesis algorithm such as that given in [26, 77] to transform NCT based gate circuit into mixed-polarity Toffoli gate based circuit. The algorithm works by adding rules to reduce redundant NOT gate on the synthesized circuit. The algorithm can be broken into two steps: during the first step, multiple NOT gates are applied all across a given reversible circuit and converting Toffoli based gates into mixed-polarity Toffoli gate, all redundant NOT gates are being removed at this step. At the second step, a Karnaugh map-based optimization is applied to optimize sub-circuits with common-target gates.

Datta et al. [79], the authors proposed a post-synthesis optimization rules that uses template matching to transform NCT based reversible circuits into a cascade of

mixed-polarity based circuit. Template matching rules are applied to cascade several Toffoli based gates together to match the function of a mixed-polarity based gate and replace them accordingly. Their current template rules are only capable of matching mixed-polarity Toffoli gate up to 4 variables.

#### 3.1.3 Cycle Based Synthesis Algorithm

Cycle based synthesis algorithm are known for separating the entire permutation into several cycles and synthesize them separately. The first cycle based synthesis algorithm is introduced by Shende et al. [27] in which the algorithm decompose any given permutation into a set of disjoint cycles and synthesize individual cycle separately. This method is efficient when dealing with permutations that do not have a regular patterns and reversible function that leave many input combinations unchanged. Yang et al. [80] introduced a similar method to [27] except that the algorithm choose to drop the uses of CNOT gate and uses only NOT and Toffoli gate when synthesizing qubit function that is greater than 3 variables. The algorithm has proposed several permutations formula that can be easily applied on targeted function area and transform them to obtain the synthesized gates. And Prasad et al. [81] improve the existing algorithm in [27] by applying NOT and CNOT gates instead of Toffoli gate in many situations. The gate count and quantum cost results improves dramatically through applying the following changes.

Sasanian et al. [82] extended the algorithm given in [27] by removing the decomposition of larger cycles into a set of 2-cycles which results in using more reversible gates. In the proposed method, larger cycles are decomposed into a set of single 3-cycles, pairs of 3-cycles, and pairs of 2-cycles and synthesize the resulted cycle directly. This direct implementation of cycles greatly reduce unwanted reversible gates in the synthesis algorithm compared to the existing algorithm given in [27].

In Saeedi et al. [83], a k-cycle-based synthesis method is developed that uses a set of seven building blocks to directly synthesize a given permutation to reduce both quantum cost and average run-time. Given a large cycle inputs, the synthesis

algorithm uses the decompose rules to extract the seven building blocks from the input specification before synthesizing them. The seven building blocks include a pair of 2-cycles, a single 3-cycles, a pair of 3-cycles, a single 5-cycles, a pair of 5-cycles, a single 2-cycles (4-cycles) followed by a single 4-cycles (2-cycles) and a pair of 5-cycles. This algorithm shows capability to synthesize reversible function of large variable (up to variable size of 20 given a time limit of 12 hour per function) and produces better quantum cost result for reversible benchmark function for variable size 8 and above.

In Saeedi et al. [84], the proposed algorithm uses a set of building blocks and a library to synthesize a given specification. Each specification is considered as a permutation with several cycles where each cycle is synthesized by some reversible gates. If a given cycle is found in the library, it is synthesized directly. Otherwise, a decomposition algorithm detaches the building blocks from the given cycle and explores all possible minimal and inequivalent factorizations where the number of disjoint cycles is maximized. Experimental results have shown that the proposed approach reduces the quantum cost and runtime.

#### 3.1.4 Binary Decision Diagrams Based Synthesis

Binary Decision Diagrams (BDDs) based synthesis algorithm was first introduced by Kerntopf [85]. For any given Boolean function, a Decision Diagram is constructed through examine all possible gates. Gates that minimize the Decision Diagram complexity are selected and further analyzed by repeating the same process. The process stops when all paths are analyzed and the minimal node path is selected and transformed into reversible circuits. Wille et al. [86] introduced a different algorithm which starts by directly constructing a BDD. Each of the BDD nodes is substituted by a cascade of reversible gates. Since BDDs may contain shared nodes, hence it will result in using fan-outs which is not allowed in reversible logic. To overcome it, additional ancilla input and CNOT gate are added. Although the algorithm leads to a good reduction in quantum cost, but the usage of a large amount of ancilla input is rather impractical. The algorithm is later improved by Wille et al. [3], by introducing a post-processing optimization method that reduces the garbage line by merging

some garbage output lines with appropriate ancilla input lines. Although improvement has been made, improvement is not obvious and the problem remains.

Krishana et al. [87] introduced a technique that uses isomorphic sub-graph matching which helps map sub-graphs of the BDD to structures with known reversible circuit templates. Using this approach it greatly reduces the number of ancilla inputs made by earlier BDD based synthesis algorithm [86].

Ancilla problem for BDD based synthesis algorithm was finally solved by a recent proposed synthesis algorithm by Soeken et al. [88]. The concept of the proposed algorithm in [88] is based on Young subgroups using symbolic function representations than can efficiently be implemented with BDDs. As a result the synthesis algorithm generates no ancilla inputs and able to cope with large reversible functions.

# 3.1.5 Search Based Synthesis Algorithm

Gupta et al. [89] proposed a search based synthesis algorithm, which reversible logic s synthesized in term of gate count using positive polarity Reed-Muller (PPRM) expansion. The algorithm works by traversing the input reversible function into a search tree and determine all possible solution using the gate matching factor. For a given amount of time, the algorithm searches all possible solution and stores only the best solution.

The algorithm was later improved by Saeedi et al. [90], which introduced several new substitutions rules to the original ones. Their experimental results have shown that their method can lead to a better synthesis circuit with respect to the total circuit cost as well as the probability of leading to a synthesized circuit better than the existing algorithm given in [89].

Donald et al. [30] further extended the algorithm of [89] to handle SWAP gate, Fredkin gate, Peres gate and reverse Peres gate in a similar search based framework. Capability to synthesize in term of quantum cost was also added to the algorithm.

The synthesis method of the algorithm remains unchanged compared to the earlier work given in [89].

#### 3.1.6 Graph Based Synthesis Algorithm

Graph based synthesis algorithm is proposed by Yexin et al. [91] in which reversible logic is synthesized in term of gate count using NCT library gates. The algorithm targets on faster synthesis time by reducing the function complexity during each synthesis steps. Although synthesis time is shorten, the algorithm is still able to capable of finding possible solution for all input reversible function. The drawback of the algorithm is that it lacks of the ability to determine the best gate to substitute in each step and hence often uses more unnecessary gates to realize a function.

## 3.1.7 Optimal Based Synthesis Algorithm

In Golubitsky et al. [92], the authors presented an optimal based reversible synthesis algorithm which is capable of finding optimal solution through matching the input reversible function to a set of presets in their database. Using the database, the gate count of the optimal circuit can be easily found in a short amount of time through lookup in their canonical representative form. Golubitsky et al. [54] made an extension to further improve the existing database in [92] which removes all inverse functions and added several new functions to the existing databases. This improves the performance of the algorithm and allows the algorithm to synthesize reversible functions or higher variables. When dealing with larger reversible function, the algorithm may break the function into several sub-functions and matches them individually using their database and combine them afterwards.

Szprowski et al. [34] further extends the algorithm presented in [92] through adding method to further synthesize in term of quantum cost after being synthesize using the algorithm given in [92]. The proposed algorithm is able to generate optimal circuits up to 4 variables based reversible functions. Although gate count is at minimal but this does not mean that these circuits are exact minimal in terms of quantum cost.

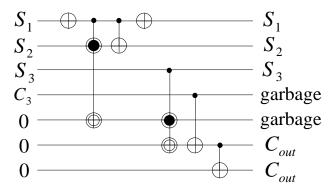

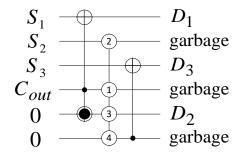

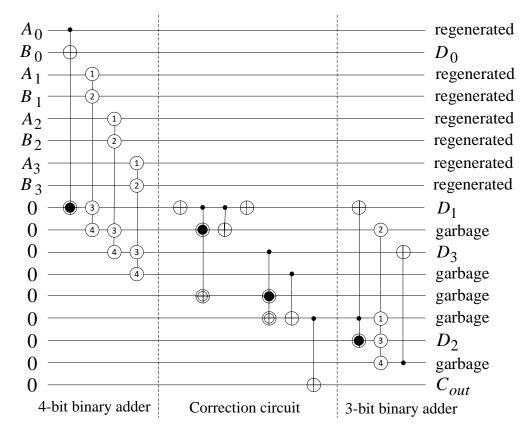

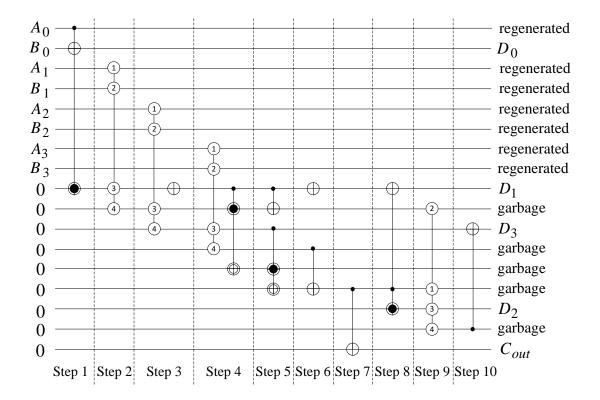

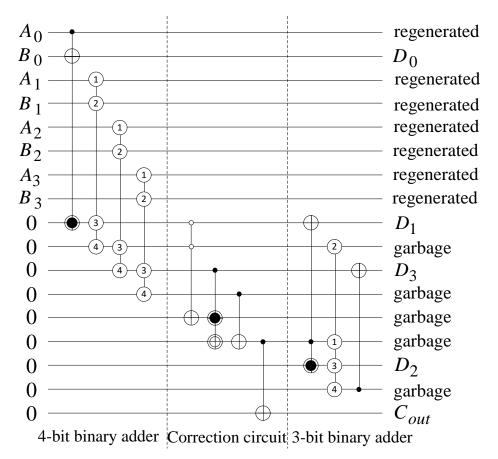

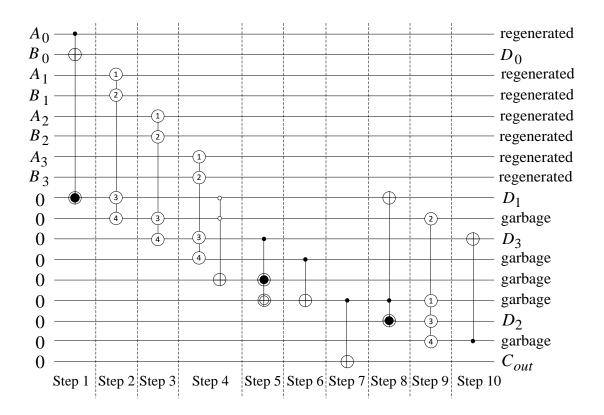

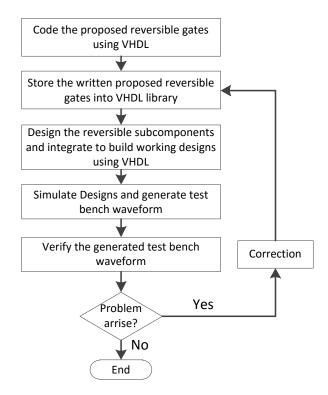

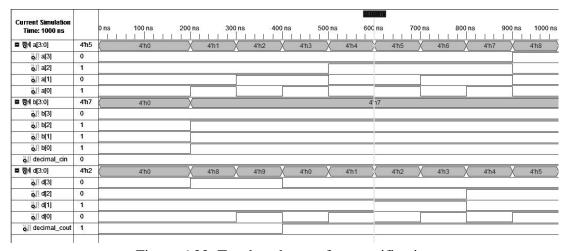

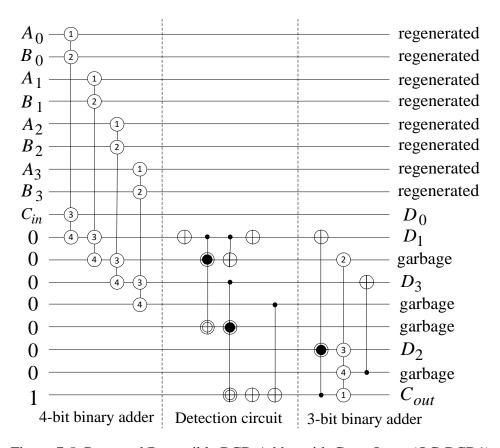

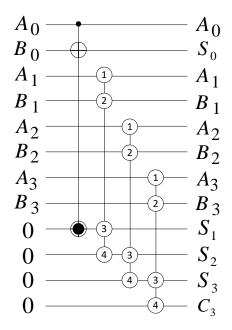

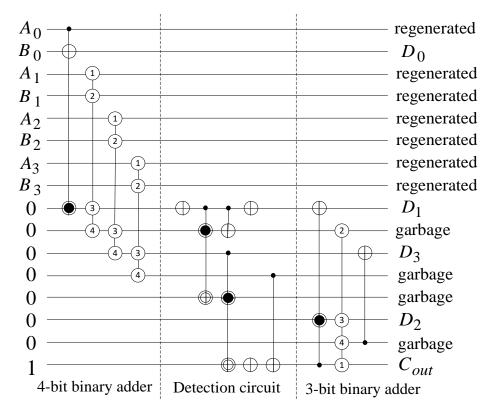

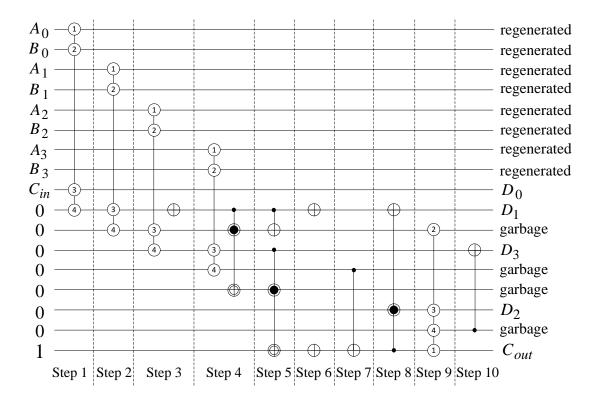

This is because there might be longer cascades with lower quantum cost value. In Golubitsky et al. [93], the authors further improve the algorithm in [34] by using only classical decompositions techniques without using additional lines. By using this technique, it provides substantial saving of quantum cost. Szyprowski et al. [36] further extended the work given in [93] by adding mixed-polarity based Toffoli gate into the synthesis library.