# Australian Telecommunications Research Institute (ATRI) and Co-operative Research Centre for Broadband Telecommunications and Networking (CRC-BTN)

# Frame Synchronization Techniques and Jitter Generation: Analysis, Modelling and Enhancement

Jacqueline Walker

This thesis is presented as part of the requirements for the award of the Degree of Doctor of Philosophy of the Curtin University of Technology

# Acknowledgements

Firstly, I would like to thank Professor Tony Cantoni, my supervisor. Although an extremely busy person, Tony still manages to find the time to assist students. I also appreciate his understanding towards my particular needs as a new mother.

Secondly, I would like to thank Giles for his encouragement and practical support and my sister, Amanda, for helping with Oisin.

## **Abstract**

Synchronization means the aligning of the significant instants of one signal to the significant instants of another. In digital systems, where timing transfer between systems is required, synchronization is an important function. In this thesis new results on the performance and design of synchronization processes are presented.

An inescapable consequence of the synchronization of external autonomous inputs in digital systems is the possibility of failure of digital devices used to capture the external signal. The anomalous behaviour of these devices is referred to as metastability. The most commonly used approach to controlling the problem of metastability is the use of synchronizers. A synchronizer can be designed to reduce the probability of metastable failure but cannot eliminate it altogether. New high performance synchronizer designs are presented and analysed in this thesis.

Another consequence of synchronization is the resulting disturbance of the significant epochs of timing signals. This disturbance is referred to as jitter. The characterization of jitter produced in synchronization processes is important in the design of digital systems. In this thesis, jitter characteristics are derived for two important applications that arise in digital communications systems. The characterization provides new insight into the dependence of the jitter on system parameters.

# Contents

| 1 I  | ntroduction                                                                                         | 1        |

|------|-----------------------------------------------------------------------------------------------------|----------|

| 1.1  | Motivation and Applications                                                                         |          |

|      | 1.1.1 External Timing Source Injection for an ATM LAN                                               |          |

|      | 1.1.2 Synchronous Residual Time Stamp (SRTS) Timing Transfer                                        |          |

|      | Contributions                                                                                       |          |

|      | Outline of the Thesis                                                                               |          |

|      | Metastability                                                                                       |          |

|      | Introduction                                                                                        |          |

| 2.2  | The Problem of Metastable Failure.                                                                  | 10       |

| 2.3  | Synchronizer Designs and their Assessment                                                           | 12       |

|      | 2.3.1 A Framework for Assessment of Synchronizer Performance                                        |          |

|      | 2.3.2 Existing Synchronizer Designs                                                                 | 13       |

|      | 2.3.3 Three New Synchronizer Designs.                                                               | 16       |

|      | 2.3.3.1 The Asynchronous Front End Synchronizer                                                     | 16       |

|      | 2.3.3.2 The Synchronous Front End Synchronizer Designs                                              | 20       |

|      |                                                                                                     |          |

|      | pendix 2A: Glossary                                                                                 |          |

|      | pendix 2B: Metastable Failure Probability Equations                                                 |          |

| 3 J  | itter                                                                                               | 30       |

| 3.1  | Introduction                                                                                        | 31       |

| 3.2  | Jitter - Definitions, Framework and Modelling                                                       | 31       |

|      | 3.2.1 Definition of Time Jitter                                                                     |          |

|      | 3.2.2 Jitter Recurrence Equation                                                                    |          |

|      | Time Jitter and Phase Jitter                                                                        |          |

|      | The Synchronization Process Jitter Equation for an Ideal Asynchronous Input                         |          |

|      | Fourier Transforms of Jitter                                                                        |          |

| 3.6  | The Synchronization Process Jitter Equation for a Jittered Asynchronous Input                       | 41       |

| 3.7  | Jitter Spectrum for the Jittered Asynchronous Input                                                 | 44       |

| App  | pendix 3A: Glossary                                                                                 | 46       |

| App  | pendix 3B: Jitter Approximations                                                                    | 48       |

| App  | pendix 3C: Derivation of the Synchronization Process Jitter Equation                                | 49       |

| App  | endix 3D: Stability of the Synchronization Process Jitter Equation                                  | 51       |

| Арр  | endix 3E: RMS Jitter Power of the Synchronization Process Jitter                                    | 52       |

| App  | endix 3F: Derivation of the Synchronization Process Jitter Equation with Input Jitter               | 53       |

| App  | endix 3G: Stability of the Jitter Equation for a Jittered Asynchronous Input                        | 54       |

|      | endix 3H: Spectrum of the Jitter Equation for a Jittered Asynchronous Input                         |          |

| 4 Ji | tter Generation in External Timing Source Injection                                                 | 58       |

|      | Introduction                                                                                        |          |

|      | Timing Reference Transfer and Jitter in Digital Communications Networks                             | 59       |

| 42   | 4.2.1 External Timing Source Injection                                                              |          |

| 4.3  | The Conventional Stuffing Approach to XTS Injection                                                 | 66       |

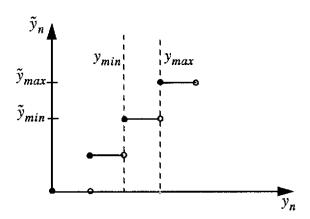

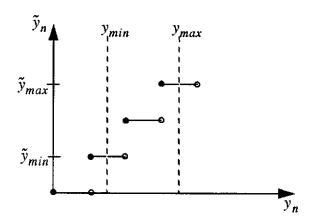

|      | 4.3.1 The Jitter Equation for the Conventional Stuffing Synchronizer 4.3.2 Measurement Quantization | 67<br>20 |

|      | 4.3.3 Jitter Spectrum of the Conventional Stuffing Synchronizer                                     | 0ሃ<br>71 |

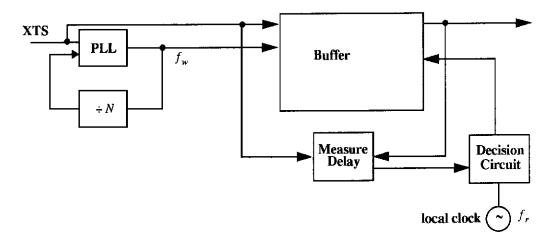

| 4.4  | The Frame Sampling Synchronizer Approach to XTS Injection                                           |          |

| •••  | 4.4.1 Effect of Different Synchronizer Designs                                                      | 12<br>72 |

|      | ^                                                                                                   | , 2      |

| 4.4.2 The Jitter Equation for the Frame Sampling Synchronizer                      | 75   |

|------------------------------------------------------------------------------------|------|

| 4.5 External Timing Source Injection and Waiting Time Jitter                       |      |

| Appendix 4A: Glossary                                                              |      |

| Appendix 4B: Stability of the Conventional Stuffing Synchronizer Jitter Equation   |      |

|                                                                                    |      |

| Appendix 4C: Derivation of the Conventional Stuffing Synchronizer Equation         |      |

| Appendix 4D: Measurement Quantization in the Conventional Stuffing Synchronizer    | 91   |

| Appendix 4E: The Spectrum of the Jitter for the Conventional Stuffing Synchronizer |      |

| 5 Jitter Generation and the Synchronous Residual Time Stamp                        |      |

| 5.1 Introduction                                                                   |      |

| 5.2 The SRTS Method                                                                |      |

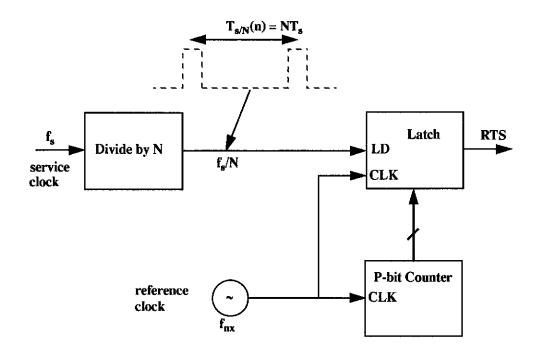

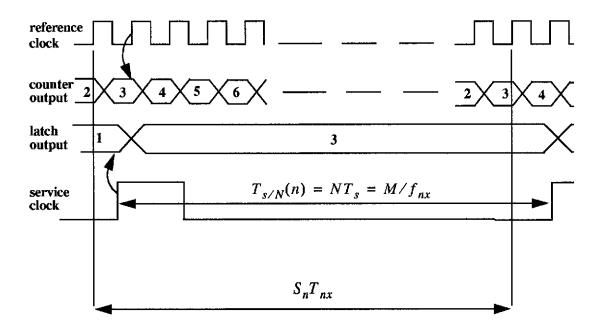

| 5.2.1 RTS Generation                                                               |      |

| 5.2.2 Transport of the RTS                                                         |      |

| 5.2.4 Requirement for a Synchronizer in RTS Generation                             |      |

| 5.3 Jitter Generation in the SRTS Method                                           | 106  |

| 5.3.1 Jitter Generation in an Ideal SRTS System                                    | 106  |

| 5.3.2 Jitter Spectrum for the Ideal Model of RTS Generation                        |      |

| 5.4 Choosing Parameters in RTS Generation                                          | 110  |

| Appendix 5A: Glossary                                                              | 115  |

| Appendix 5B: Derivation of the Number of Bits to Uniquely Identify RTS             | 117  |

| Appendix 5C: Proof of Correctness of the New Method of S <sub>n</sub> Regeneration | 118  |

| Appendix 5D: Existence of L and the nominal stuff ratio for a given x              |      |

| 6 The Experimental Study of the Jitter Spectrum                                    | 120  |

| 6.1 Introduction                                                                   | 121  |

| 6.2 Description of the Experiment                                                  |      |

| 6.3 Verification of the Synchronization Process Jitter Spectrum Model              | 123  |

| 6.3.1 Plotting the Predicted Jitter Spectrum.                                      | 123  |

| 6.3.2 Experimental Results                                                         |      |

| 6.4 Verification of Jitter Spectrum for Sinusoidal Input Jitter Case               | 129  |

| 6.4.2 Experimental Results                                                         | 129  |

| 6.5 Use of Sinusoidal Input Jitter as Jitter Reduction Mechanism                   |      |

| 6.5.1 An Example of Jitter Reduction Using Sinusoidal Input Jitter                 | 140  |

| Appendix 6A: Glossary                                                              |      |

| 7 Further Work                                                                     | 144  |

|                                                                                    | 1.47 |

# **Figures**

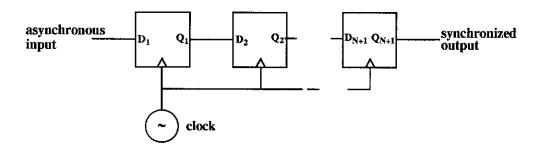

| 2.1  | A shift register synchronizer.                                           | 13   |

|------|--------------------------------------------------------------------------|------|

| 2.2  | Timing diagram for the shift register synchronizer when N=2              | 14   |

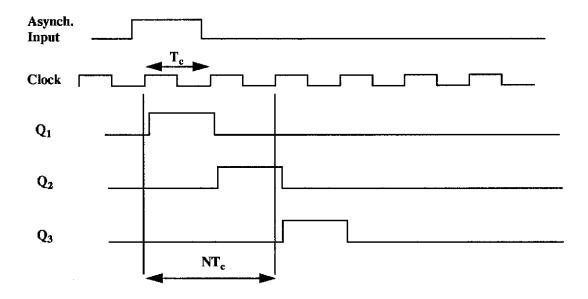

| 2.3  | A divided clock synchronizer.                                            | 14   |

| 2.4  | Timing diagram for the divided clock synchronizer for N=3                | 15   |

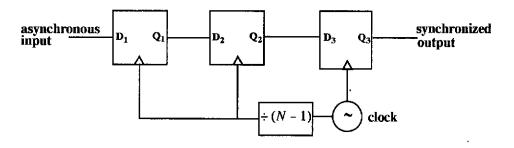

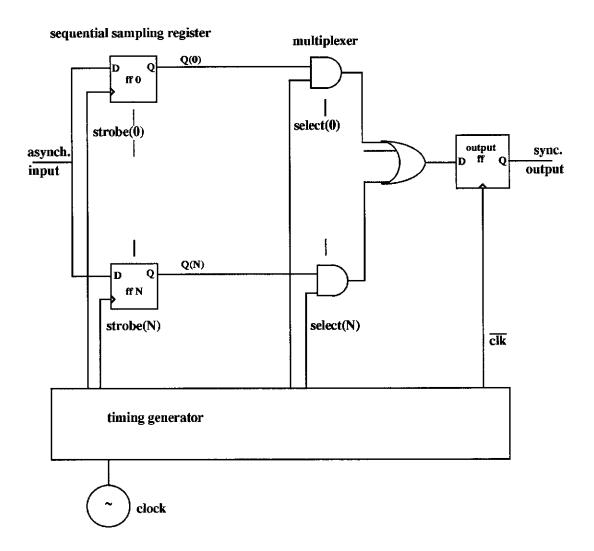

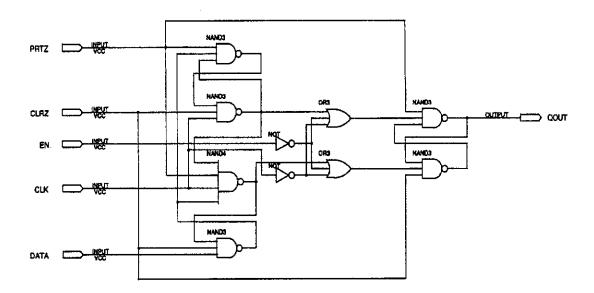

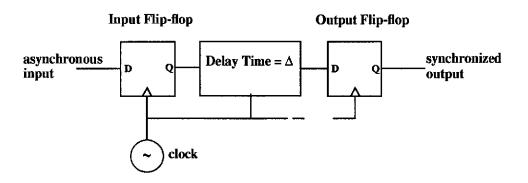

| 2.5  | The new AFE synchronizer.                                                | 17   |

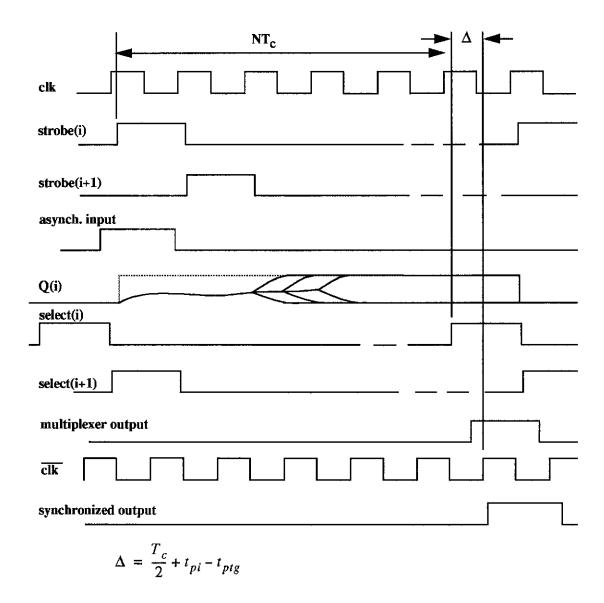

| 2.6  | Timing diagram for AFE synchronizer.                                     | 18   |

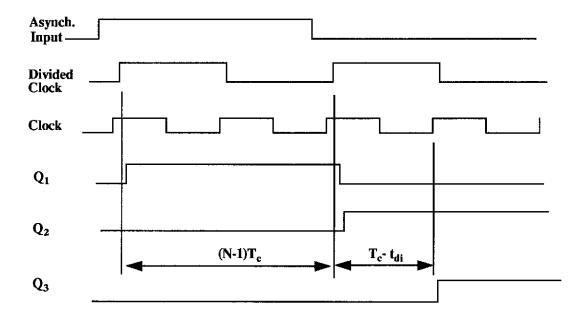

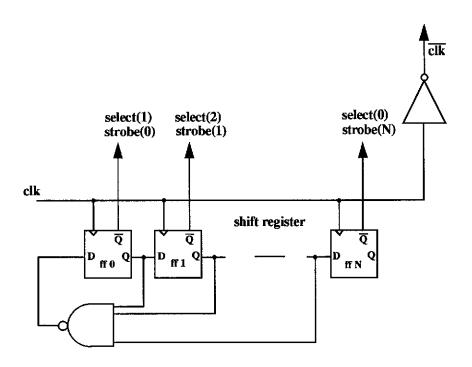

| 2.7  | Possible implementation of the timing generator.                         | 19   |

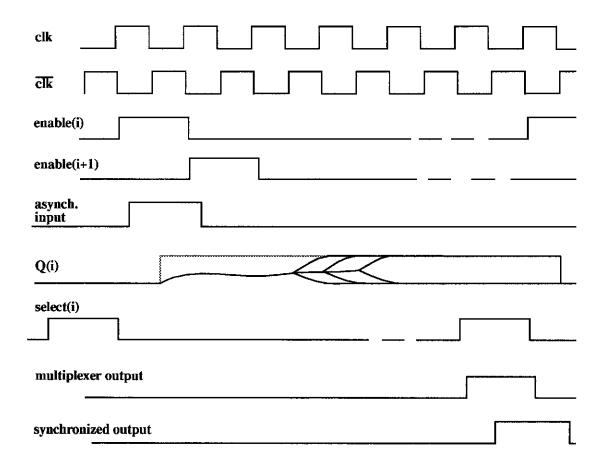

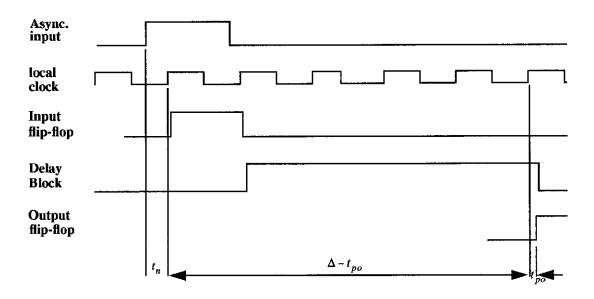

| 2.8  | The front end of the new SFE synchronizer design                         | 21   |

| 2.9  | Timing diagram for SFE synchronizer                                      | 22   |

| 2.10 | Alternative enable flip-flop implementation.                             | 24   |

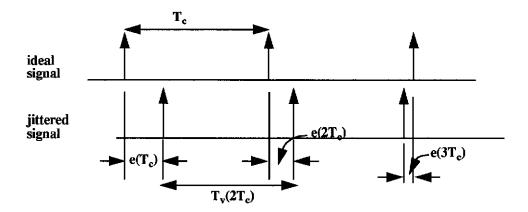

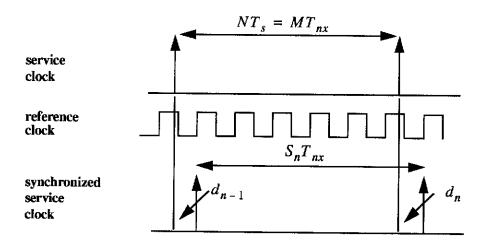

| 3.1  | Definition of time jitter                                                | 32   |

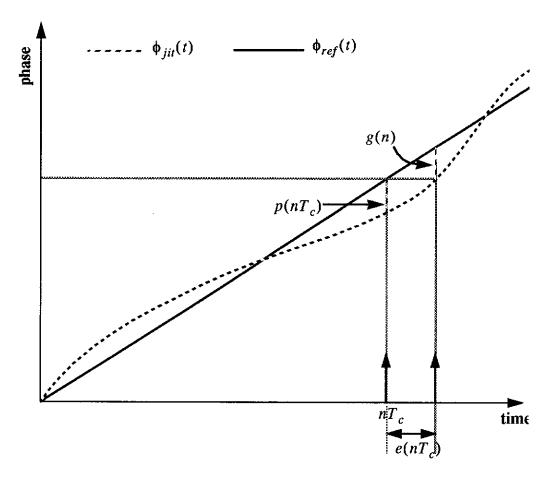

| 3.2  | Distinction between time jitter and phase jitter.                        | 34   |

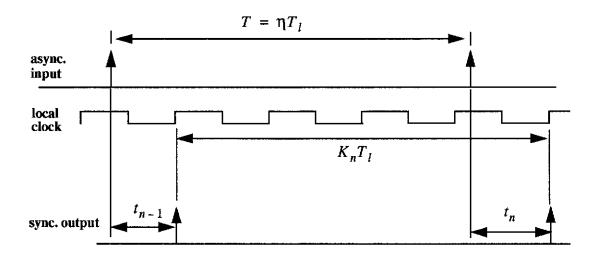

| 3.3  | Synchronization process jitter diagram.                                  | 37   |

| 3.4  | Mapping local clock onto period of asynchronous input.                   | 38   |

| 3.5  | Timing diagram for a jittered asynchronous input                         | 41   |

| 3.6  | Mapping local clock onto jittered asynchronous input period              | 42   |

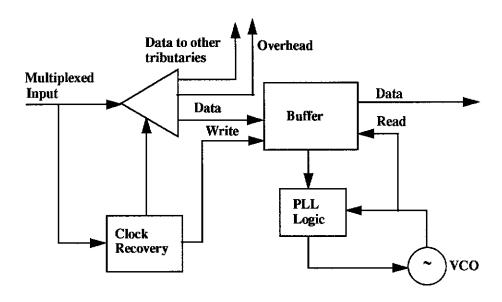

| 4.1  | Simple block diagram of a synchronizer in a PDH multiplexer              | 61   |

| 4.2  | Simple block diagram of a desynchronizer in a PDH demultiplexer          | 62   |

| 4.3  | Conventional stuffing synchronizer.                                      | 66   |

| 4.4  | Conventional stuffing synchronizer jitter diagram.                       | 68   |

| 4.5  | Thresholds on quantization boundaries.                                   | 70   |

| 4.6  | Generalised design of a synchronizer.                                    | 73   |

| 4.7  | Timing diagram for the generalised synchronizer design                   | 74   |

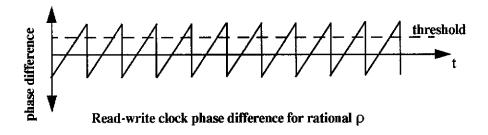

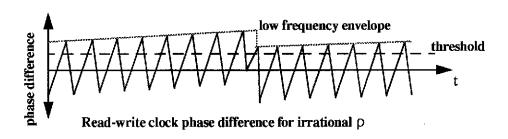

| 4.8  | Presence of low frequency envelope for irrational rho.                   | 79   |

| 4.9  | Classical waiting time jitter characteristic.                            |      |

| 4D.1 | Thresholds between quantization boundaries.                              | . 91 |

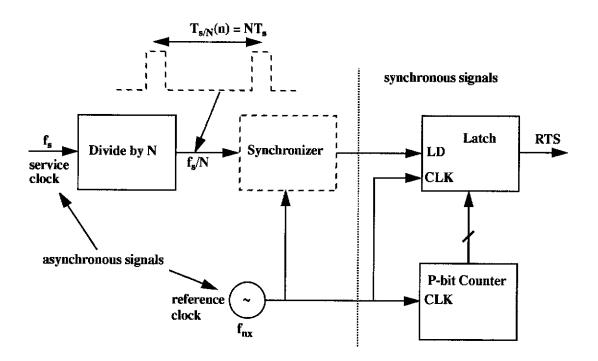

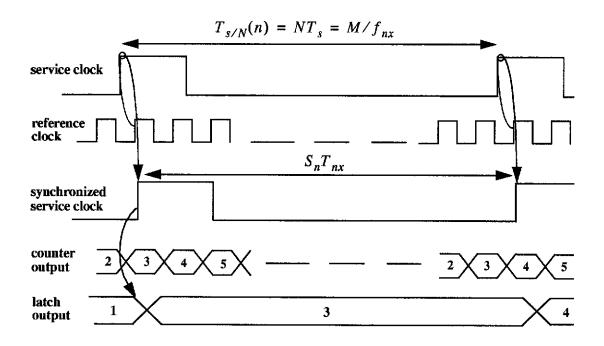

| 5.1  | RTS Generation in the SRTS Method                                        |      |

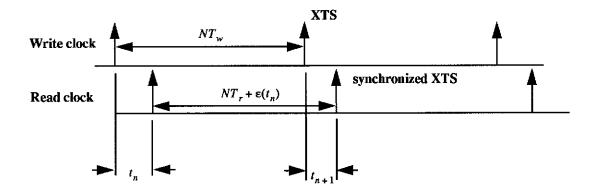

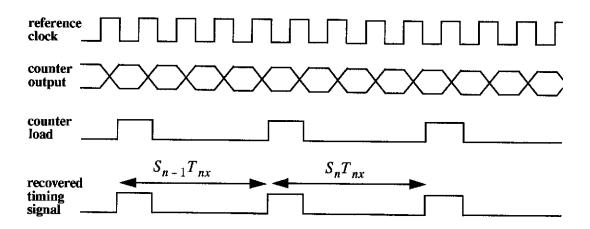

| 5.2  | Timing Diagram of SRTS Method                                            | . 99 |

| 5.3  | General principle of timing transport by AAL1 for CBR sources.           |      |

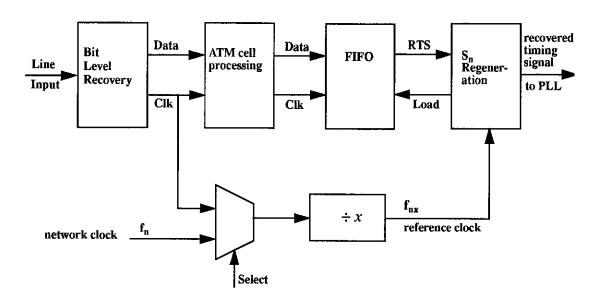

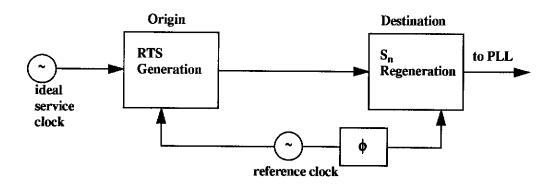

| 5.4  | Overview of regeneration of the timing signal at the destination         |      |

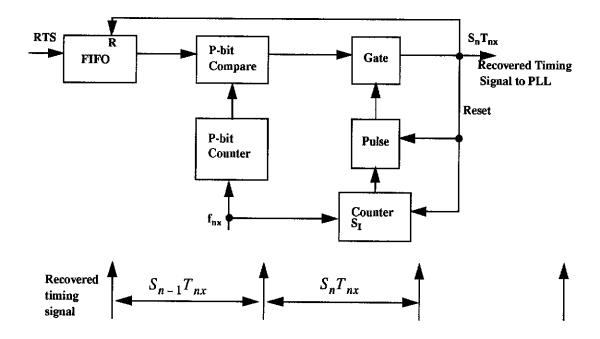

| 5.5  | Possible implementation of S <sub>n</sub> regeneration                   |      |

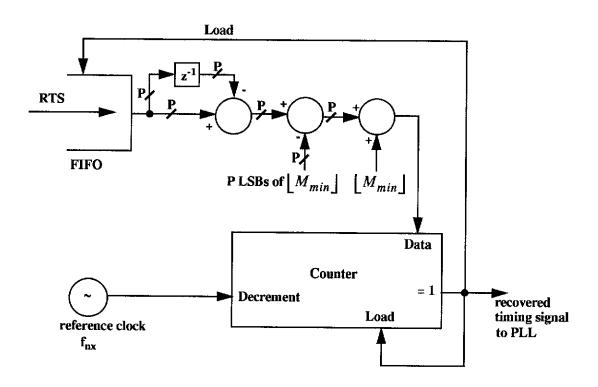

| 5.6  | New method for regeneration of the timing signal at the destination      |      |

| 5.7  | Timing diagram for regeneration of the timing signal                     |      |

| 5.8  | Need for a synchronizer in RTS generation                                |      |

| 5.9  | Timing diagram of SRTS Method with synchronizer.                         |      |

| 5.10 | SRTS system model.                                                       |      |

| 5.11 | Timing diagram to show jitter in RTS generation.                         |      |

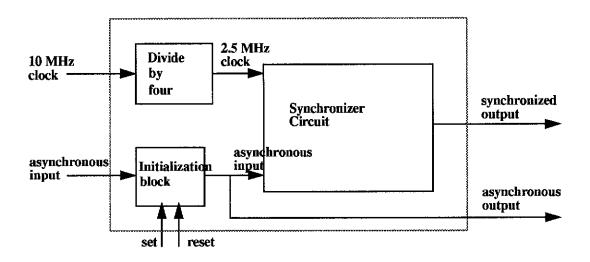

| 5.1  | Functional block diagram of experimental system.                         |      |

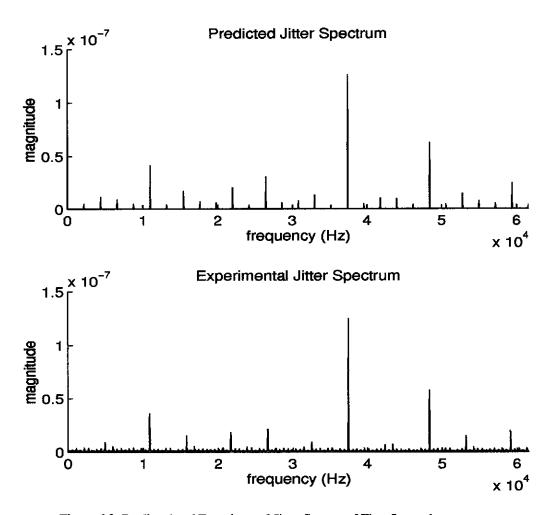

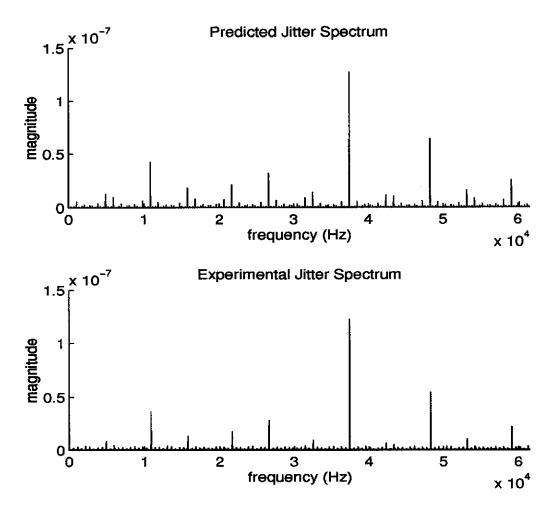

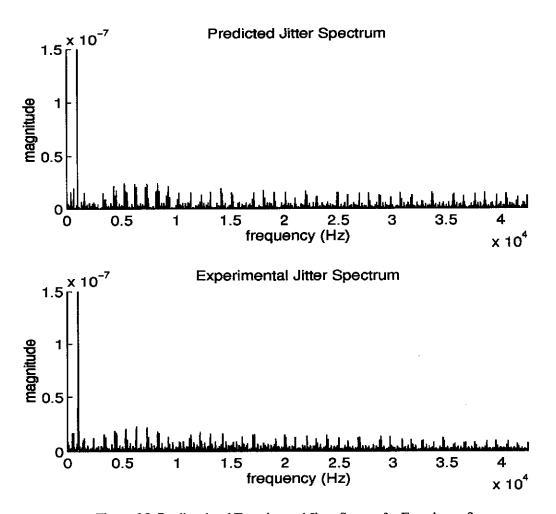

| 5.2  | Predicted and Experimental Jitter Spectra of Time Interval measurement   |      |

| 5.3  | Predicted and Experimental Jitter Spectra of Time Deviation measurement. | 127  |

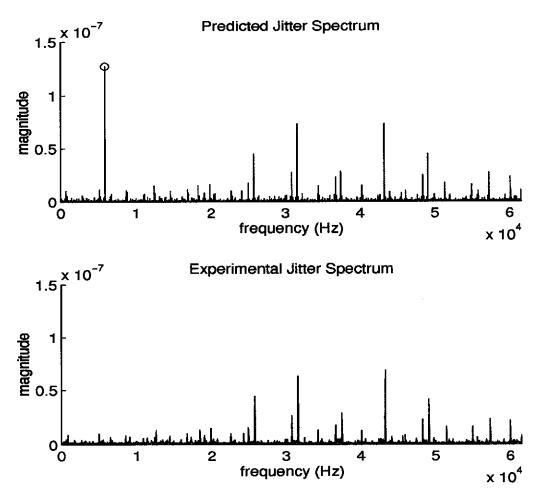

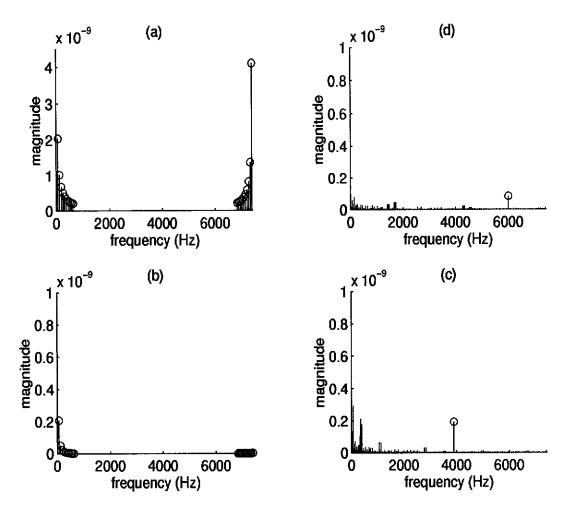

| 6.4  | Predicted and Experimental Jitter Spectra for Experiment 3         | 133 |

|------|--------------------------------------------------------------------|-----|

| 6.5  | Predicted and Experimental Jitter Spectra for Experiment 4.        | 134 |

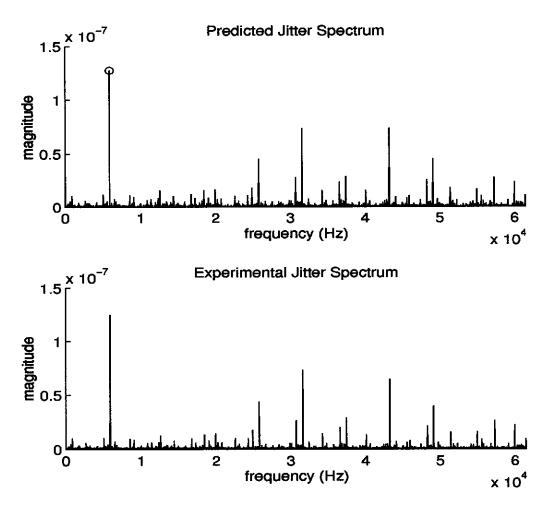

| 6.6  | Predicted and Experimental Jitter Spectra for Experiment 5.        | 135 |

| 6.7  | Predicted and Experimental Jitter Spectra for Experiment 6         | 136 |

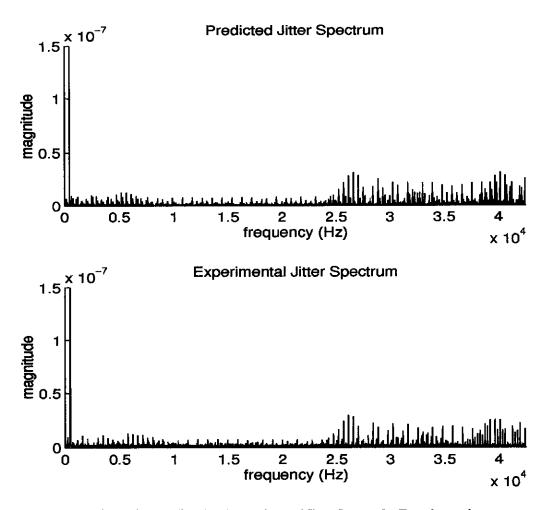

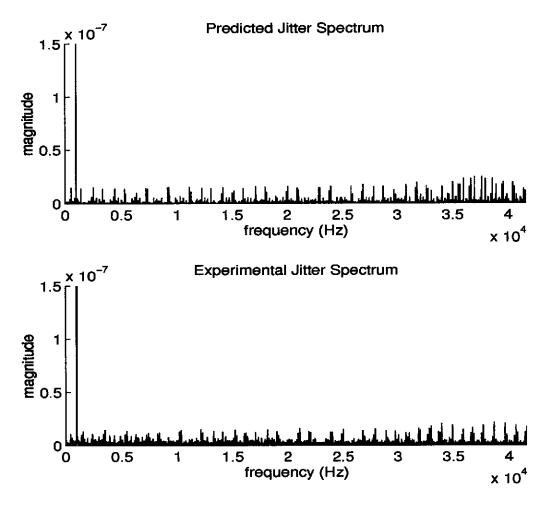

| 6.8  | Predicted and Experimental Jitter Spectra for Experiment 7.        | 137 |

| 6.9  | Predicted and Experimental Jitter Spectra for Experiment 8.        | 138 |

| 6.10 | Jitter Reduction from Sinusoidal Input Jitter: SRTS method example | 141 |

# **Tables**

| 2.1 | Synchronizer Performance Comparison                                  | 25  |

|-----|----------------------------------------------------------------------|-----|

| 2.2 | Quantitative Synchronizer Performance Comparison.                    | 26  |

| 5.1 | Values of x and L for nominal rho in a narrow recommended range      |     |

| 5.2 | Required tolerances when restricting rho to a narrow range           | 114 |

| 6.1 | Spectral Frequencies for Time Interval Measurement                   | 126 |

| 6.2 | Spectral Amplitudes for Time Interval Measurement                    | 126 |

| 6.3 | Spectral Frequencies for Time Deviation Measurement                  | 128 |

| 6.4 | Spectral Amplitudes for Time Deviation Measurement                   | 128 |

| 6.5 | Settings of Jitter Spectrum Experiments with Sinusoidal Input Jitter | 132 |

| 6.6 | Results of Jitter Spectrum Experiments with Sinusoidal Input Jitter  | 132 |

The term synchronization refers to the aligning of the timing instants of one signal to the timing instants of another signal. In synchronous digital systems, for example, all operations within the system are synchronized to the edges of the system clock. The synchronization to the system clock provides a known constraint on the timing of events within the system which greatly simplifies the design, test and functioning of the system. The thesis presents original work on various aspects of synchronization.

In digital communications networks, recovery of the transmitted information is dependent upon accurate timing linked to the data in order to decode correctly the stream of bits. Due to the large distances frequently encountered in communications systems, the issue of synchronization becomes even more important.

Digital systems are rarely useful if they operate in total isolation. They therefore must be able to accept inputs from external autonomous sources. These external inputs will be asynchronous to the digital system clock, that is, there is no relationship between the frequency and phase of the input and the system clock. For the digital system to be able to use the input, it must be synchronized into the timing domain of the system clock.

Bistable devices are frequently used to synchronize the inputs in digital systems. The presence of an asynchronous input means that the constraints on input timing of a bistable device cannot always be observed [15], [34], [42]. As a result, a state may result in which the output of the device becomes logically undefined, for a time that is long compared to the normal switching delay of the device [16], [17], [31]. This state is referred to as a metastable state. Metastable failure of bistable devices is important not only due to the excess settling delay but also because of the possibility of propagation of an undefined logic level within the system and inconsistent interpretation of the device output by other devices in the system [34], [55].

To control the problem of metastable failure within systems, synchronizers have been adopted as an interface between the asynchronous input and the synchronous system. The synchronizer samples the asynchronous input typically at the rate of the system clock. The output of the synchronizer is thus synchronous with the rest of the system. The synchronizer is designed to reduce the probability of metastable failure to an acceptable level, but it cannot eliminate it altogether.

Digital systems, including communications systems, are susceptible to errors caused by the misidentification of the significant instants of a signal. Jitter is said to affect the signal when the significant instants of a signal vary from their ideal positions in time. Jitter may cause bit errors, unwanted phase modulation after conversion back to an analog signal [8], or corruption of data if data buffers overflow or underflow. In digital communications systems there are many potential sources of jitter: for example, jitter arising in clock recovery in repeaters, wander (low frequency jitter) arising due to variations in transmission link delays, and jitter arising as result of synchronization processes in multiplexers [8], [13].

## 1.1 Motivation and Applications

### 1.1.1 External Timing Source Injection for an ATM LAN

The Co-operative Research Centre for Broadband Telecommunications Networks (CRC-BTN) has been involved in the development of an ATM LAN (Asynchronous Transfer Mode Local Area Network), based on extensions of the DQDB (Distributed Queueing Dual Bus) protocol which is the basis of the 802.6 MAN (Metropolitan Area Network) Standard [4]. The author participated in the project and studied aspects of network timing distribution for the ATM LAN.

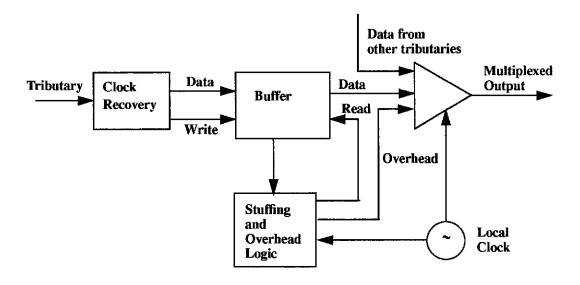

A key feature of the DQDB network used in the ATM LAN is the use of autonomous nodes with independent clocks [4] which prevents the build-up of bit-level jitter due to link level clock recovery [52]. The clocks in such a network will be plesiochronous, that is with different frequencies within a certain tolerance of a nominal rate. Without synchronization, the average rate of data input to a buffer within a node will not be the same as the average data output rate leading to corruption of data due to buffer overflow or underflow. The same problem arises, for example in the asynchronous time division multiplexing used in the Plesiochronous Digital Hierarchy (PDH). In the PDH, the required synchronization of the plesiochronous lower rate tributaries is accomplished locally at the telecommunications node using a timing adjustment mechanism known as pulse stuffing or justification [7], [47]. The stuffing algorithm used in the ATM LAN is based on the constrained stuffing algorithm used in the DQDB [63] and can lead to a build-up of frame level jitter.

Although the nodes in the ATM LAN have autonomous clocks, a common timing reference is still required to enable the provision of certain services such as constant bit rate (CBR) services. The timing reference is carried by the framing signal. However, the build-up of frame-level jitter, containing undesirable low frequency components, makes provision of a high quality reference difficult.

The timing reference is usually derived from an external timing source (XTS) to generate a clean frame. If the reference is supplied by a public network, there is the additional advantage that information exchange with the public network becomes possible.

To inject the XTS, the frame timing must be locked to the XTS. Conventionally, the synchronization of the frame timing would be accomplished using a justification or stuffing approach. The conventional approach is complex, requiring a buffer and control blocks to monitor stuffing. As the XTS is asynchronous to the local clock of the node, a synchronizer must still be used in the conventional implementation. A simpler method of XTS injection combines the generation of a clean frame and synchronization in a single operation. In this thesis, new high performance synchronizer designs are presented and analysed [60], [61]. The need for managing metastability is a more widespread problem and is inherent in all synchronization processes as will be evident when timing transfer over an ATM network is considered.

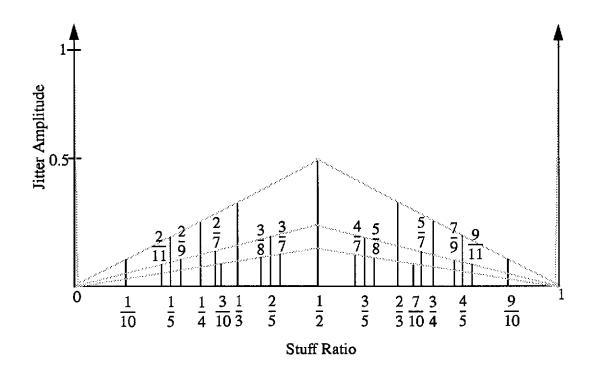

The first investigations of the jitter generated by synchronization processes followed the introduction of pulse stuffing synchronization for digital multiplexing in the PDH. In pulse stuffing, certain locations within the data stream carry data bits or dummy 'stuff' bits as required to vary the tributary rate [47]. An important parameter is the stuff ratio which expresses the average rate of stuffing as a proportion of the maximum rate of stuffing, usually the frame rate. The most problematic jitter component produced by pulse stuffing synchronization is waiting time jitter which can be at arbitrarily low frequency and thus cannot easily be removed by a desynchronizer [22], [47].

Kuroyanagi et al. [35] used the value of the stuff ratio in the PDH to find the dominant frequency and peak-to-peak amplitude of the waiting time jitter. They also plotted the

so-called classical characteristic of the waiting time jitter, plotting the stuff ratio vs. the peak-to-peak jitter amplitude.

The spectrum of waiting time jitter was first derived by Duttweiler [22] by applying random process theory to waiting time jitter waveforms. Duttweiler's approach made simplifying assumptions about the operation of the phase detector [19], [47]. Some more detailed analysis [19], [20] suggests that the actual jitter generated in PDH multiplexing depends on the precise frame format, the buffer size and the phase detector implementation. The resulting filtered waiting time jitter amplitude may be less than that predicted by the ideal case. The effect of phase detector implementation was also investigated experimentally by Cock et al. [21]. Other methods of deriving the spectrum exist, for example, decomposition of the waiting time jitter waveform [56] and analysis of the phase waveforms at the buffer [10], [48]. The spectrum of the jitter generated by the constrained stuffing algorithm used in the 802.6 DQDB network [4] was derived by Warner [63].

In this thesis, the jitter generation inherent in XTS injection is characterized. Two different methods of accomplishing the XTS injection, are analysed using a new time domain approach developed by the author which yields exact expressions for frame-level jitter [62].

## 1.1.2 Synchronous Residual Time Stamp (SRTS) Timing Transfer

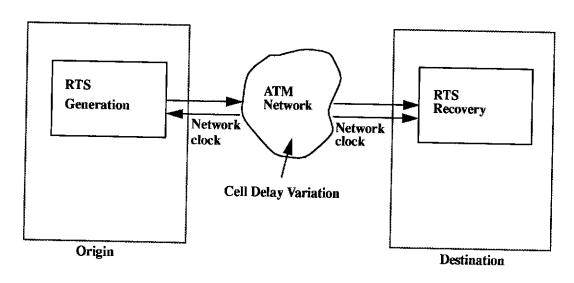

The Synchronous Digital Hierarchy (SDH) and SONET (Synchronous Optical Network), will be the underlying transmission network of the Broadband Integrated Services Digital Network (B-ISDN) [11], [37]. ATM is the preferred protocol for the transport of all kinds of traffic in the new B-ISDN [44]. The AAL1 (ATM Adaptation Layer 1) performs the functions necessary to allow CBR services to be transported in ATM cells, including encoding and transporting the CBR service clock. One of the methods accepted for end-to-end timing transfer in the AAL 1 is the Synchronous Residual Time Stamp (SRTS) [5] which makes use of the presence of a common network clock at the origin and destination.

It has been suggested that the jitter which is an inherent characteristic of the SRTS method of frequency encoding, is analogous to the waiting time jitter generated by

conventional pulse stuffing [37], [46], [57]. Lau and Fleischer [37] and Uematsu and Ueda [57] use the approach of [35] to deduce the jitter amplitude. [46] uses a piecewise linear approximation to the resulting time-varying frequency of the reconstructed timing signal at the destination to find an approximation to the spectrum. However, a formal derivation of the jitter spectrum associated with SRTS method timing transfer has not been provided.

In applications where waiting time jitter occurs, the stuff ratio is chosen so that the peak-to-peak amplitude of the waiting time jitter is small, for example, the telecommunications multiplexing hierarchies have been designed with values of the stuff ratio in the range (0.41, 0.44) [7].

In this thesis, the jitter characteristics of the SRTS method are derived. Original analysis by the author is used to determine whether it is possible to specify parameters of the SRTS method so as to reduce the amplitude of the waiting time jitter.

### 1.2 Contributions

Within the fields of synchronization, jitter analysis and metastability, the author has made the following contributions which are reported in this thesis:

- (i) The development and analysis of three new synchronizer designs and the determination of their metastable failure performance.

- (ii) A new time domain approach to jitter analysis, used to find exact expressions for frame-level jitter in a conventional approach to external timing source injection.

- (iii)The analysis of a new method of external timing source injection showing that the jitter spectrum is equivalent to waiting time jitter. The new time domain approach to jitter analysis has also been applied to the SRTS method establishing formally that waiting time jitter is an inherent characteristic of this method of timing transfer.

- (iv) A new, more direct and easily verifiable approach to the regeneration at the destination of the SRTS timing signal has been developed, analysed and simulated.

(v) It has been shown that it is not possible, in general, to choose the equivalent of the stuff ratio in the SRTS method in order to minimise the amplitude of the waiting time jitter generated in this method.

- (vi)Extension of the new time domain approach to include analysis of the jitter spectrum in the presence of input jitter.

- (vii)The jitter model developed has been experimentally verified, showing that the jitter spectrum conforms to the predictions, both with and without input jitter.

Much of the above work has also been reported by the author [60]-[62] as listed below:

- J. Walker and A. Cantoni, "A New Design for a Frame Sampling Synchronizer", in *Proc. IEEE Int. Symp. Circuits and Systems*, London, vol. 3, pp. 97-100, June 1994.

- J. Walker and A. Cantoni, "A New Synchronizer Design" *IEEE Trans. Comput.*, vol. 45, no. 11, pp.1308-1311, Nov. 1996.

- J. Walker and A. Cantoni, "Jitter Analysis for Two Methods of Synchronization for External Timing Injection", *IEEE Trans. Commun.*, vol. 44, no. 2, pp. 269-276, Feb. 1996.

#### 1.3 Outline of the Thesis

In Chapter 2, a brief overview of the problem of metastable failure is given including a summary of some useful models and metastable failure probability equations. Synchronizer design is the main focus of this chapter. Three new synchronizer designs are presented and their performance compared with that of existing synchronizer designs.

In Chapter 3, an introduction to jitter is first given, covering a range of topics in jitter modelling and analysis which are of relevance to later chapters. The analysis of the jitter equation of the synchronization process is then presented and techniques for Fourier analysis of jitter are applied to derive the jitter spectrum of the synchronization process. Finally, the analysis of the jitter equation of the

7

synchronization process is extended to determine the jitter spectrum in the presence of input jitter.

One application of synchronization is external timing source injection. Chapter 4, begins with an introduction to timing adjustment, jitter and the use of external timing sources in networks. Two different approaches to external timing source injection are then studied and the spectrum of the jitter generated by each is determined. Finally, the results of the jitter analyses for the two approaches are compared and shown to be equivalent to waiting time jitter. Issues relating to waiting time jitter and how the choice of the stuff ratio can minimise the waiting time jitter amplitude are then reviewed.

A second application of synchronization is the Synchronous Residual Time Stamp (SRTS) method of end-to-end timing transfer. Chapter 5 begins with a detailed introduction to the SRTS method, including presentation of a new method for destination timing signal recovery. A model of the SRTS method is developed and the spectrum of the jitter inherent to the SRTS method is derived, showing that it is equivalent to waiting time jitter. Finally, the question of whether it is possible to specify parameters of the SRTS method so as to reduce the amplitude of the waiting time jitter is studied in detail.

In Chapter 6, an experimental investigation into the jitter spectrum of the synchronization process is described. A brief description of the experimental approach is given and then the experimental results are compared with the theoretical predictions of the jitter spectrum both with and without input jitter. Finally, the question of whether sinusoidal input jitter might be useful in the suppression of unwanted waiting time jitter is briefly examined.

In Chapter 7, suggestions for further work are made.

Each chapter is followed by a number of appendices, the first of which contains a Glossary relevant to that chapter. Subsequent appendices contain the derivations of the key results found in the chapter.

### 2.1 Introduction

Systems which have asynchronous inputs will inevitably suffer from problems due to the phenomenon of metastability [15], [34], [42]. Any design for a synchronizer should take into account the possibility of metastability and be designed to cap the probability of metastable failure to an acceptable level.

This chapter presents new synchronizer designs and compares their performance to existing synchronizers. In Section 2.2, a brief overview of the problem of metastable failure is given including a summary of some useful models and metastable failure probability equations. In Section 2.3, three new synchronizer designs are presented [60], [61] which are shown to have significant advantages over previous designs.

#### 2.2 The Problem of Metastable Failure

Bistable devices are frequently used to synchronize the inputs in digital systems. For correct operation, a bistable device such as a latch or a flip-flop has certain constraints on the timing of its inputs. For example, the input of a D-type flip-flop must be established for a certain minimum time before the clock edge (setup time) and must be held for a certain minimum time after the clock edge (hold time). Similar constraints on minimum pulse width and minimum pulse separation apply to the signals applied to the R and S inputs of a RS flip-flop.

If the timing constraints are not observed, the output of the device may become logically undefined, lingering between the two stable defined states of the device. When the output of a bistable device exhibits such behaviour, the device is said to be in a metastable state [16], [17], [31]. The invalid logic level may persist for a time that is long compared to the normal switching delay of the device [16], [17]. In certain device types, the metastable state may be characterized by oscillatory behaviour [17], [31], [50] which lasts for a time long in comparison to normal logic delays.

Metastable failure of bistable devices is an important issue in digital system design, not only because of the excess settling delay. When metastable failure occurs in a device, other components of the system which use the output of the failed device may propagate an undefined level in the system or may interpret the output inconsistently which can then cause malfunctions within the system [34], [55].

It has been shown mathematically that metastability cannot be avoided when bistable digital systems have inputs which are asynchronous to each other [33], [40]. The fundamental equivalence of the different kinds of circuits which operate with asynchronous inputs such as the synchronizer, the arbiter, the latch and the inertial delay has also been demonstrated [12].

With metastability acknowledged as an unavoidable problem, the focus of research has turned to other aspects: characterization and modelling of the metastable state [26], [32], [34], [50], [59]; detailed analysis and simulation of metastable behaviour in different kinds of bistable devices, such as the CMOS RS flip-flop [29], [30], the CMOS D latch [28], CMOS ASIC flip-flops [27]; design methods for reducing the probability of metastable failure either at the component [27], [28], [51] or the system level [34], [39], [54], [55]; and to ways of measuring the failure rate of bistables [23], [27], [51] or calculating the probability of system failure due to its occurrence [26], [31], [34], [59].

Several different approaches have been used to model the metastable behaviour of bistable devices: theoretical models where the device is modelled as a simple regenerative loop [49], [59]; experimental studies [23], [51] and simulation studies [26], [32]. The resulting model is of a two stage process. The first phase, known as the sampling phase, is brought to an end as the regenerative loop closes. The device is triggered into metastability when the separation between clock and data edges at the end of the sampling phase falls within the metastable window. Once metastability is triggered, the resolution of the device outputs to one or other valid stable state during the regeneration phase follows an exponential path. Some details of the metastable window and the resulting probability expressions are briefly summarised in Appendix 2B.

To control the problem of metastable failure within systems, synchronizers have been adopted as an interface between the asynchronous input and the synchronous system. The synchronizer samples the asynchronous input at the rate of the system clock. The output of the synchronizer is thus synchronous with the rest of the system. The synchronizer is designed to provide an increased settling time before the sampled asynchronous input is presented to the rest of the system. However, the use of a synchronizer does not eliminate the possibility of metastable failure. When the

synchronizer fails, the problems associated with metastability will occur and can affect the system. It is therefore important both to develop synchronizer designs which reduce the probability of metastable failure to an acceptable level and to assess the performance of the designs using metastable failure probability models.

# 2.3 Synchronizer Designs and their Assessment

In this section, three new synchronizer designs first reported by the author in [60], [61] are described and their performance compared with that of existing synchronizer designs. The section begins with a description of the framework in which the synchronizers will be compared. Existing synchronizer designs are then briefly described. Then, the new synchronizer designs are presented and analysed. The section concludes with a comparison of the performance of the different designs.

### 2.3.1 A Framework for Assessment of Synchronizer Performance

The four performance indices used to compare the synchronizer designs are: the MTBF (mean time between failure), the data delay time, the data sampling rate and the complexity. The MTBF for the desired clock period and flip-flop characteristics gives the reliability of the design and is a function of the settling time,  $T_s$ , allowed by the synchronizer. Failure of a synchronizer will be defined to occur when the output flip-flop samples a metastable state at its input, where the output flip-flop is the flip-flop which interfaces directly with the system where the synchronizer is used.

The total data delay time,  $T_d$ , gives a measure of the efficiency of the synchronizer by indicating how much delay is required as a trade-off for the MTBF. The data sampling rate depends on the system clock rate and the design of the synchronizer. The complexity of the synchronizer design is represented by the number of flip-flops in the design.

The current model of metastable failure for bistable devices, as summarised in Appendix 2B, allows the calculation of metastable failure probabilities and MTBF. The model is developed on the basis of a single loop only, however, experimental work [27], [51] suggests that the equations still apply asymptotically to the more complicated circuits present in real devices. When attempting to predict the

performance of synchronizers made of many flip-flops, the model can still be used but it is necessary to model how metastability is transferred between devices.

There are at least two approaches to modelling the transfer of metastability from one device to the next [34], [49]. In the performance assessment of the synchronizers in the following sections, the sampling model [34] will be used. In the sampling model, it is assumed that the transfer of metastability occurs by simple sampling because, while a metastable state is resolving, the device is in its linear region of operation. In this first-order linear model, the metastable state is assumed to resolve progressively as it passes from device to device. The model is simple but requires the assumption that the devices have identical parameters and that the device behaviour while resolving is monotonic. It also does not allow for further metastable triggering in the second and subsequent devices.

### 2.3.2 Existing Synchronizer Designs

The shift register synchronizer [34], which uses a chain of N+1 flip-flops, is illustrated in Figure 2.1. The timing diagram for the shift register synchronizer is in Figure 2.2 and shows that it provides a settling time,  $T_s$ , of

$$T_s = NT_c - (N-1)t_{pd} (2-1)$$

where  $T_c$  is the system clock and  $t_{pd}$  is the propagation delay of a flip-flop. The propagation delays of the internal N-1 flip-flops are deducted from the settling time, because it is only in these flip-flops that the simple sampling transfer of the resolving metastable state is assumed to occur.

Figure 2.1: A shift register synchronizer.

Metastability

Figure 2.2: Timing diagram for the shift register synchronizer when N=2.

The MTBF is given by [34]

$$\frac{T_c e^{\frac{NT_c - (N-1)t_{pd}}{\tau}}}{\lambda \Delta t_{max}}$$

(2-2)

The data delay time of the shift register synchronizer is

$$T_d = NT_c \tag{2-3}$$

The second design to be discussed in this section is the divided clock synchronizer [34], illustrated in Figure 2.3, which uses three flip-flops and a divided clock. A timing diagram for the divided clock synchronizer is in Figure 2.4.

Figure 2.3: A divided clock synchronizer.

Figure 2.4: Timing diagram for the divided clock synchronizer for N=3.

The use of the divided clock in this synchronizer design means that most of the settling time is between the first and second flip-flops thus reducing the need for a long chain of flip-flops in order to provide a long settling time [34]. The settling time,  $T_s$  is,

$$T_s = NT_c - t_{pd} - t_{di} ag{2-4}$$

where  $t_d$  is the delay in the clock divider circuit. Note that only the propagation delay of the second flip-flop, where the resolving metastable state is assumed to be transferred by simple sampling, is deducted from the settling time.

The MTBF is given by [34]

$$\frac{(N-1)T_c e^{\frac{NT_c - t_{pd} - t_{di}}{\tau}}}{\lambda \Delta t_{max}}$$

(2-5)

and the data delay time is

$$T_d = NT_c - t_{di} (2-6)$$

### 2.3.3 Three New Synchronizer Designs

This section presents three new synchronizer designs, the first two of which were described by the author in [60], [61], and which represent distinct implementations of a basic synchronizer structure. The first has an asynchronous front end and is termed the AFE synchronizer. The second has a synchronous front end and is termed the SFE synchronizer. The third uses a new flip-flop design in a synchronous front end and is termed the SFE-NFF synchronizer.

### 2.3.3.1 The Asynchronous Front End Synchronizer

Figure 2.5 shows the AFE synchronizer. The design consists of four blocks: a sequential sampling register, a multiplexer, an output flip-flop and a timing generator. The sequential sampling register has N+1 independent flip-flops which all see the same asynchronous input, but are clocked cyclically. Each flip-flop within the sequential sampling register is clocked at 1/(N+1) the rate of the clock. Viewing the sequential sampling register as a whole, samples are taken at the clock frequency, but each successive sample is taken by a different flip-flop.

Figure 2.5: The new AFE synchronizer.

The N+1 outputs of the flip-flops are connected to the multiplexer together with N+1 corresponding select signals. The select signals are phased with respect to the flip-flop strobe by the timing generator, so that a given flip-flop's output is not selected until it has had N clock periods to settle. In this respect the design resembles the divided clock synchronizer. However, the multiplexer presents the delayed samples to the output flip-flop at the same rate as the samples are taken. This is a key difference with respect to the divided clock synchronizer which only samples the input every N-1 clock periods. The output flip-flop is clocked synchronously with the clocking of the flip-flops in the sequential sampling register. Figure 2.6 shows the timing diagram for the AFE synchronizer shown in Figure 2.5.

Figure 2.6: Timing diagram for AFE synchronizer.

Figure 2.7 shows the detail of a possible implementation of the timing generator. The shift register and nand gate combination is self-starting and circulates a zero through the shift register thus generating the cycle of N+1 successive pulses for the strobe and select signals.

Figure 2.7: Possible implementation of the timing generator.

For the ith pathway through the AFE synchronizer, the settling time is calculated beginning from the clock edge at the ith input flip-flop, that is the ith strobe, to the clock edge at the output flip-flop, that is the inverted clock, as shown in the timing diagram of Figure 2.6. Hence, the settling time for the AFE synchronizer is given by

$$T_{s} = NT_{c} + \frac{T_{c}}{2} + t_{pi} - t_{ptg} - t_{pmux}$$

(2-7)

where  $t_{pi}$  is the propagation delay of the inverter which produces the inverted clock,  $t_{ptg}$  is the propagation delay of the timing generator in producing the strobe and select signals (assumed to be identical in all cases) and  $t_{pmux}$  is the propagation delay in the multiplexer, which is assumed not to be part of the settling time in a similar way that the propagation delay through the internal flip-flops was excluded in the previous designs.

The MTBF for the AFE synchronizer is given by

$$\frac{T_c e^{\frac{NT_c + T_c/2 + t_{pi} - t_{plg} - t_{pmux}}{\tau}}}{\lambda \Delta t_{max}}$$

(2-8)

For the ith pathway through the synchronizer, the data delay time is calculated beginning from the clock edge at the ith input flip-flop, that is the ith strobe, to the clock edge at the output flip-flop, that is the inverted clock, as shown in the timing diagram of Figure 2.6. Hence, the data delay time for the AFE synchronizer design is given by

$$T_d = NT_c + \frac{T_c}{2} + t_{pi} - t_{ptg} (2-9)$$

### 2.3.3.2 The Synchronous Front End Synchronizer Designs

In VLSI implementation, for ease of testing, it is preferable to use purely synchronous designs, for example, this simplifies the use of the scan path methodology. Two implementations of the synchronous front end synchronizer are presented in this section. The basic structure of the synchronizer remains the same as described for the AFE synchronizer in Section 2.3.3.1. A possible alternative and synchronous implementation of the synchronizer front end, as seen in the SFE synchronizer, is in Figure 2.8 and the corresponding timing diagram is shown in Figure 2.9.

#

Figure 2.8: The front end of the new SFE synchronizer design.

In the SFE synchronizer, the enable takes the place of the strobe and is activated cyclically at 1/(N+1) the clock rate, routing the asynchronous input to the input of each flip-flop in turn. The flip-flops are clocked at the clock rate, thus although each flip-flop only samples the asynchronous input once every N+1 clock cycles, a sample is taken of the asynchronous input on every clock edge. When the enable input of a particular flip-flop is not activated, the output of that flip-flop is routed to its input. Thus, at every clock edge while its enable is not active, the flip-flop resamples its own output. For testing purposes the front end can be converted to a scan register. The timing of the data input can be forced to satisfy the necessary set-up and hold time requirements during testing.

Figure 2.9: Timing diagram for SFE synchronizer.

The SFE synchronizer design is analogous to a shift register synchronizer with the first N flip-flops in the chain being exactly the same flip-flop. The settling time is calculated from the clock edge at the ith input flip-flop to the clock edge at the output flip-flop. As all the flip-flops are clocked by the same clock edge, the settling time is simply N clock periods minus the propagation times through the multiplexer and the internal flip-flops, which in this design is caused by the repeated clocking of a single input flip-flop when the input is not enabled. Hence,  $T_s$  is given by

$$T_s = NT_c - (N-1)t_{pd} - t_{pmux}$$

(2-10)

The MTBF for the SFE synchronizer is given by

$$\frac{T_c e^{\frac{NT_c - (N-1)t_{pd} - t_{pmux}}{\tau}}}{\lambda \Delta t_{max}}$$

(2-11)

The data delay time is calculated from the clock edge at the ith input flip-flop to the clock edge at the output flip-flop. As all the flip-flops are clocked by the same clock edge, the data delay time is simply N clock periods.

$$T_d = NT_c \tag{2-12}$$

A further interesting question about the implementation of the synchronous front end is the use of the flip-flop with an enable. In the analysis above it has been assumed that the implementation involves a simple multiplexer arrangement where the enable selects between the flip-flop input and the fed back flip-flop output as shown in Figure 2.8. Another possibility is shown in Figure 2.10, where the flip-flop uses the R-S latch design [14]. The SFE-NFF synchronizer is the synchronous front end implementation of the new synchronizer built with this new enable flip-flop.

Metastability may be triggered in the output latch of this flip-flop when the clock and data inputs occur too close together resulting in either the R or the S input being of a critical width [49]. Once the enable is low and the input is no longer selected, further access to the resolving latches during subsequent clock pulses is blocked. Neither the input nor the output of the flip-flop nor the clock can affect the resolving output latch of the flip-flop. For the output flip-flop to sample metastability, the input flip-flop must remain metastable for  $NT_c$ . Hence the MTBF for the SFE-NFF synchronizer is

$$\frac{T_c e^{\frac{NT_c}{\tau}}}{\lambda \Delta t_{max}} \tag{2-13}$$

where the data delay time is given by (2-12).

Figure 2.10: Alternative enable flip-flop implementation.

## 2.3.4 Comparison of the Synchronizer Designs

As described in Section 2.3.1, the four indices of synchronizer performance are MTBF, data delay time, sampling rate and complexity. For the comparison of the different synchronizer designs to be fair, it has to be made for settling times which are the same number of system clock cycles, for a given value of N. Comparison between different MTBFs will then give an indication of the influence of the synchronizer design on the MTBF. For a given value of N, synchronizer complexity and sampling rate may vary and these other factors may need to be weighed against the MTBF.

In Table 2.1, expressions are given for the MTBF and data delay time using the shift register synchronizer as the basis for comparison. From these expressions, it can be seen that designs which do not propagate the settling metastable state through successive devices enjoy an improved MTBF. The AFE synchronizer has an additionally improved MTBF due to an extra half of a system clock period resulting from the clocking scheme used. However, as a result, the AFE synchronizer suffers from a penalty in the data delay time. The SFE synchronizer, however, has a worse

MTBF than the shift register synchronizer due to the additional propagation delay through the multiplexer stage.

| Synchronizer<br>Type    | $\frac{MTBF}{MTBF_{SR}}$ a                                      | $\frac{T_d}{T_{d,SR}}$ b                            | Sampling<br>Rate  | Number of<br>Flip-flops |

|-------------------------|-----------------------------------------------------------------|-----------------------------------------------------|-------------------|-------------------------|

| Shift<br>Register       | 1                                                               | 1                                                   | $f_c$             | N+1                     |

| Divided<br>Clock        | $(N-1)e^{\frac{(N-2)t_{pd}-t_{di}}{\tau}}$                      | $1 - \frac{t_{di}}{NT_c}$                           | $\frac{f_c}{N-1}$ | 3                       |

| AFE Synchronizer        | $e^{\frac{T_c}{2} + (N-1)t_{pd} + t_{pi} - t_{plg} - t_{pmux}}$ | $1 + \frac{\frac{T_c}{2} + t_{pi} - t_{ptg}}{NT_c}$ | $f_c$             | N+2                     |

| SFE Synchronizer        | -t <sub>ртих</sub><br>е т                                       | 1                                                   | $f_c$             | N+2                     |

| SFE-NFF<br>Synchronizer | $e^{\frac{(N-1)t_{pd}}{\tau}}$                                  | 1                                                   | $f_c$             | N+2                     |

**Table 2.1: Synchronizer Performance Comparison**

The comparisons are evaluated in Table 2.2. In order to accommodate the clock division in the divided clock synchronizer, the minimum value of N for which the performance comparison can be made is N=3. When computing the ratios, it is necessary to assume that the shift register synchronizer and the design with which it is being compared are built with the same type of flip-flop. For the divided clock synchronizer and the AFE synchronizer, 74HC D type flip-flops are assumed with the following parameters  $t_{pd}=16$  ns,  $\tau=1.3$  ns, the clock divider has  $t_{di}=15$  ns and the system clock period is  $T_c=100$  ns [49]. The other delay terms are assumed to be 74AC components with  $t_{pi}=1.7$  ns,  $t_{ptg}=12.3$  ns,  $t_{pmux}=13$  ns where the delays have been assumed to be worst case, that is, to reduce the MTBF. For the comparison with the SFE synchronizer, it is only necessary to assume that it and the shift register synchronizer be built of the same type of flip-flop. For comparison with the SFE-NFF synchronizer, it is not necessary to assume that the shift register synchronizer is built with the new type of flip-flop.

a.  $MTBF_{SR}$  Mean time between failure of the shift register synchronizer.

b.  $T_{d-SR}$  Data delay time of the shift register synchronizer.

Table 2.2: Quantitative Synchronizer Performance Comparison.

| Synchronizer<br>Type    | $\frac{MTBF}{MTBF_{SR}}_{a}$ $N = 3$ | $\frac{T_d}{T_{d,SR}}_{\mathbf{b}}$ $N = 3$ | $\frac{MTBF}{MTBF_{SR}}$ $N = 9$ | $\frac{T_d}{T_{d, SR}}$ $N = 9$ |

|-------------------------|--------------------------------------|---------------------------------------------|----------------------------------|---------------------------------|

| Shift<br>Register       | 1                                    | 1                                           | 1                                | 1                               |

| Divided<br>Clock        | 4.32                                 | 0.95                                        | 2.03×10 <sup>33</sup>            | 0.98                            |

| AFE Synchronizer        | 3.23×10 <sup>19</sup>                | 1.13                                        | 3.81×10 <sup>51</sup>            | 1.04                            |

| SFE Synchronizer        | 4.54×10 <sup>-5</sup>                | 1                                           | 4.54×10 <sup>-5</sup>            | 1                               |

| SFE-NFF<br>Synchronizer | 4.9×10 <sup>10</sup>                 | 1                                           | 5.77×10 <sup>42</sup>            | 1                               |

a.  $MTBF_{SR}$  Mean time between failure of the shift register synchronizer.

Table 2.2 confirms that the designs which do not require propagation through many cascaded devices are expected to perform better. The divided clock synchronizer is only slightly better than the shift register synchronizer for small N but the effect of delays such as  $t_{di}$  on the MTBF is overcome for larger values of N. However, as N increases there is a penalty in the 1/(N-1) times lower sampling rate.

The AFE and SFE-NFF synchronizers have better performance for a given N, than the shift register synchronizer, but are much more complex in design. The shift register synchronizer may still be designed to a desired MTBF and may be favoured because it is simpler. However, to characterize a practical realization of the shift register synchronizer is difficult. The simple sampling model of metastability transfer which has been assumed is a simplification and real systems may introduce additional dynamics between the devices. It also assumes that all flip-flops in the chain have identical parameters, whereas in a real system this may not be the case.

The SFE synchronizer overcomes one of these problems because it is equivalent to a shift register synchronizer with the first N flip-flops in the chain being the same flip-flop, hence the assumption that the flip-flop parameters are identical is valid. The

b.  $T_{d,SR}$  Data delay time of the shift register synchronizer.

slightly worse performance than the shift register synchronizer may be overcome by using a fast multiplexer stage and acceptable performance can still be obtained by selecting an appropriate value of N.

Although the new designs use more flip-flops and are more complex in their design, they provide much better performance. Their main advantage however, lies in the greater reliance which can be placed on the MTBF calculation. Manufacturers provide data for the flip-flop parameters  $\tau$  and  $\Delta t_{max}$  under the assumption that the flip-flops will be used in a simple two flip-flops synchronizer [1], [2]. In calculating the MTBF for the simple two flip-flops synchronizer, assumptions about metastability transfer are not required as failure is defined to occur if the second flip-flop samples a metastable state. The determination of the MTBFs for the AFE synchronizer and for the SFE-NFF synchronizer also makes no assumptions about metastability transfer between flip-flops nor places any requirement on flip-flops in the design to be closely matched. Characterization reduces to considering a pair of synchronizing flip-flops and the parameters of the worst case sampling flip-flop can be used. Thus, these designs can provide an acceptable performance with a greater certainty that the actual performance will correspond to the predicted performance.

## **Appendix 2A: Glossary**

$t_d$  - delay time before loop output reaches a valid logic level

$t_{pd}$  - normal propagation delay of a flip-flop

$t_m$  - delay value defining metastable failure

$\Delta t_{max}$  - maximum size of metastable window

$\lambda$  - mean rate of arrival of data edges (Poisson process) in probability model of metastability

$\tau$  - regeneration time constant in probability model of metastability

$T_c$ ,  $f_c$  - system clock period and system clock rate

$T_s$  - settling time allowed for synchronizer output to resolve

$T_d$  - data delay time in a synchronizer

$t_{di}$  - propagation delay of clock divider circuit in divided clock synchronizer

$t_{pi}$  - propagation delay of inverter in new synchronizer designs

$t_{ptg}$  - propagation delay of timing generator in new synchronizer designs

$t_{pmux}$  - propagation delay of multiplexer in new synchronizer design

### Appendix 2B: Metastable Failure Probability Equations

This appendix gives the equations which describe the probability of metastable failure in bistable devices [31], [34], [39], [49].

Metastable failure is defined as the failure of a device to resolve by some time  $t_m$ , which is the time available for its output to settle before the output is required by other devices in a system.

The metastable failure probability  $P(t_d > t_m)$ , the probability that the delay time of the latch is greater than some value  $t_m$ , is given by [49]

$$P(t_d > t_m) \approx \lambda \Delta t_{max} e^{-\left(\frac{t_m - t_{pd}}{\tau}\right)}, t_m > t_{pd}$$

(2B-1)

where it is assumed that the arrival times of the data edges are determined by a Poisson process with a mean rate of arrival of edges given by  $\lambda$ . (2B-1) says that the probability of metastable failure is approximately equal to the mean rate of arrival of data edges multiplied by the size of the metastable window corresponding to the desired delay time of  $t_m$ .

If it is assumed that the probability of metastable failure is an independent probability in each clock period then it is possible to calculate the mean time between failure (MTBF) for a given settling time,  $T_s$ , as [34], [49]

$$MTBF = \frac{T_c e^{\frac{T_s}{\tau}}}{\lambda \Delta t_{max}}$$

(2B-2)

where  $T_c$  is the clock period.

## Chapter 3

## Jitter

#### 3.1 Introduction

In digital systems, the value of signals matters only at particular instants in time. For example, digital transmission link repeaters regenerate the signal based on the detection of each bit at a significant instant set by the associated (recovered) clock. Digital systems are susceptible to errors caused by the displacement of the significant instants of a signal. The disturbance which causes the significant epochs of a signal to vary from their ideal positions in time is known as jitter.

The errors caused by jitter are not confined to bit errors, as may occur in digital repeaters when there is excessive jitter. Jitter on digital data which is to be converted back into analog form may cause unwanted phase modulation on the resulting analog signal [8]. Variations in rates of writing or reading a buffer due to jitter on clock signals can cause buffer slips leading to loss of data.

The purpose of this chapter is to provide an introduction to jitter, covering a range of topics in jitter modelling and analysis which are of relevance to later chapters. In Section 3.2, time jitter is formally defined and the necessary framework and models for describing jitter are presented. Phase jitter is introduced in Section 3.3 and the question of when time jitter can be approximated using phase jitter is explored. Section 3.4 presents the analysis of an important class of jitter recurrence equation, the jitter equation of the synchronization process, which has been analysed for the first time by the author [60], [62]. In Section 3.5, techniques for Fourier analysis of jitter are developed and applied to the analysis of the jitter spectrum of the synchronization process. In Section 3.6 the analysis of the jitter equation of the synchronization process is extended to include input jitter and the spectrum of the synchronization process jitter in the presence of input jitter is derived in Section 3.7.

#### 3.2 Jitter - Definitions, Framework and Modelling

#### 3.2.1 Definition of Time Jitter

Time jitter is defined as the difference between the ideal position of the significant edge of a signal and its actual position as shown in Figure 3.1. If a jittered pulse is delayed with respect to the ideal pulse, the time jitter is positive; if it precedes the

corresponding ideal pulse then the time jitter is negative. The time jitter values are defined at the regular time instants of the ideal signal and are thus discrete in time but continuous in amplitude. Such a discrete time sequence can be viewed as samples of a continuous time jitter function e(t) at times  $t = nT_c$ .

Figure 3.1: Definition of time jitter

As time jitter has dimensions of time, a time jitter function will be denominated in seconds and the derivative of a time jitter function will be dimensionless. It is also possible to consider normalised time jitter where the time jitter is normalised to the period of the ideal signal, for example, for the time jitter samples  $e(nT_c)$

$$\hat{e}(nT_c) = \frac{e(nT_c)}{T_c} \tag{3-1}$$

Clearly, the normalised time jitter is dimensionless.

The amplitude of jitter is often referred to in unit intervals. The unit interval is a way of normalising the jitter amplitude to the period of the ideal or reference signal. When dealing with jitter on a particular signal, the unit interval is defined to be equal to the ideal period of that signal and the amplitude of the jitter in unit intervals is given by

$$\hat{A}_j = \frac{A_j}{T_c} \tag{3-2}$$

that is where

$$1UI = T_c \tag{3-3}$$

As time jitter forms the major subject of this work, it will generally be referred to simply as jitter.

#### 3.2.2 Jitter Recurrence Equation

Referring to Figure 3.1, it can be seen that it is possible to define an expression for the variable length time interval between any two jittered pulses in terms of the period of the ideal signal and the value of the jitter at either end of the time interval in question. In particular,  $T_{\nu}(nT_c)$ , the interval between adjacent jittered pulses, can be considered the instantaneous period of the jittered signal. The instantaneous period of the jittered signal is expressible only in terms of the discrete jitter samples and is defined only at the regular instances of the corresponding ideal period  $T_c$ , that is at one or other of its endpoints, as shown in (3-4) where it has been defined at the endpoint corresponding to the jitter value  $e(nT_c)$ .

$$T_{\nu}(nT_c) = T_c + e(nT_c) - e((n-1)T_c)$$

(3-4)

#### 3.3 Time Jitter and Phase Jitter

In this section, another type of jitter called phase jitter [18] is introduced. There is a clear distinction between time jitter and phase jitter [10], [18] which is summarised here. For mathematical tractability, it may sometimes be desirable to approximate one form of jitter using the other. Under certain conditions it is possible to do this. It is important to appreciate the limitations imposed on the jitter approximation as it is used in experimental work described in Section 6.4 of Chapter 6.

Phase jitter is defined as the difference between the jittered and reference phases sampled at the regularly spaced instants of the reference clock, that is

$$p(nT_c) = \phi_{jit}(t) - \phi_{ref}(t)|_{t = nT_c}$$

(3-5)

By analogy with time jitter in Section 3.2.1, the phase jitter can be viewed as samples, taken at the instants of the reference clock, of some phase jitter function,

$p(t) = \phi_{jit}(t) - \phi_{ref}(t)$ , where  $\phi_{ref}(t)$  is the phase of an ideal reference clock signal which has perfectly regularly spaced clock pulses with period,  $T_c$

$$\phi_{ref}(t) = \frac{t}{T_c} \tag{3-6}$$

and the phase of the jittered clock signal is given by some function,  $\phi_{jit}(t)$ , such that

$$\phi_{iit}(nT_c + e(nT_c)) = n \tag{3-7}$$

As illustrated on the graph of time versus phase for reference and jittered clocks shown in Figure 3.2, both phase jitter and time jitter are defined at the regularly spaced instants of the reference clock.

Figure 3.2: Distinction between time jitter and phase jitter.

For purposes of comparing time jitter and phase jitter, it is convenient to define a quantity g(n) which is related to time jitter but is dimensionless like phase jitter. g(n) is defined as samples of the phase jitter function, p(t), at the irregularly spaced instants of the jittered clock

$$g(n) = p(t)|_{t = nT_c + e(nT_c)} = -\frac{e(nT_c)}{T_c}$$

(3-8)

As shown in (3-8), g(n) is defined to be of the opposite sign to the normalised time jitter. For example, if the jittered pulse is delayed with respect to the reference pulse and so the time jitter is positive, the phase of the jittered signal must be behind that of the reference signal and so the phase difference at that time, which is given by g(n), is negative. g(n) can be approximated by phase jitter as [10]

$$g(n) \approx \frac{p(nT_c)}{1 + p(nT_c) - p((n-1)T_c)}$$

(3-9)

(3-9) applies when the jitter is linearly varying and can be described using a first order Taylor series expansion. Furthermore, from (3-9) if the difference of adjacent samples of  $p(nT_c)$  is very small compared to unity [10] then

$$g(n) \approx p(nT_c) \tag{3-10}$$

If it is desired to approximate time jitter using phase jitter, as in (3-10), then it is shown in Appendix 3B that the restriction on the derivative of the phase jitter function is

$$\left| \frac{d}{dt} p(t) \right|_{max} \ll f_c \tag{3-11}$$

For the case of sinusoidal jitter, these conditions result in the following restriction on the jitter frequency and amplitude

$$f_j A_j \ll \frac{1}{2\pi} \tag{3-12}$$

The restriction on sinusoidal jitter frequency and amplitude is explored quantitatively in Section 6.4 of Chapter 6 where phase jitter approximation of time jitter is used in experimental work.

## 3.4 The Synchronization Process Jitter Equation for an Ideal Asynchronous Input

In its simplest and most straightforward sense, the term synchronization refers to the aligning of the timing instants of an asynchronous external signal to the timing instants of the local system clock. One result of the asynchronism is that the asynchronous input signal period is not an integer number of local clock periods. It is shown in this section that, for an ideal asynchronous input, the synchronized output signal does not have a fixed period but varies between two values. The two values are the closest integer number of local clock periods on either side of the input signal period. As a result of the varying output period, the synchronized output signal is jittered with respect to the input signal. Another important result of the asynchronism is the possibility of metastability. However, as has been considered in Chapter 2, the use of a properly designed synchronizer can make the probability of metastable failure acceptably low. Hence, the possibility of metastable failure can be ignored in the jitter analysis.

In this section a jitter equation that models the process of synchronization and which was derived for the first time by the author [60], [62] is presented. The model is applicable to two applications of practical importance examined in subsequent chapters.

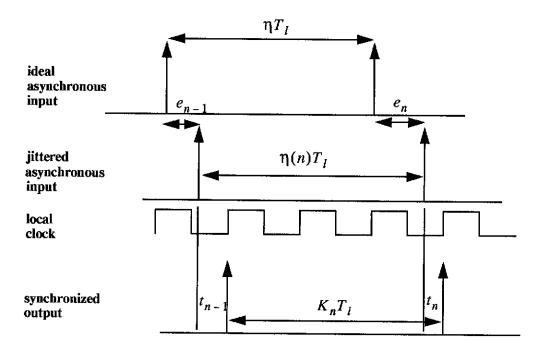

The synchronization process is modelled in terms of an asynchronous timing reference input and a local clock. The essential point is that the synchronized output is aligned with the significant edges of the local clock and is jittered with respect to the asynchronous input. A diagram which shows the relationships between the asynchronous input, the synchronized output and the jitter is in Figure 3.3.

Figure 3.3: Synchronization process jitter diagram.

An expression for the varying delay between the time of the asynchronous input and the time of the synchronized output is obtainable directly from Figure 3.3 and is given in (3-13)

$$t_n = t_{n-1} + K_n T_l - \eta T_l \tag{3-13}$$

where T is the period of the asynchronous input,  $T_l$  is the local clock period,  $\eta = T/T_l \in \Re$ ,  $K_n$  is an integer number of periods of  $T_l$ , and  $t_n$  is the jitter on the synchronized output. The model allows for the fact that practical synchronizers have a positive delay.

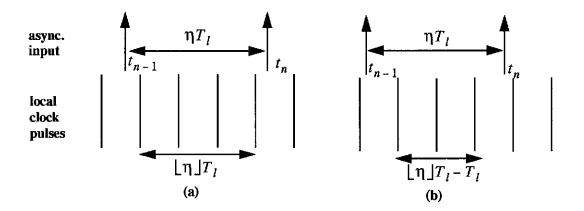

Mapping the local clock period onto T in the synchronization process results in two possible patterns as illustrated in Figure 3.4.

Figure 3.4: Mapping local clock onto period of asynchronous input.

Part (a) of Figure 3.4 shows the first case where the integer part of  $\eta$  is provided by a corresponding integer number of full periods of  $T_l$  giving (3-14).

$$\eta T_{I} = \lfloor \eta \rfloor T_{I} + t_{n-1} + (T_{I} - t_{n})$$

(3-14)

Part (b) of Figure 3.4 illustrates the second case where the integer number of full periods of  $T_l$  is one period less than the integer part of  $\eta$  giving (3-15).

$$\eta T_I = \lfloor \eta \rfloor T_I + t_{n-1} - t_n \tag{3-15}$$

where  $\lfloor a \rfloor = \text{greatest integer } \leq a$ .

It is shown in Appendix 3C that these are the only two possible patterns and the derivation for the combined form in (3-16) is given, where use is made of the new variable  $x_n = t_n/T_l$ .

$$\eta = \lfloor \eta \rfloor + x_{n-1} - x_n + 1 - u(x_{n-1} + \lfloor \eta \rfloor - \eta)$$

(3-16)

The closed form of (3-16) is also derived in Appendix 3C and is

$$x_n = x_0 - n\eta - \lfloor x_0 - n\eta \rfloor \tag{3-17}$$

which can be written in terms of absolute time, that is with  $t_n = x_n T_l$

$$t_n = t_0 - n\eta T_l - \left\lfloor \frac{t_0}{T_l} - n\eta \right\rfloor T_l \tag{3-18}$$

Finally, it is shown in Appendix 3D that the jitter equation for the synchronizer is stable. Stability means that the long term average period of the output signal is equal to the period of the input signal, although individual periods of the output signal may equal either  $\lfloor \eta \rfloor$  or  $\lfloor \eta \rfloor + 1$  local clock periods. Because of the varying period of the output signal, the significant instants of the output signal are jittered with respect to the significant instants of the input signal. The resulting jitter on the output signal is expressed by (3-18).

#### 3.5 Fourier Transforms of Jitter

The spectrum of the jitter provides an alternate and, in some applications, more useful characterization of the jitter. For example, it is useful in characterizing the effect of filtering by a phase-locked loop. The spectrum of the synchronization process jitter is used in Chapter 4 and Chapter 5 to investigate the performance of two different practical applications of the synchronization process.

As discussed in Section 3.2, jitter is defined as a series of discrete time samples taken at the regular instants of the reference clock. When the samples are the samples of some continuous time function, there is a straightforward technique for finding the spectrum of the jitter using the Fourier Transform of the continuous time function.

Consider time jitter,  $e(nT_c)$ , which can be considered as samples of some jitter function e(t) taken at  $t = nT_c$ . If the continuous time jitter function has some Fourier Transform E(f), then

$$\mathcal{F}\{e(nT_c)\} = f_c \mathcal{F}\left\{e(t) \sum_{n=-\infty}^{\infty} \delta(t - nT_c)\right\}$$

$$= f_c E(f) \otimes \sum_{n=-\infty}^{\infty} \delta(f - nf_c)$$

$$= f_c \sum_{n=-\infty}^{\infty} E(f - nf_c)$$

(3-19)

where  $\otimes$  represents the convolution operator.

Applying this approach to the synchronizer jitter equation, the function z(t) when sampled at t = nT yields (3-18).

$$z(t) = t_0 - \frac{\eta t T_l}{T} - \left| \frac{t_0}{T_l} - \frac{\eta t}{T} \right| T_l$$

(3-20)

As z(t) is periodic with period  $\frac{T}{\eta}$  secs, it can also be written as a Fourier Series

$$z(t) = \sum_{k=-\infty}^{\infty} d_k e^{\frac{j2\pi k \eta t}{T}}$$

(3-21)

where

$$d_{k} = \begin{cases} \frac{T_{l}}{2}, & k = 0\\ \frac{e^{-j2\pi kx_{0}}T_{l}}{j2\pi k}, & k \neq 0 \end{cases}$$

(3-22)

The Fourier Transform of (3-21) is

$J(f) = \mathcal{F}\{t_n\}$

$$Z(f) = \sum_{k=-\infty}^{\infty} d_k \delta(f - k\eta F)$$

(3-23)

where the coefficients  $d_k$  are as defined in (3-22), F=1/T, and use is made of the property that

$$\sum_{k=-\infty}^{\infty} e^{\frac{-j2\pi kt}{T}} \leftrightarrow \sum_{k=-\infty}^{\infty} \delta(f - kF)$$

(3-24)

Applying (3-19)

$$= F \sum_{k=-\infty}^{\infty} d_k \sum_{n=-\infty}^{\infty} \delta(f - k\eta F - nF)$$

(3-25)

It is shown in Appendix 3E that the RMS jitter power is

$$P = F^2 \left( \frac{T_I^2}{4} + \frac{T_I^2}{12} \right) \tag{3-26}$$

The first term on the right is the DC power.

## 3.6 The Synchronization Process Jitter Equation for a Jittered Asynchronous Input

In this section, the synchronizer jitter equation will be extended by deriving the expressions which apply when the asynchronous input signal is jittered with respect to the ideal asynchronous input considered in Section 3.4. In the practical applications presented in Chapter 4 and Chapter 5, it is not likely that an ideal, perfectly regular asynchronous input is obtainable, so it is useful to derive the jitter equation and spectrum under these conditions.

Figure 3.5: Timing diagram for a jittered asynchronous input.

When the asynchronous input is jittered, the period of the asynchronous input signal is varying and the ratio of its period to the local clock period is not given by some

constant, but is also varying. As shown in Figure 3.5, the relationship between the ideal asynchronous input and the jittered asynchronous input is given by

$$\eta T_l + e_n - e_{n-1} = \eta(n) T_l \tag{3-27}$$

where  $e_n$  is the nth sample of the jitter on the asynchronous input. The varying period of the jittered asynchronous input is expressed by  $\eta(n)T_l$ . Neither  $\eta$  nor  $\eta(n)$  is necessarily an integer. Also from Figure 3.5, it can be seen that (3-13) still applies to the relationship between the input and the output of the synchronizer. Hence, combining the two equations it is possible to write

$$\eta T_l + e_n - e_{n-1} = t_{n-1} + K_n T_l - t_n \tag{3-28}$$

where  $K_n$  is an integer number of local clock periods but is not a constant.

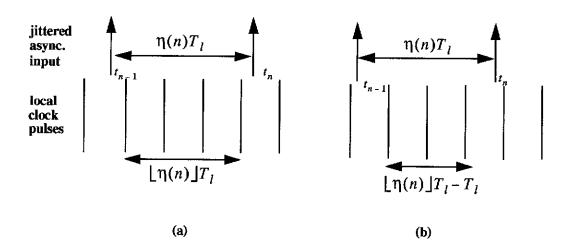

Figure 3.6: Mapping local clock onto jittered asynchronous input period.

Using the same approach as in Section 3.4, Figure 3.6 shows that the local clock period may be mapped onto the varying period,  $\eta(n)T_l$ , of the jittered asynchronous input resulting in two possible patterns. The proof given in Appendix 3C which shows that these are the only two possibilities for a constant period applies equally to the case of a varying period.

Part (a) of Figure 3.6 shows the first case where the integer part of  $\eta(n)$  is provided by a corresponding integer number of full periods of  $T_l$  giving (3-29).

$$\eta(n)T_{l} = \lfloor \eta(n) \rfloor T_{l} + t_{n-1} + (T_{l} - t_{n})$$

(3-29)

Part (b) of Figure 3.6 illustrates the second case where the integer number of full periods of  $T_l$  is one period less than the integer part of  $\eta(n)$  giving (3-30).

$$\eta(n)T_1 = \lfloor \eta(n) \rfloor T_1 + t_{n-1} - t_n \tag{3-30}$$