School of Electrical and Computer Engineering

Signal Compression for Digital Television

by

Mr. Huy So Truong

This thesis is presented as part of the requirements for the award of the Degree of Master of Engineering

of

Curtin University of Technology

## PROJECT DOCUMENTATION SHEET TITLE Signal Compression for **Digital Television AUTHOR** Huy So Truong DATE SUPERVISOR April 18, 1999 Dr. Stephen C. Y. Ho OPTION **DEGREE** Electrical Master of Engineering ABSTRACT Still image and image sequence compression plays an important role in digital television. For still image compression, Block Adaptive Classified Vector Quantisation (BACVQ) algorithm has been developed which combines variable block size coding and CVQ. Segmentation and classification decisions are made based on spatial and temporal domain criteria. For image sequence compression, an adaptive coding technique has been developed which divides an image sequence into groups of pictures using adaptive scene segmentation before BACVQ and variable block size motion compensated predictive coding techniques are applied. Both compression techniques have demonstrated good performance with high compression gain and reconstruction quality. A small scale parallel DSP system has been constructed with a 486DX33 IBM/PC serving as a master processor and two DSP (PC-32) cards as parallel processors. Dualport memory has been used to provide high speed interconnection and its access is arbitrated by hardware semaphore and mailbox messaging. The host PC shall dynamically distribute processing tasks to idle PC-32 cards for parallel processing. Optimal parallel operation has been achieved during 4x4 CVQ processing, variable block size motion compensation and residual frame processing.

#### INDEXING TERMS

Block Adaptive Classified VQ, intraframe coding, interframe coding, motion compensated predictive coding, variable block size motion estimation, progressive motion estimation, adaptive scene segmentation, quadtree segmentation, parallel still image compression, parallel image sequence compression, statistical redundancy, spatial and temporal redundancy.

|                     | GOOD        | AVERAGE | POOR |

|---------------------|-------------|---------|------|

| TECHNICAL WORK      |             |         |      |

| REPORT PRESENTATION |             |         |      |

| EXAMINER            | CO-EXAMINER |         |      |

|                     |             |         |      |

|                     |             |         |      |

Mr. Huy So Truong

18 April, 1999

Prof. T. Smith

Dean of Engineering

Curtin University of Technology

Kent Street,

Bentley, W.A. 6120

Dear Sir,

Please accept this thesis, entitled "Signal Compression for Digital Television", as part of the requirements for the Degree of Master of Engineering (Electrical Engineering).

Yours faithfully,

Mr. Huy So Truong

## **Synopsis**

Still image and image sequence compression plays an important role in the development of digital television. Although various still image and image sequence compression algorithms have already been developed, it is very difficult for them to achieve both compression performance and coding efficiency simultaneously due to the complexity of the compression process itself. As a results, improvements in the forms of hybrid coding, coding procedure refinement, new algorithms and even new coding concepts have been constantly tried, some offering very encouraging results.

In this thesis, Block Adaptive Classified Vector Quantisation (BACVQ) has been developed as an alternative algorithm for still image compression. It is found that BACVQ achieves good compression performance and coding efficiency by combining variable block-size coding and classified VQ. Its performance is further enhanced by adopting both spatial and transform domain criteria for the image block segmentation and classification process. Alternative algorithms have also been developed to accelerate normal codebook searching operation and to determine the optimal sizes of classified VQ sub-codebooks.

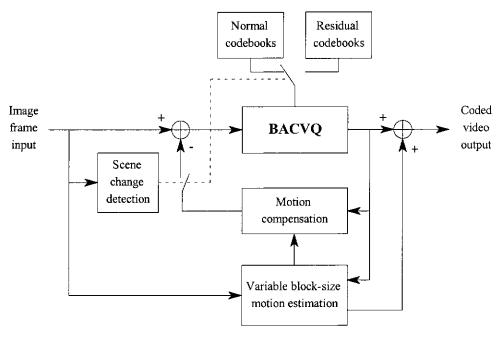

For image sequence compression, an adaptive spatial/temporal compression algorithm has been developed which divides an image sequence into smaller groups of pictures (GOP) using adaptive scene segmentation before BACVQ and variable block-size motion compensated predictive coding are applied to the intraframe and interframe coding processes. It is found the application of the proposed adaptive scene segmentation algorithm, an alternative motion estimation strategy and a new progressive motion estimation algorithm enables the performance and efficiency of the compression process to be improved even further.

Apart from improving still image and image sequence compression algorithms, the application of parallel processing to image sequence compression is also investigated. Parallel image compression offers a more effective approach than the sequential counterparts to accelerate the compression process and bring it closer to

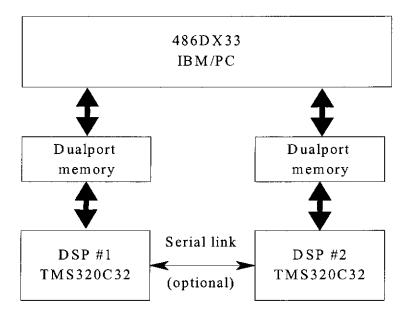

real-time operation. In this study, a small scale parallel digital signal processing platform has been constructed for supporting parallel image sequence compression operation. It consists of a 486DX33 IBM/PC serving as a master processor and two DSP (PC-32) cards as parallel processors. Because of the independent processing and spatial arrangement natures of most image processing operations, an effective parallel image sequence compression algorithm has been developed on the proposed parallel processing platform to significantly reduce the processing time of the proposed parallel image compression algorithms.

## Acknowledgments

I would like to acknowledge the support and encouragement of my supervisor, Dr. Stephen C. Y. Ho. His expertise in the area of digital signal processing and image processing has provided me a significant insight into many issues encountered throughout the course of my study. I am also grateful for his endorsement and arrangement for me to obtain financial assistance from Australian Postgraduate Award scholarship and funding for acquiring parallel DSP hardware from Curtin University; without which my Master study would not be possible.

I would like to acknowledge financial supports from my School for me to attend several International Conferences. Staff members at my School have also offered valuable assistance throughout the course of my study. In particular, I would like to thank Mrs Ingrid Hastie and Mrs. Susan Summers for their administrative work.

Special thanks to Dr. Kheong Chee with whom I have had so many exiting and enjoyable discussions on various topics of image compression due to his enthusiasm and expertise in the field. I am also grateful for his valuable advice on how to organising research materials and his assistance in utilising HP workstations in the Image Technology lab for conducting my research activities.

Finally, I would like to thank Mr. Sarfraz Khokhar and Mr Yukihiro Nakazato for their friendship and interest in my work. I would also like to thank all of my family members. Without their continuing supports and encouragement, my Master study would have been very difficult.

## Table of Contents

| Synopsis                                            | 1    |

|-----------------------------------------------------|------|

| Acknowledgments                                     | iii  |

| Table of Contents                                   | iv   |

| List of Figures                                     | viii |

| List of Tables                                      | X    |

| List of Abbreviations                               | xi   |

| Chapter 1: Introduction                             | 1    |

| 1.1 Introduction                                    | 1    |

| 1.2 The growing importance of digital technology    | 2    |

| 1.3 The importance of digital image compression     | 4    |

| 1.4 Thesis contributions                            |      |

| 1.5 Thesis organisation                             | 6    |

| Chapter 2: Still Image Compression                  | 9    |

| 2.1 Introduction                                    | 9    |

| 2.2 Transform coding                                | 12   |

| 2.2.1 Discrete Fourier transform (DFT):             |      |

| 2.2.2 Discrete Hartley transform (DHT):             |      |

| 2.2.3 Karhunen-Loeve transform (KLT):               | 17   |

| 2.2.4 Discrete Cosine transform (DCT):              |      |

| 2.3 Subband and wavelet coding                      | 19   |

| 2.4 Vector quantisation                             | 24   |

| 2.4.1 Overview                                      | 24   |

| 2.4.2 Vector quantisation                           | 27   |

| 2.4.3 Shannon's rate-distortion theorem             |      |

| 2.4.4 Optimality conditions for vector quantisation | 31   |

| 2.4.5 Nearest Neighbour Quantisation                |      |

| 2.4.6 Structurally constrained vector quantisers    |      |

| 2.4.7 Fast nearest neighbour encoding techniques    |      |

| 2.4.8 Vector quantisation codebook generation       | 46   |

| 2 4 9 Generalised Llovd algorithm                   | 49   |

| 2.5 Proposed block adaptive classified vector quantisation        | 52  |

|-------------------------------------------------------------------|-----|

| 2.5.1 Variable block-size coding with adaptive block segmentation | 52  |

| 2.5.2 Classified VQ                                               | 55  |

| 2.5.3 Image sub-block classification                              | 56  |

| 2.5.4 BACVQ Codebook design                                       | 60  |

| 2.5.5 Bit allocation                                              | 64  |

| 2.5.6 Simulation results                                          | 65  |

| 2.6 Huffman coding and arithmetic coding                          | 71  |

| 2.7 Summary                                                       | 72  |

| Chapter 3: Image Sequence Compression                             | 76  |

| 3.1 Introduction                                                  | 76  |

| 3.2 Human Visual System                                           | 82  |

| 3.3 Scene Segmentation                                            | 84  |

| 3.4 Motion compensated coding                                     | 87  |

| 3.4.1 Motion compensated predictive coding                        |     |

| 3.4.2 Motion compensated interpolative coding                     | 92  |

| 3.4.3 Motion estimation strategy                                  | 94  |

| 3.5 Adaptive coding techniques                                    | 100 |

| 3.6 Basic coding structures of MPEG                               | 103 |

| 3.7 Proposed adaptive image sequence compression algorithm        |     |

| 3.7.1 Adaptive scene segmentation                                 | 104 |

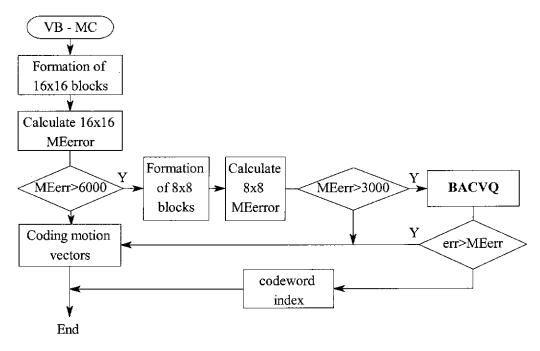

| 3.7.2 Variable block-size motion compensation                     | 108 |

| 3.7.3 Progressive motion vector estimation                        | 110 |

| 3.7.4 Block adaptive classified vector quantisation (BACVQ)       | 113 |

| 3.7.5 Simulation results                                          | 116 |

| 3.8 Summary                                                       | 120 |

| Chapter 4: Parallel Processing                                    | 132 |

| 4.1 Introduction                                                  | 132 |

| 4.2 Parallel processing architectures                             | 136 |

| 4.2.1 Single instruction stream-single data stream (SISD)         | 136 |

| 4.2.2 Single instruction stream-multiple data stream (SIMD)       | 137 |

| 4.2.3 Multiple-instruction stream-Single data stream (MISD)       | 138 |

| 4.2.4 Multiple-instruction stream-Multiple data stream (MIMD)     | 139 |

| 4.3 Connectivity in parallel processing systems                   | 141 |

|-------------------------------------------------------------------|-----|

| 4.4 Processing synchronisation                                    | 142 |

| 4.4.1 Synchronisation in shared-memory processing                 |     |

| 4.4.2 Synchronisation in message passing computation              | 145 |

| 4.5 Partitioning and scheduling                                   | 146 |

| 4.6 Processing performance                                        |     |

| 4.7 Parallel processing system design issues                      | 150 |

| 4.7.1 Message-passing MIMD                                        |     |

| 4.7.2 Shared-memory MIMD                                          |     |

| 4.8 Summary                                                       |     |

| Chapter 5: Parallel Image Sequence Compression                    | 156 |

| 5.1 Introduction                                                  | 156 |

| 5.2 Parallel digital signal processing platforms                  |     |

| 5.2.1 Overview                                                    |     |

| 5.2.2 Texas Instruments TMS320C80 MVP DSP system                  | 161 |

| 5.2.3 Sonitech SPIRIT-40 system                                   |     |

| 5.2.4 Atlanta Signal Processors ELP DSP platform                  | 163 |

| 5.2.5 Innovative Integration PC32 DSP system                      | 164 |

| 5.2.6 Other parallel DSP systems                                  | 165 |

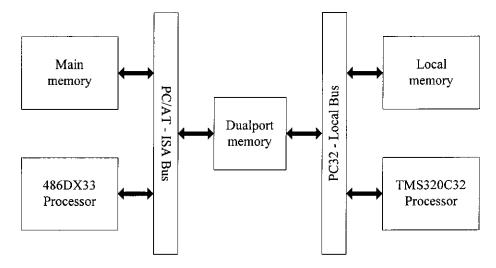

| 5.3 Hardware configuration of the prototype parallel DSP platform | 165 |

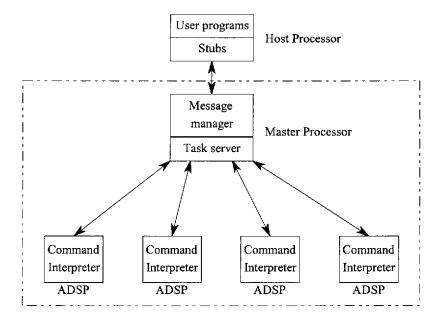

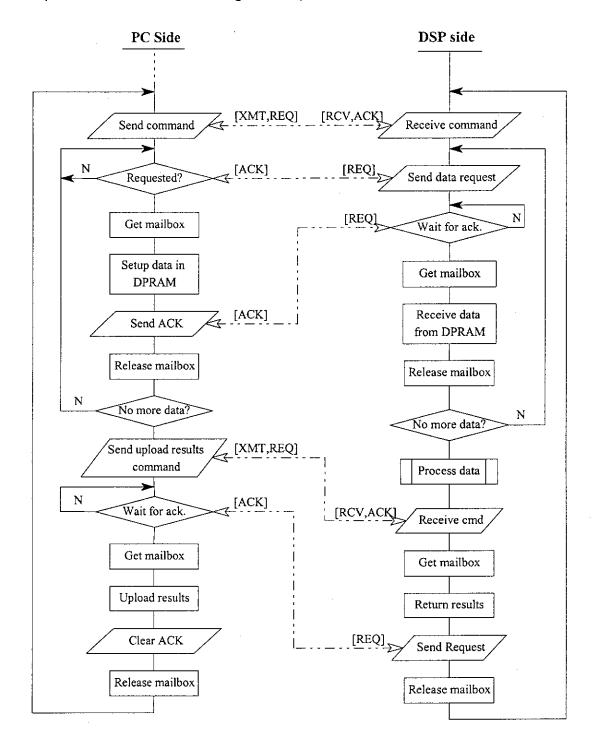

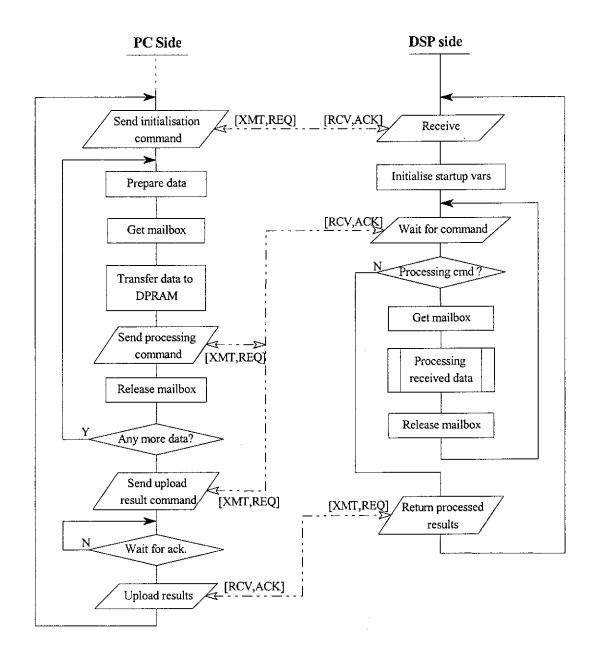

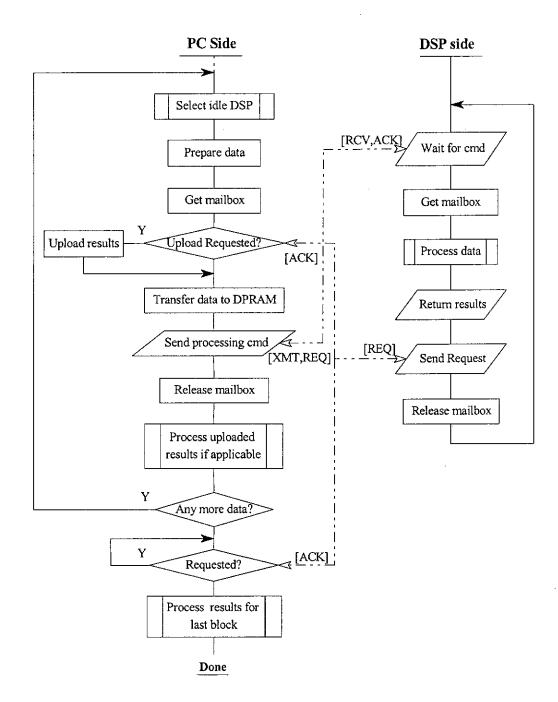

| 5.4 Basic operations of the prototype parallel DSP platform       | 169 |

| 5.5 Dualport memory operation                                     | 171 |

| 5.6 Semaphore operation                                           | 175 |

| 5.7 Parallel processing algorithm and experimental results        |     |

| 5.7.1 Parallel HOD computation                                    |     |

| 5.7.2 Parallel still image compression                            |     |

| 5.7.3 Parallel image sequence compression                         |     |

| 5.8 Summary                                                       |     |

| Chapter 6: Conclusions and Recommendations                        | 206 |

| 6.1 BACVQ algorithm                                               | 206 |

| 6.1.1 Algorithm overview                                          |     |

| 6.1.2 Coder Evaluation                                            |     |

| 6.1.3 Recommendations                                             | 208 |

| 6.2 Adaptive spatial/temporal image sequence compression    | 209      |

|-------------------------------------------------------------|----------|

| 6.2.1 Algorithm overview                                    | 209      |

| 6.2.2 Coder Evaluation                                      | 211      |

| 6.2.3 Recommendations                                       | 212      |

| 6.3 Parallel image sequence compression                     | 213      |

| 6.3.1 Algorithm overview                                    | 213      |

| 6.3.2 Coder evaluation                                      | 216      |

| 6.3.3 Recommendations                                       | 218      |

| References                                                  | 220      |

| Appendix A: Conference Paper #1                             | 226      |

| Appendix B: Conference Paper #2                             | 238      |

| Appendix C: Conference Paper #3                             | 244      |

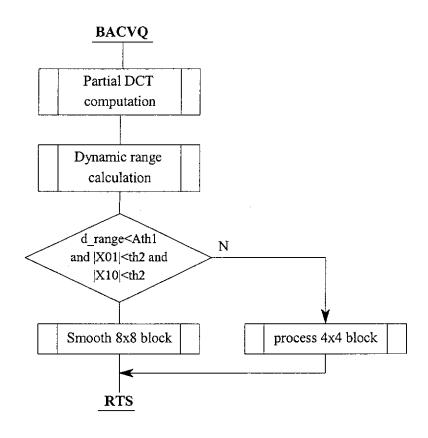

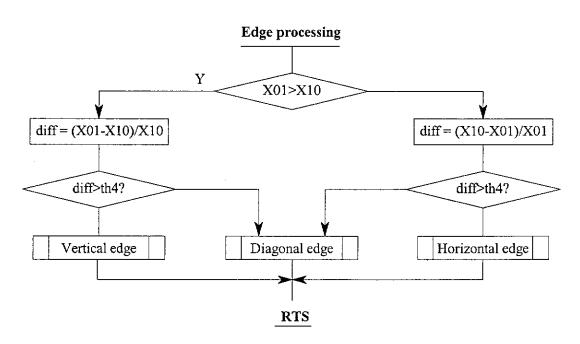

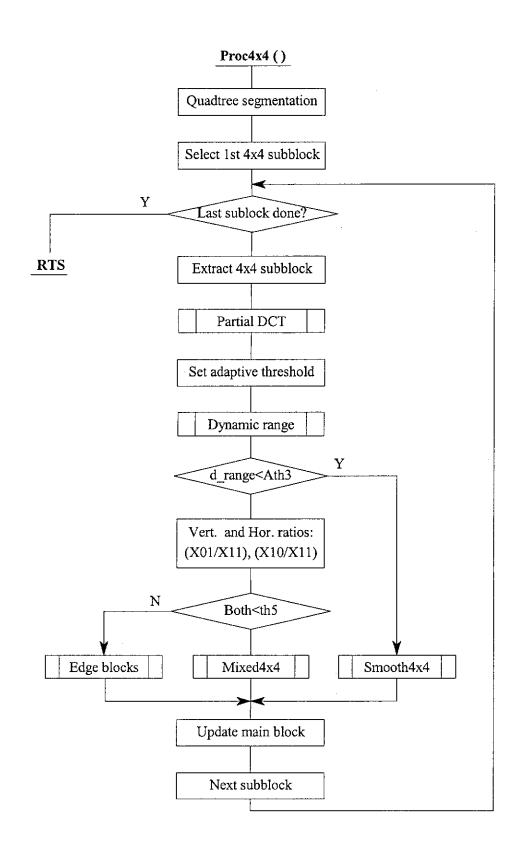

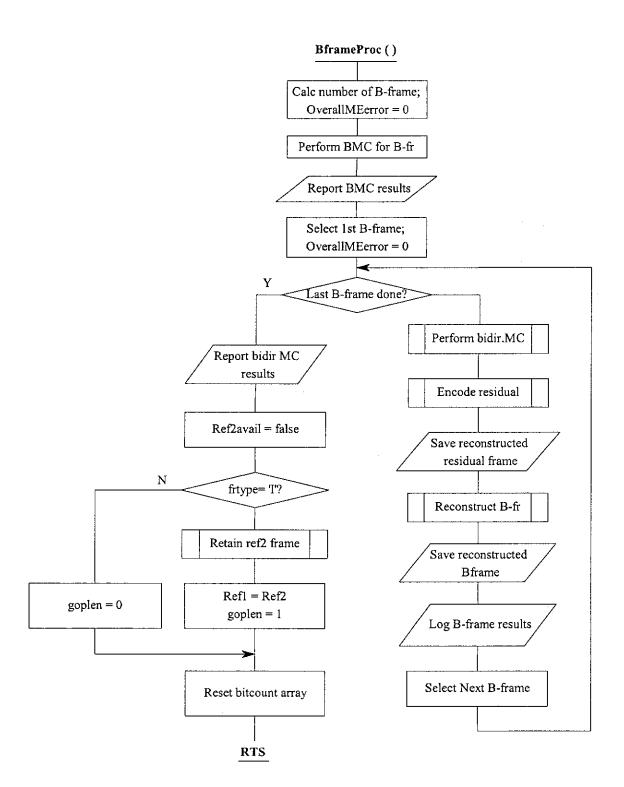

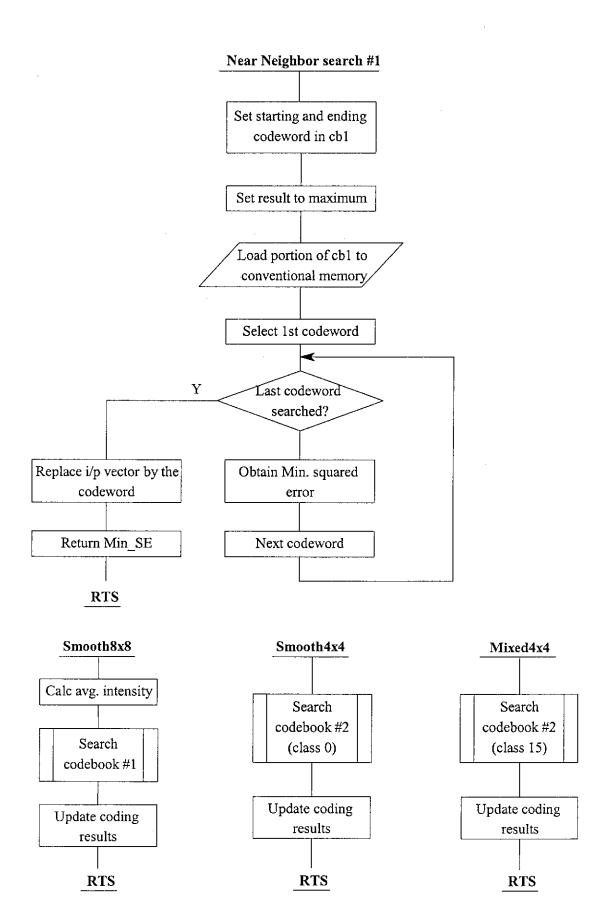

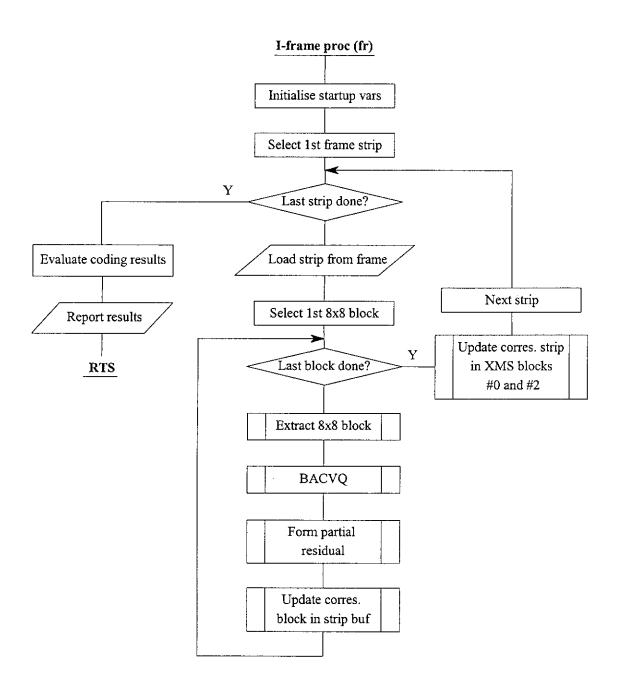

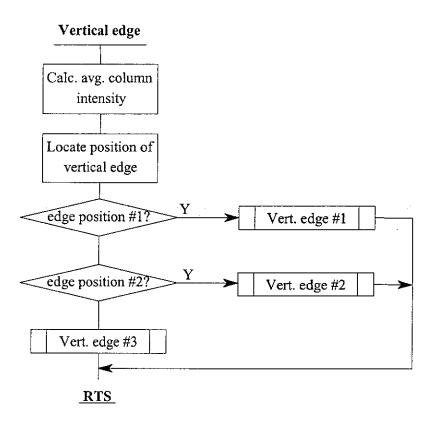

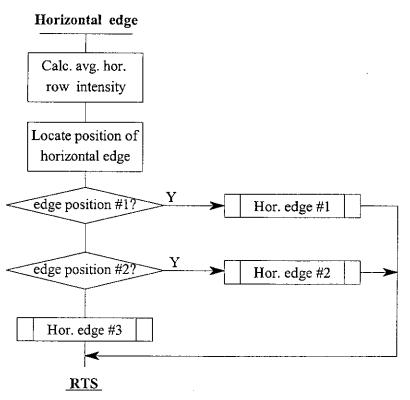

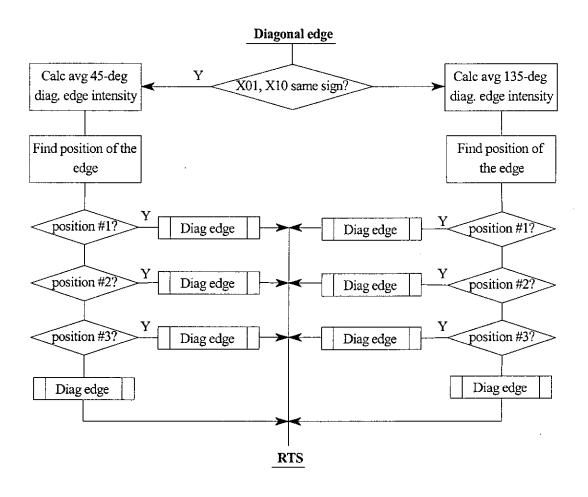

| Appendix D: Still Image Compression Flowchart               | 250      |

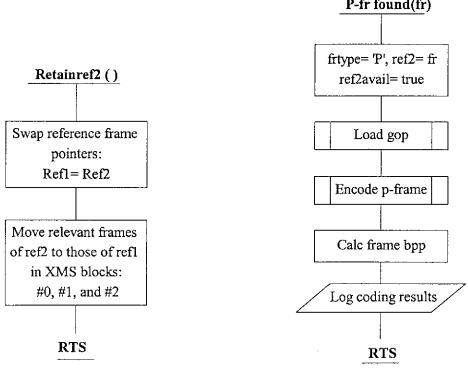

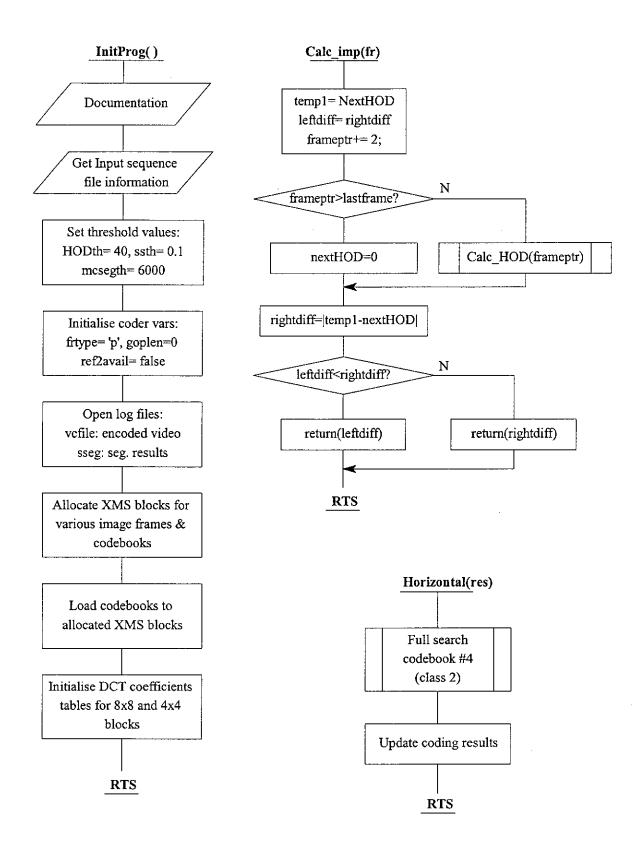

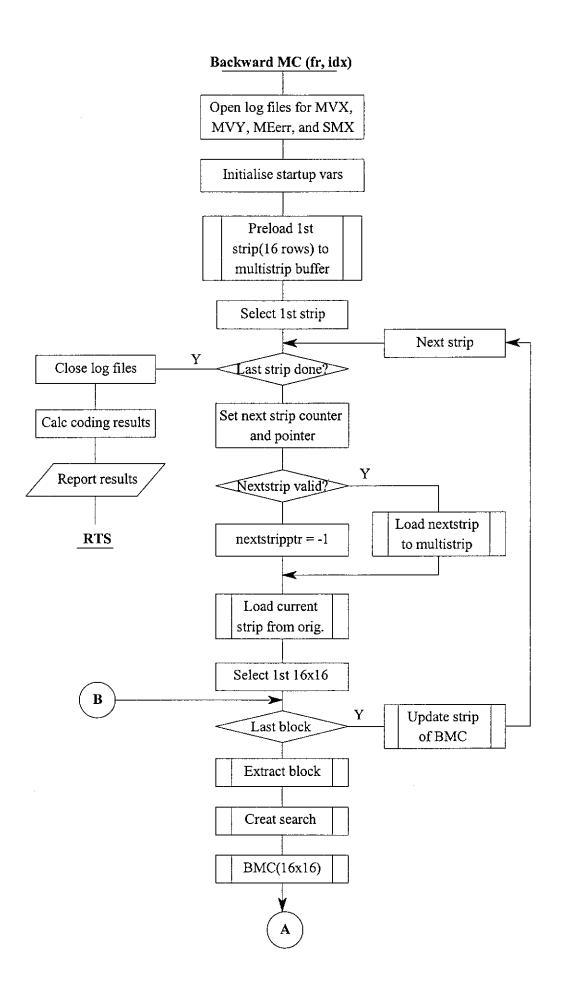

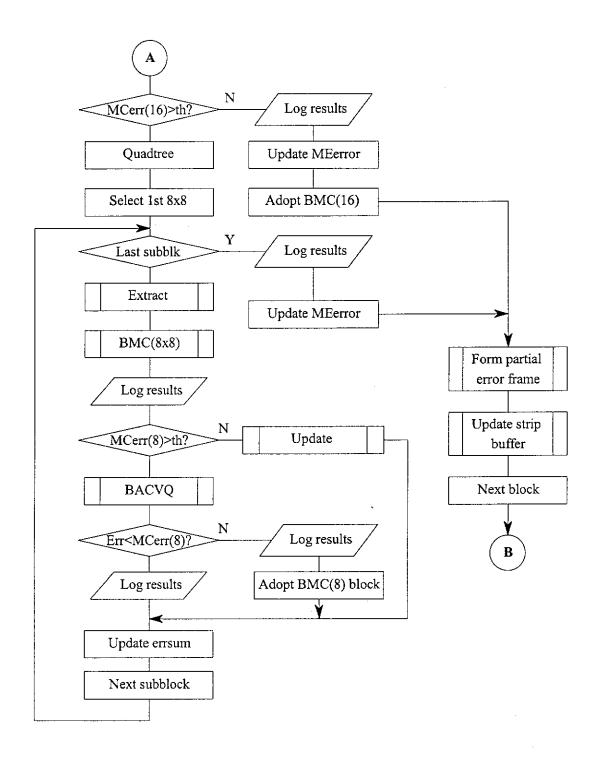

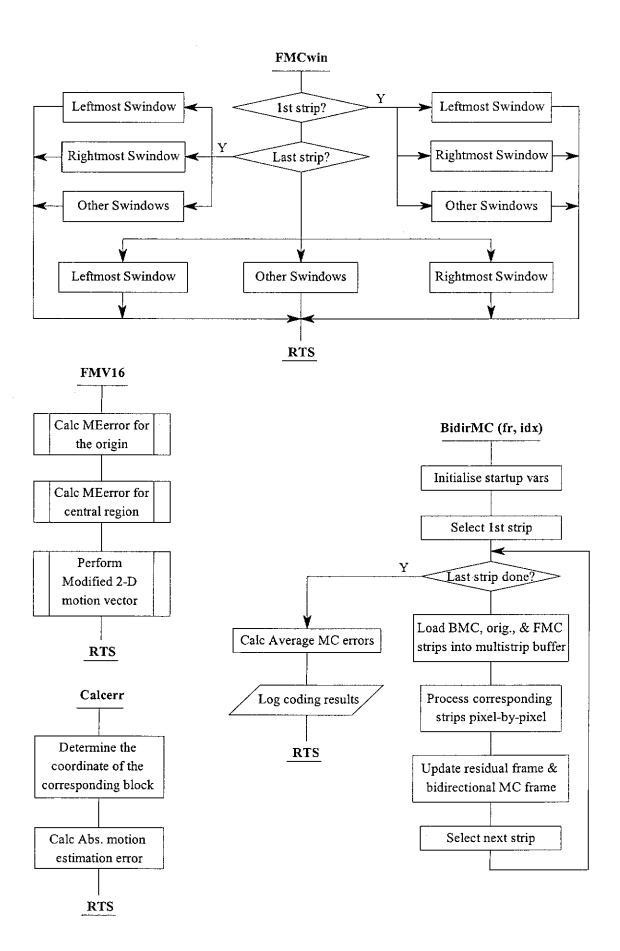

| Appendix E: Image Sequence Compression Flowchart            | 267      |

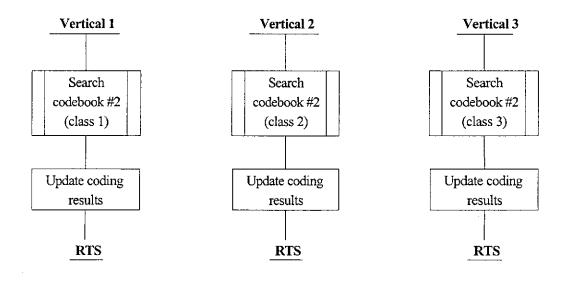

| Appendix F: Parallel Processing Arrangements                | 272      |

| Appendix G: Boot loading operations                         | 275      |

| Appendix H: Influence of high level languages on processing | speed277 |

| Appendix I: Samples of Parallel Processing Results          | 279      |

# List of Figures

| Figure 2.1: Block diagram of transform coding                                            | 14 |

|------------------------------------------------------------------------------------------|----|

| Figure 2:2: A typical zigzag scanning pattern for transformed coefficients quantisation  | 15 |

| Figure 2.3: A typical subband decomposition of still images.                             | 20 |

| Figure 2.4: Block diagram of a subband coding system                                     |    |

| Figure 2.5: Block diagram of vector quantisation coding systems                          | 25 |

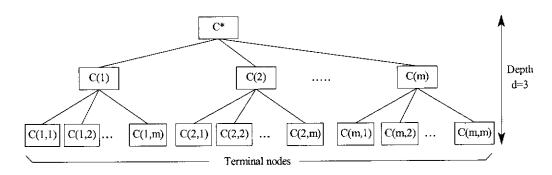

| Figure 2.6: Typical codebook structure of TSVQs                                          | 34 |

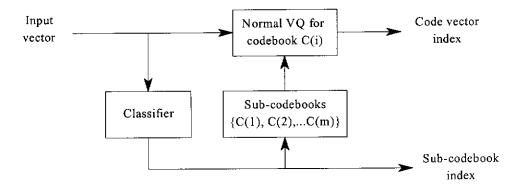

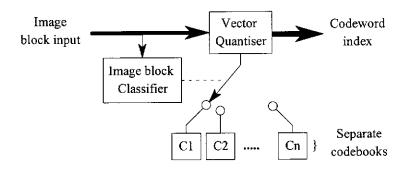

| Figure 2.7: Block diagram of classified VQ                                               | 36 |

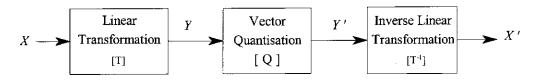

| Figure 2.8: Block diagram of transform VQ                                                | 38 |

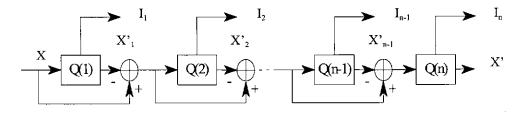

| Figure 2.9: Block diagram of multi-stage VQ                                              | 39 |

| Figure 2.10: Triangle inequality codebook search method                                  | 45 |

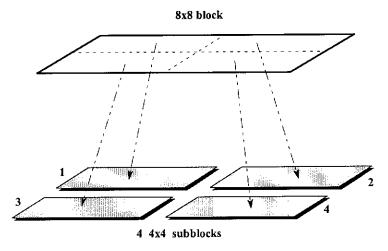

| Figure 2.11: Adaptive block segmentation structure                                       |    |

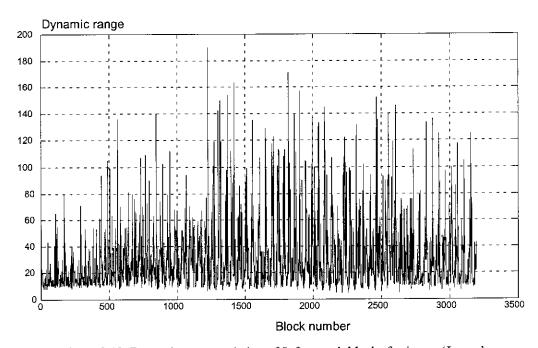

| Figure 2.12: Dynamic range variation of 8x8 smooth blocks for image 'Lenna'              |    |

| Figure 2.13: Illustration diagram of BACVQ                                               | 54 |

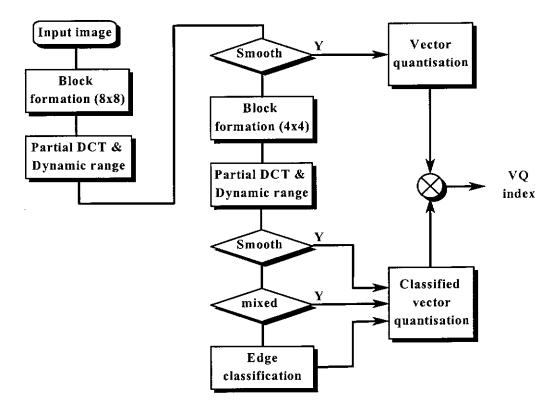

| Figure 2.14: Classified VQ operation                                                     | 56 |

| Figure 2.15: An original and transformed high texture block                              | 58 |

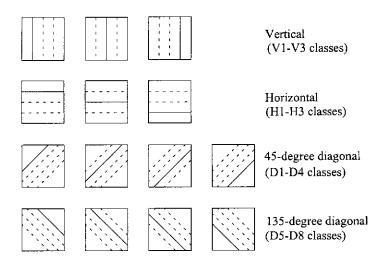

| Figure 2.16: Various classes for blocks containing edges                                 | 58 |

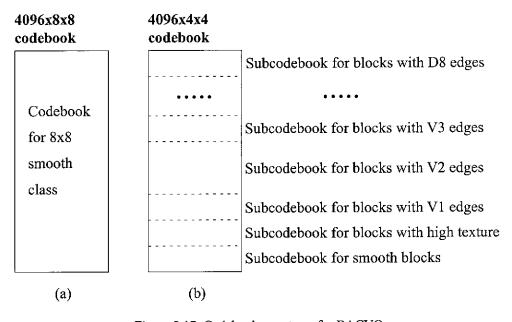

| Figure 2.17: Codebook structures for BACVQ                                               |    |

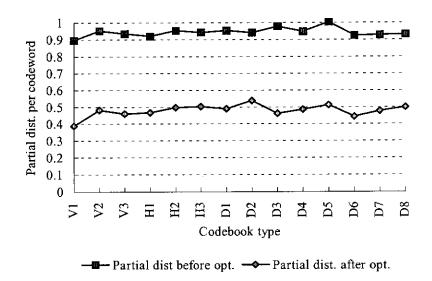

| Figure 2.18: Partial distortion among various edge-like codebooks                        | 61 |

| Figure 2.19: Partial codebook search range                                               | 64 |

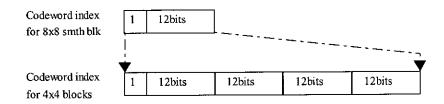

| Figure 2.20: Bit allocation for BACVQ code words                                         | 65 |

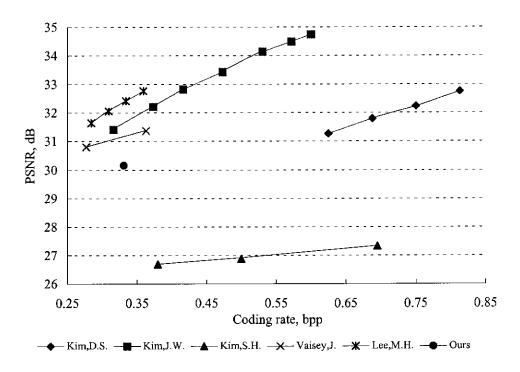

| Figure 2.21: Various coding results for 'Lenna' image                                    | 68 |

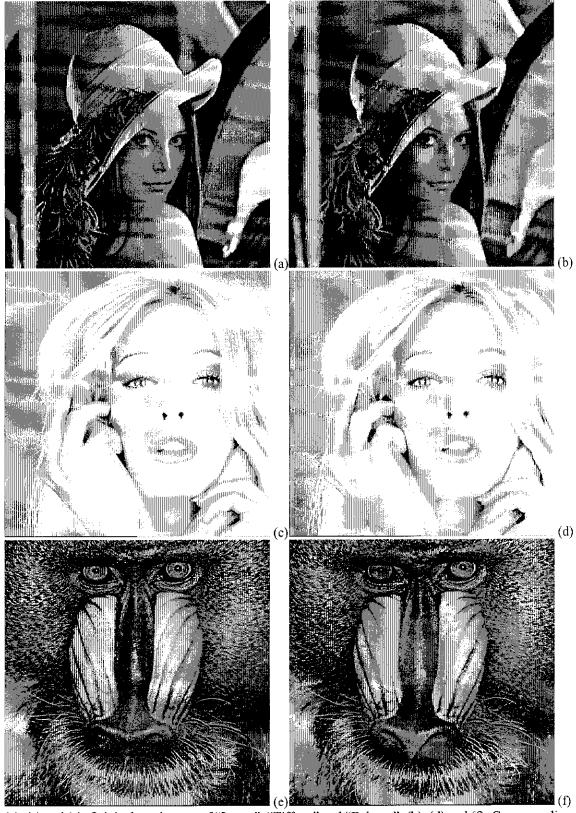

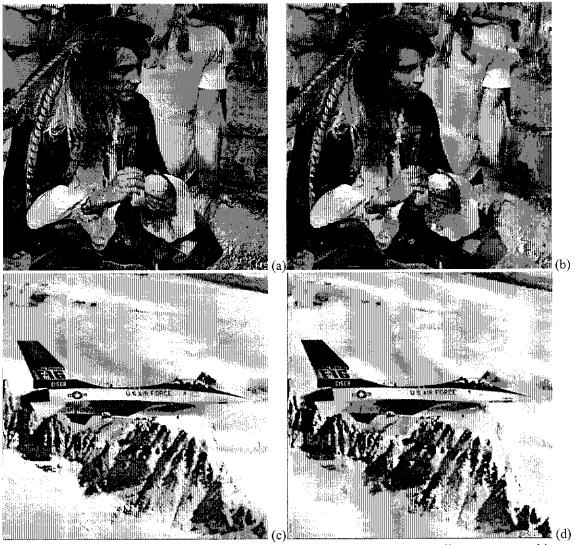

| Figure 2.22: Sample results of BACVQ coding process (set #1)                             | 70 |

| Figure 2.23: Sample results of BACVQ coding process (set #2)                             | 71 |

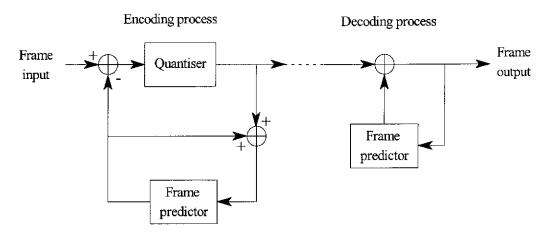

| Figure 3.1: Typical temporal DPCM coding                                                 | 79 |

| Figure 3.2: General coding structure of a motion compensated DPCM coder                  |    |

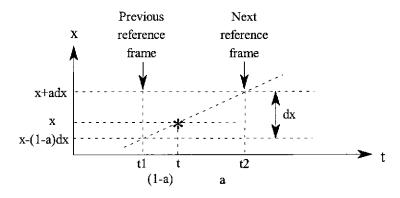

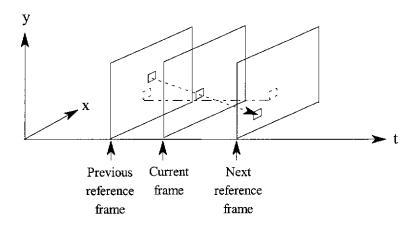

| Figure 3.3: Operation principle of temporal interpolation                                |    |

| Figure 3.4: Predicting missing image samples using bidirectional temporal interpolation. |    |

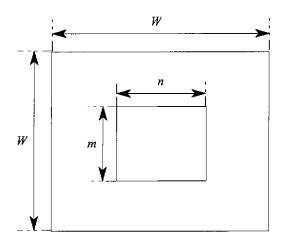

| Figure 3.5: Window search range for motion estimation                                    |    |

| Figure 3.6: Example of 2D logarithmic search strategy                                    |    |

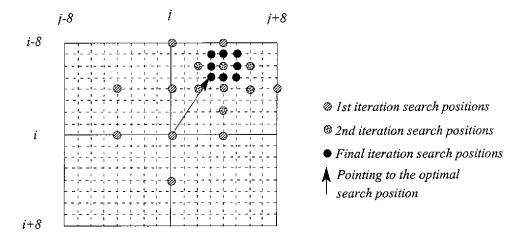

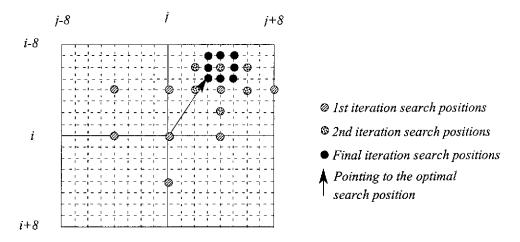

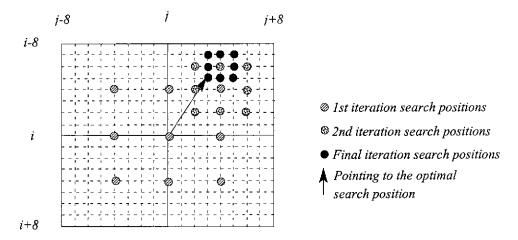

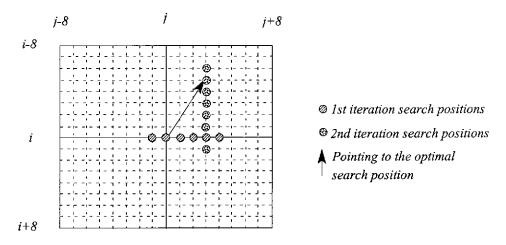

| Figure 3.7: Example of modified 2D search strategy                                       |    |

| Figure 3.8: Example of 3-step search strategy                                            |    |

| Figure 3.9: Example of modified one-at-a-time search strategy                            |    |

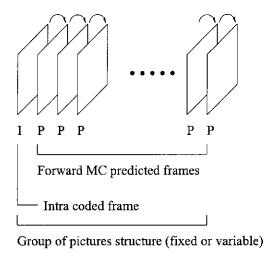

| Figure 3.10: Basic GOP frame structure for MPEG coding without B-frame inclusion    | 103 |

|-------------------------------------------------------------------------------------|-----|

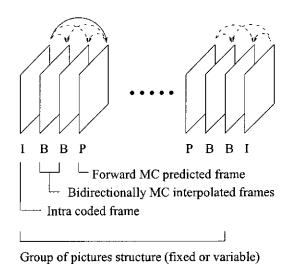

| Figure 3.11: Basic GOP frame structure for MPEG coding with B-frame inclusion       | 104 |

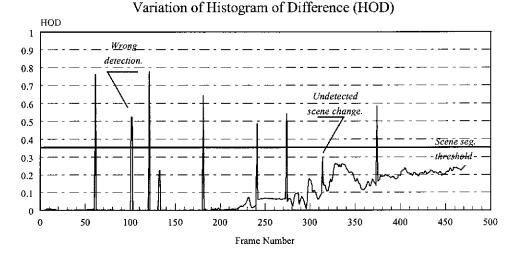

| Figure 3.12: Histogram of difference for the test sequence                          | 105 |

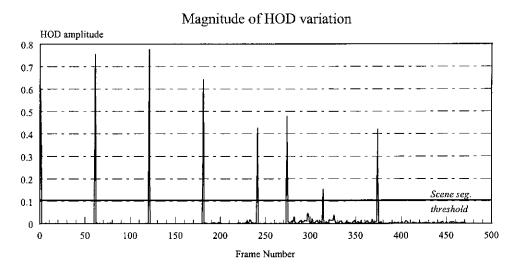

| Figure 3.13: Magnitude of HOD variation of the test sequence                        | 106 |

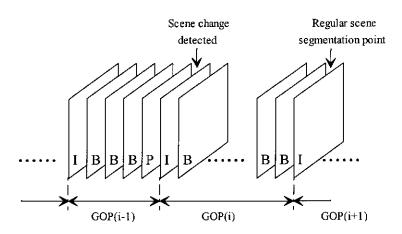

| Figure 3.14: Dynamic GOP structure                                                  | 107 |

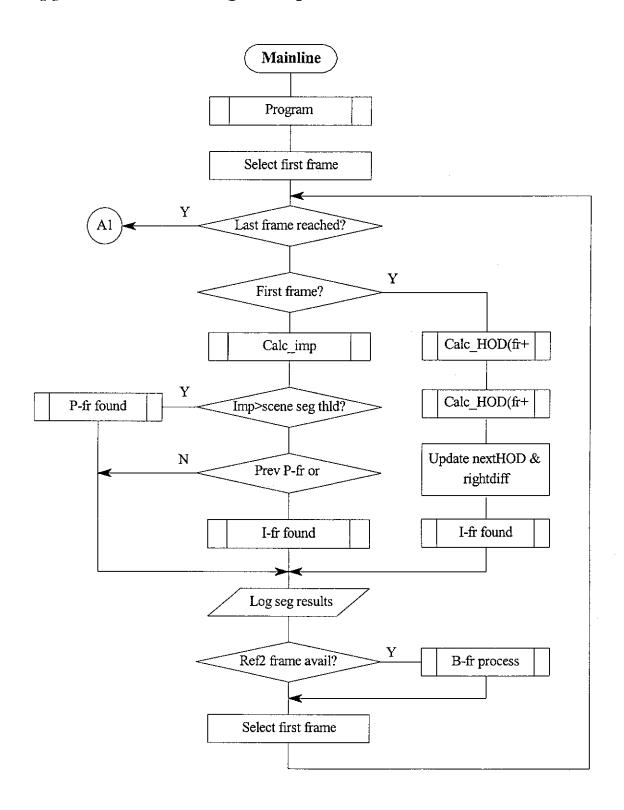

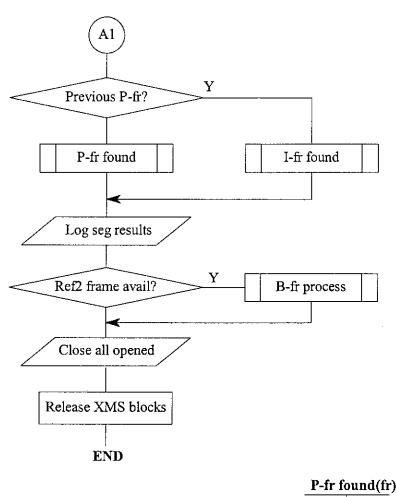

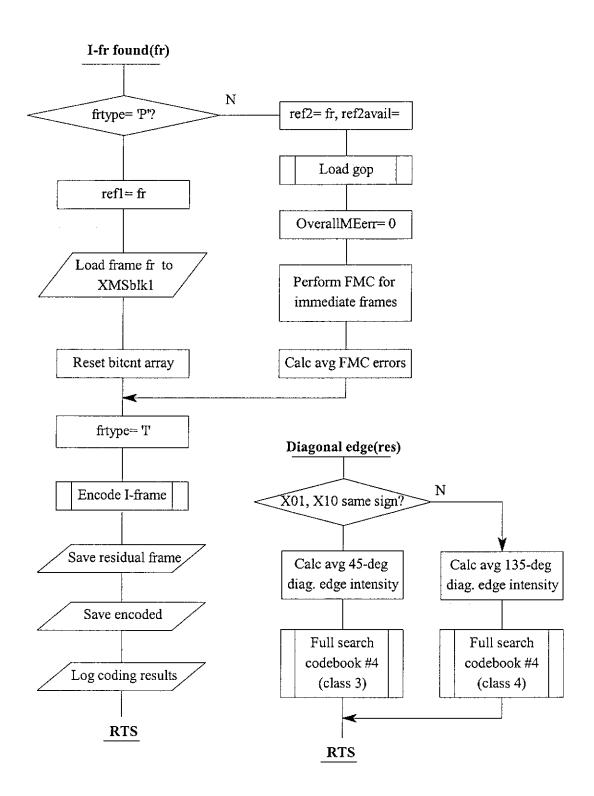

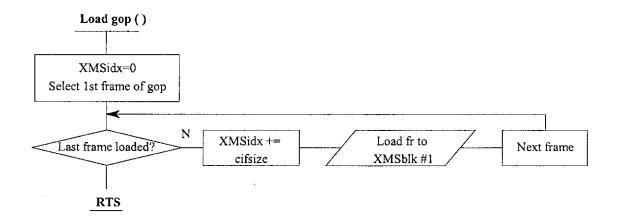

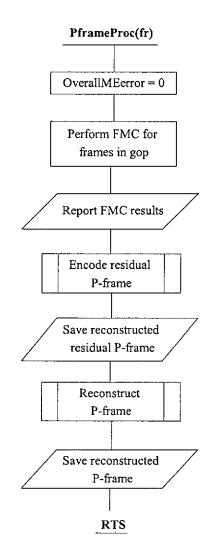

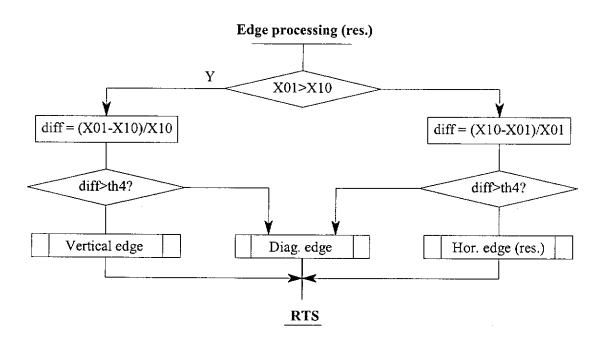

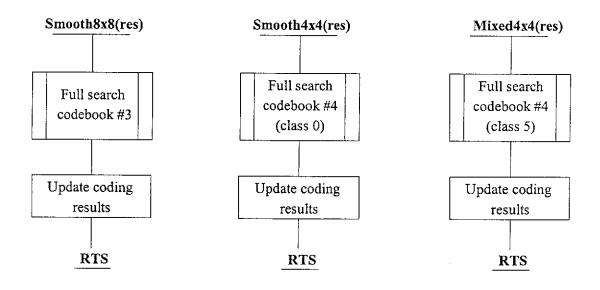

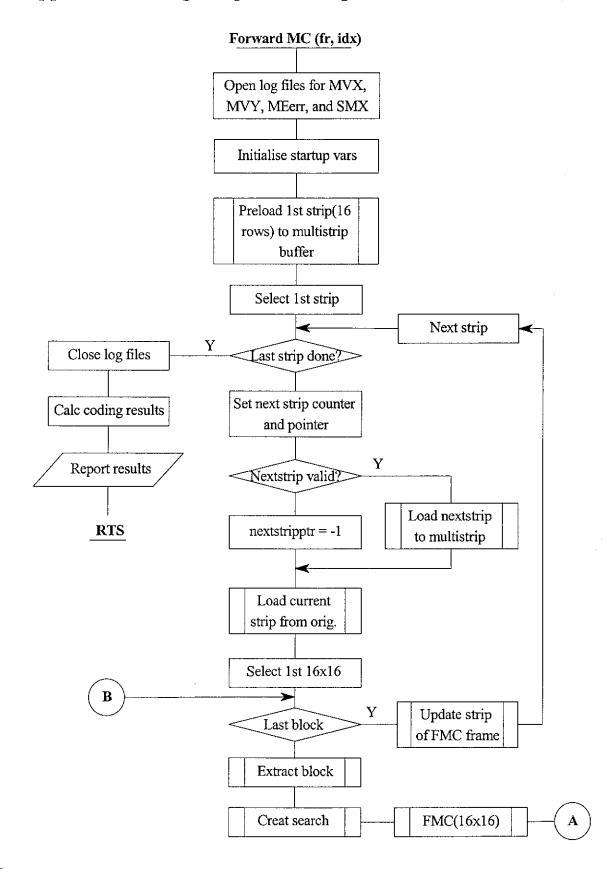

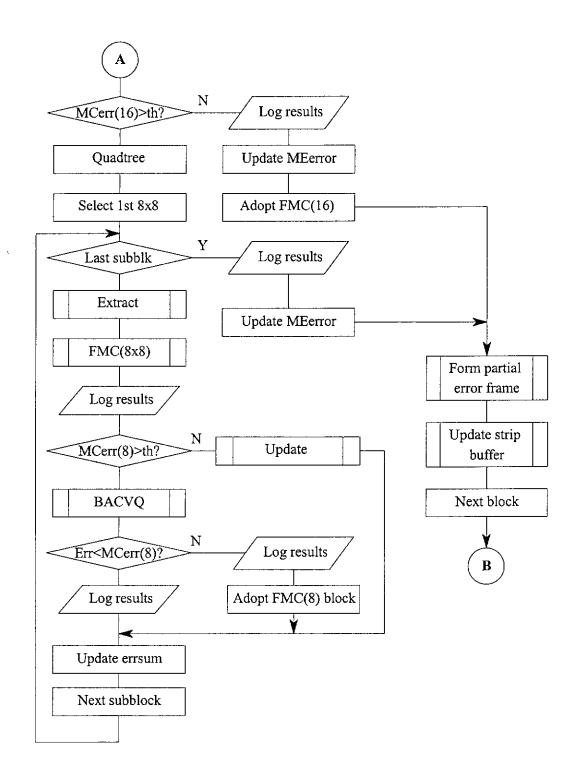

| Figure 3.15: Flowchart for the proposed image sequence compression algorithm        | 109 |

| Figure 3.16: Typical search locations for the proposed motion estimation strategy   | 111 |

| Figure 3.17: Conventional and progressive motion estimation strategies              | 113 |

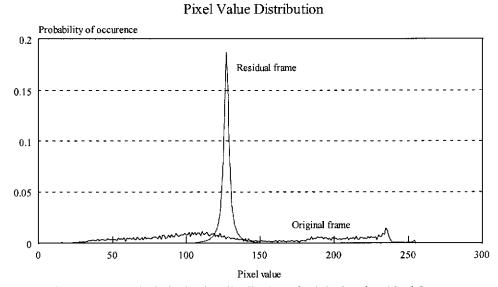

| Figure 3.18: Typical pixel value distribution of original and residual frames       | 116 |

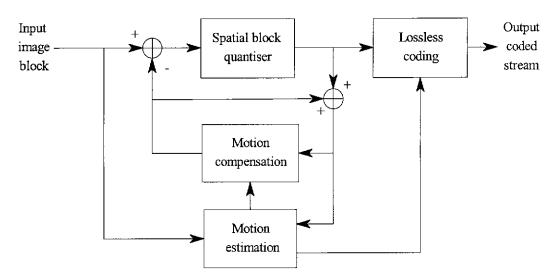

| Figure 3.19: Block diagram of the proposed image sequence compress algorithm        | 117 |

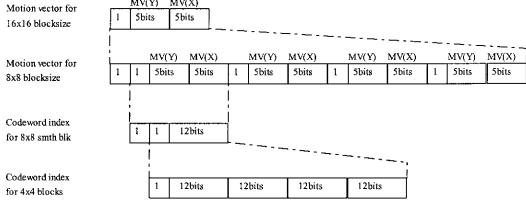

| Figure 3.20: Bit allocation for coding motion vector fields                         | 117 |

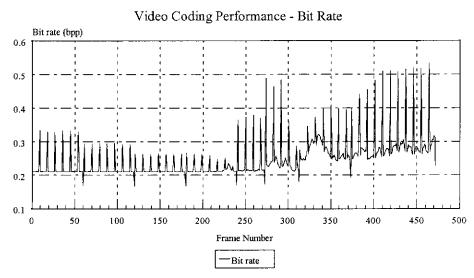

| Figure 3.21: Bit rate performance on the test sequence                              | 118 |

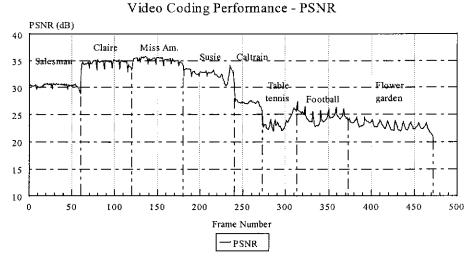

| Figure 3.22: PSNR performance on the test sequence                                  | 118 |

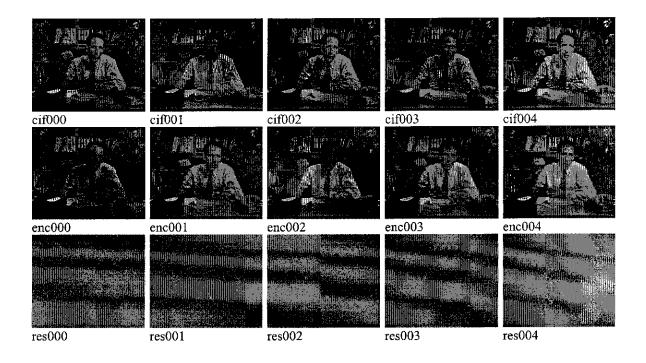

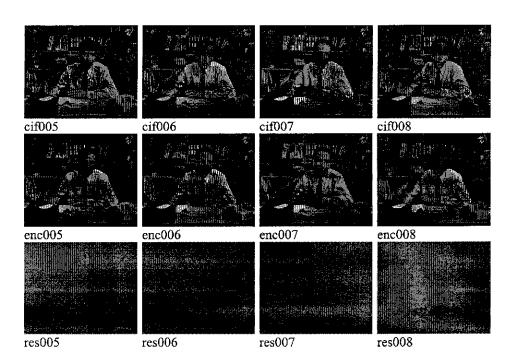

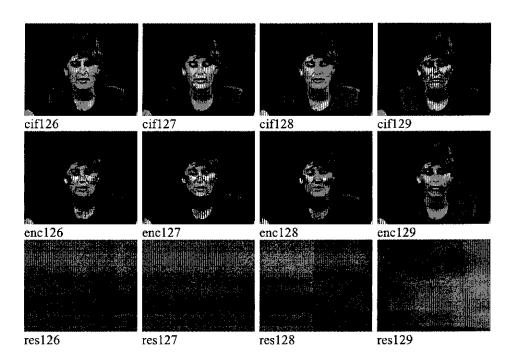

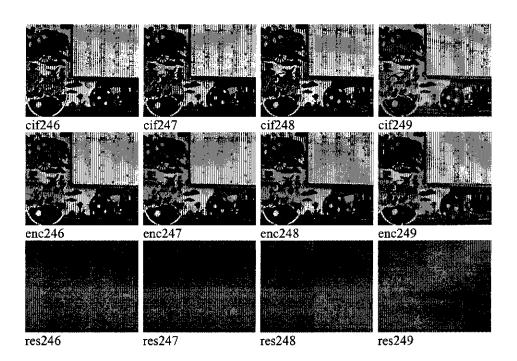

| Figure 3.23: Sample pictures for the "Salesman" test image sequence                 | 124 |

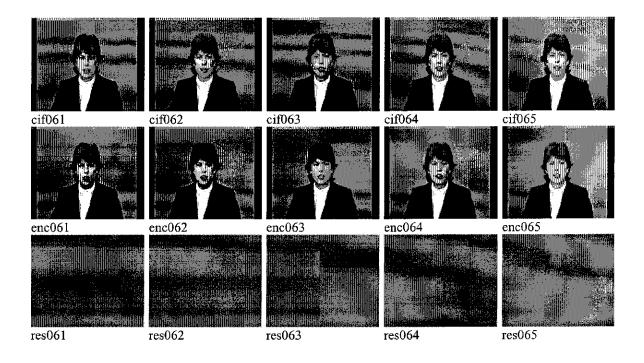

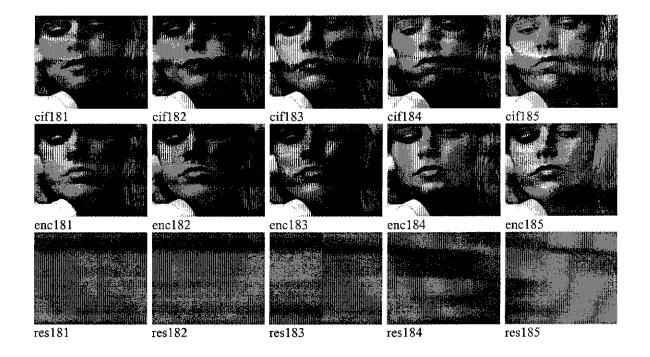

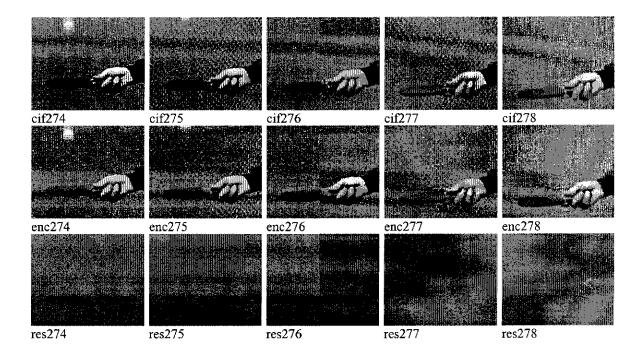

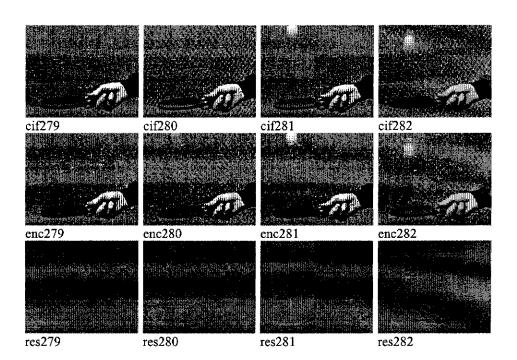

| Figure 3.24: Sample pictures for the "Claire" test image sequence                   | 125 |

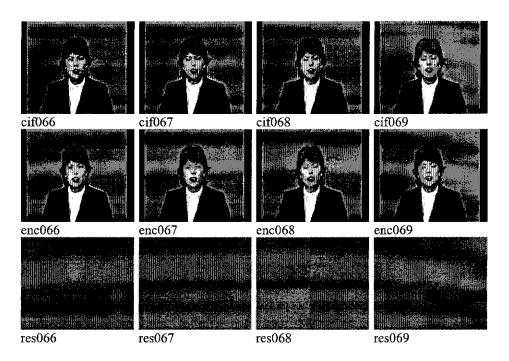

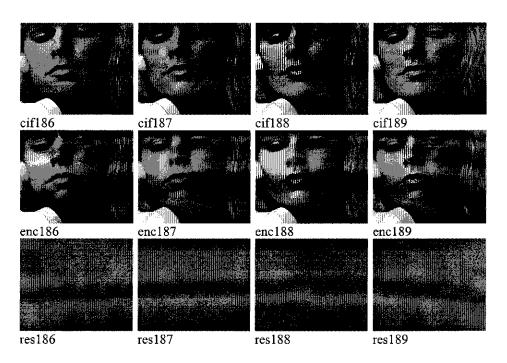

| Figure 3.25: Sample pictures for the "Miss American" test image sequence            | 126 |

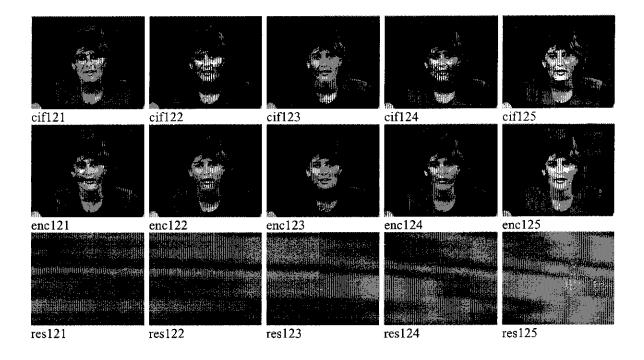

| Figure 3.26: Sample pictures for the "Susie" test image sequence                    | 127 |

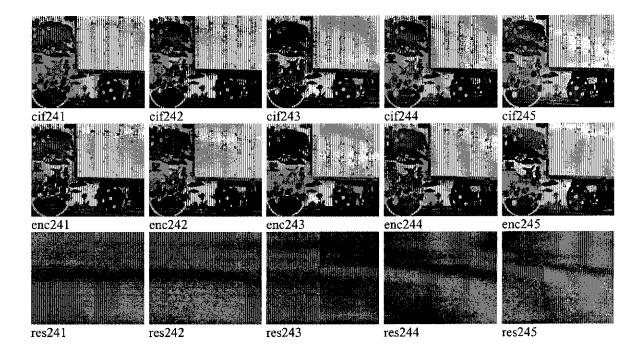

| Figure 3.27: Sample pictures for the "Caltrain" test image sequence                 | 128 |

| Figure 3.28: Sample pictures for the "Table Tennis" test image sequence             | 129 |

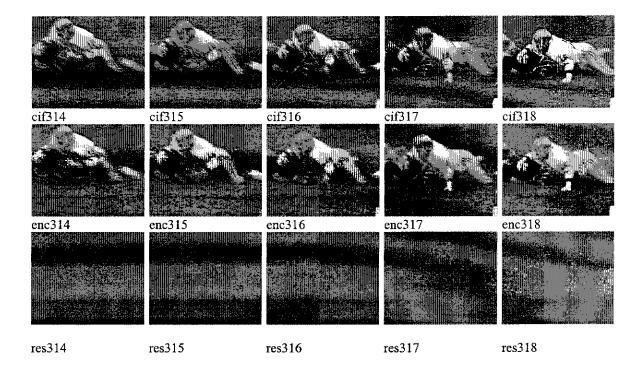

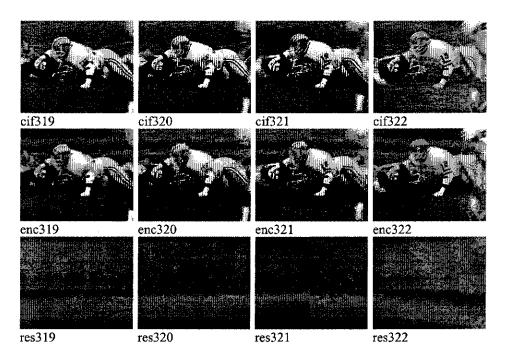

| Figure 3.29: Sample pictures for the "Football" test image sequence                 | 130 |

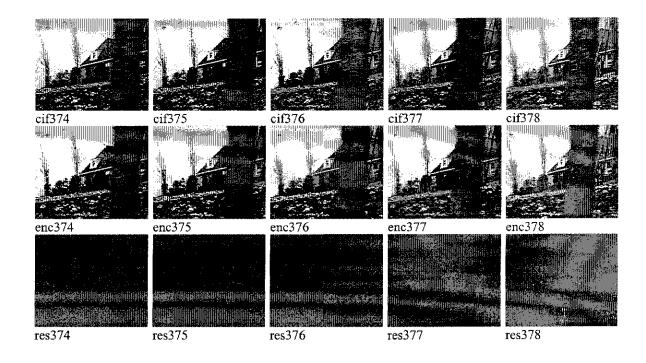

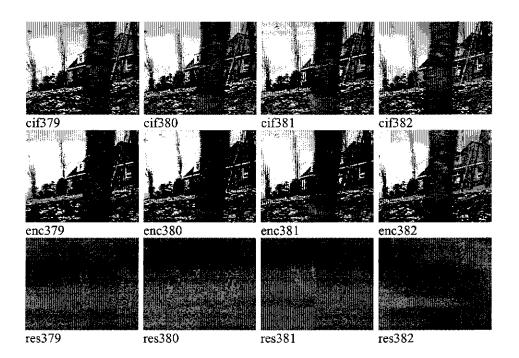

| Figure 3.30: Sample pictures for the "Flower Garden" test image sequence            | 131 |

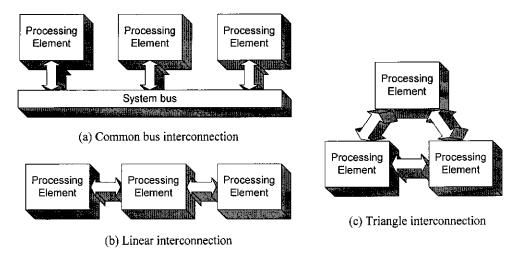

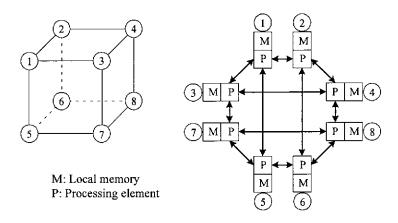

| Figure 4.1: Typical connectivity for a three processing element system              | 141 |

| Figure 4.2: Physical connections of a 3-D hypercube machine                         | 150 |

| Figure 4.3: Pseudo code for message based synchronisation                           | 152 |

| Figure 5.1: Typical processing arrangement of C80-based development system          | 162 |

| Figure 5.2: Block diagram of the prototype parallel DSP platform                    | 166 |

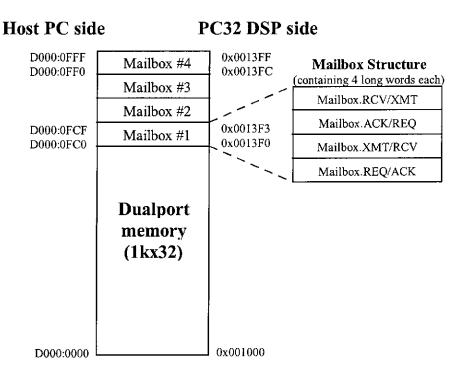

| Figure 5.3: Dualport memory mapping between the host PC and the PC32                | 172 |

| Figure 5.4: Mailbox data structure and its relative position in dualport memory     | 173 |

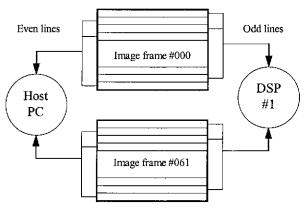

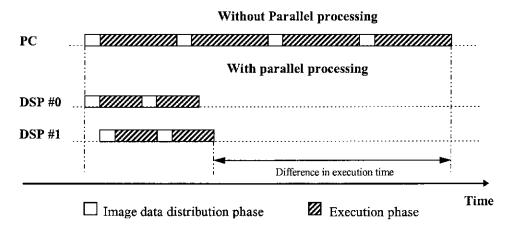

| Figure 5.5: Image data distribution for the moderate parallel processing condition  | 179 |

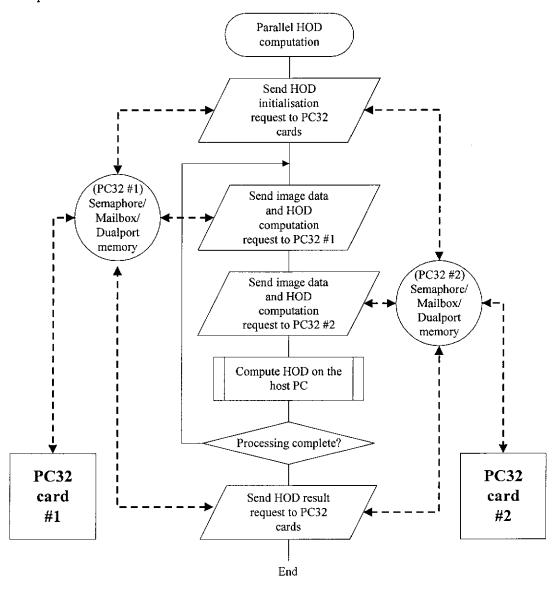

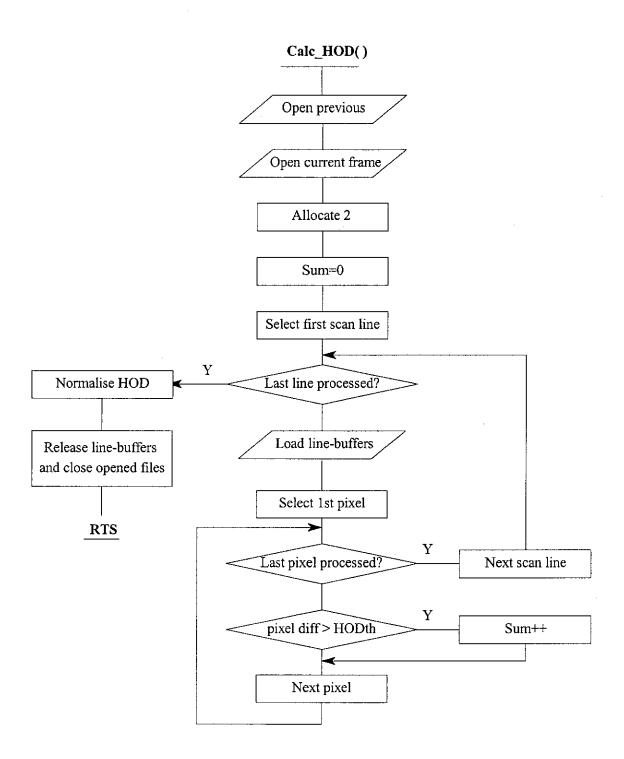

| Figure 5.6: Parallel HOD computation algorithm                                      | 180 |

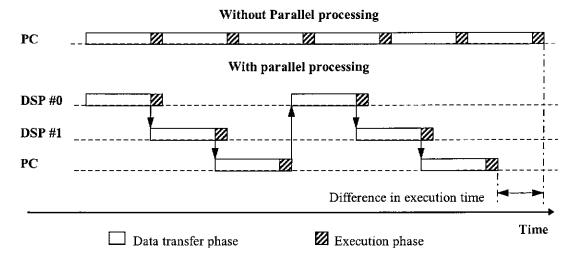

| Figure 5.7: The effect of image data transfer overheads on parallel HOD computation | 182 |

| Figure 5.8: Execution timing for 4x4 image sub-block intraframe processing          | 185 |

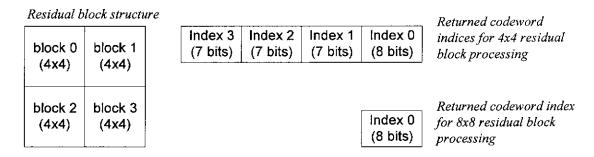

| Figure 5.9: Residual block structure and returned codeword index arrangement        | 194 |

## List of Tables

| Table 2.1: Adaptive allocation of codebook sizes to various edge codebooks     | 67  |

|--------------------------------------------------------------------------------|-----|

| Table 2.2: Results of coding non-training images with BACVQ                    | 67  |

| Table 2.3: Results of coding training images with BACVQ                        | 67  |

| Table 2.4: Results obtained from various BACVQ for non-training image "Lenna"  | 67  |

|                                                                                |     |

| Table 3.1: Maximum search steps and search points for a ±8-pixel search window | 99  |

| Table 3.2: Composition of test image sequence                                  | 105 |

| Table 3.3: BACVQ codebook optimisation for intraframe coding                   | 115 |

| Table 3.4: BACVQ codebook optimisation for residual frame processing           | 116 |

|                                                                                |     |

| Table 5.1: Various HOD computation time for image frame #001 and #061          | 182 |

| Table 5.2: Execution time for processing frame CIF061 as a still image         | 185 |

| Table 5.3: Relative parallel performance gain of various processing stages     | 188 |

| Table 5.4: Performance gain of parallel image sequence compression             | 195 |

## List of Abbreviations

ADSP: Advanced digital signal processor.

BACVQ: Block adaptive classified vector quantisation.

BH: Block histogram difference.

BMA: Block matching algorithm.

BOPS: Billion operations per second.

bpp: Bits per pixel.

BV: Block variance difference.

CTC: Combined transform coding.

CVQ: Classified vector quantisation.

DCT: Discrete cousin transform.

DFT: Discrete Fourier transform.

DHT: Discrete Hartley transform.

DOH: Difference of histogram.

DPCM: Differential pulse-code modulation.

DSP: Digital signal processing or digital signal processor.

DST: Discrete sine transform.

DVD: Digital versatile disc or digital video disc.

GLA: Generalised Lloyd algorithm for VQ codebook optimisation.

GOP: Group of pictures.

HDTV: High definition television.

HOD: Histogram of difference.

HVS: Human visual system.

JPEG: Joint Photographic Experts Group.

KLT: Karhunen-Loeve transform.

LBG: Linde, Buzo and Gray algorithm for VQ codebook optimisation.

LP, BP and HP: Low-pass, band-pass and high pass.

MAE: Mean absolute error.

MCE: Motion compensation error.

ME: Motion estimation.

MEE: Motion estimation error.

MFLOPS: Million floating-point operations per second.

MHOD: Magnitude of HOD variations.

MIMD: Multiple instruction stream multiple data stream.

MIPS: Million instructions per second.

MISD: Multiple instruction stream single data stream.

MPEG: Motion Picture Experts Group

MSE: Mean squared error.

NNQ: Nearest neighbour quantiser.

PE: processing element.

PSNR: Peak signal-to-noise ratio.

QMF: Quadrature mirror filter.

RISC: Reduced instruction set computer

SIMD: Single instruction stream multiple data stream.

SISD: Single instruction stream single data stream.

SSE: Sum of squared errors.

TSVQ: Tree-structured vector quantiser.

VLSI: Very large-scale Integration.

VO: Vector quantisation or vector quantiser.

## **Chapter 1: Introduction**

#### 1.1 Introduction

In human history, establishing communications over a distance has always been an important part of human activities. In the early days, various forms of communications like smoke signals, semaphore, mirror-flashing, drums, light or fire beacons, well-trained pigeons, or even human messengers were used to deliver messages over a distance. All these primitive forms of communications, however, suffer from many disadvantages such as distance limitation, low message-carrying capacity, low speed, unreliability and high cost.

The invention of telegraph and radio transmission in the 19th century has revolutionised the way human beings communicate (Webster's Concise Encyclopedia, 1994). In 1837, telegraph was used mainly as a signalling device over an electrical circuit in British railway systems. Subsequently, the theory of electromagnetic waves was put into practical use in 1895 by Guglielmo Marconi. The significance of Marconi's contribution is that for the first time in human history, human beings have been able to communicate over a distance using radio transmission. After the successful demonstration of radio transmission, Marconi developed wireless telegraph communications to exchange text messages between England and France in 1899 and across the Atlantic in 1901. Radio communication of human speech was then demonstrated in 1906. The development of radio communications has allowed not only news to be broadcast from radio stations to reach larger groups of audience instantly but also education and entertainment programs to be delivered to them more effectively. Most significantly, the invention of black-and-white television in the 1930's and colour television in the 1950's has had even greater impacts on people's lifestyle. Naturally, visual communications have much greater appeal than the voice counterparts, especially when high quality sound and picture transmissions are deployed. Visual communications inherently provide a friendlier atmosphere and more comprehensive coverage for news reporting and offer a more exciting entertainment environment to enhance human experience.

## 1.2 The growing importance of digital technology

In addition to the deployment of various forms of communications, more recent development of digital technology has opened up a whole new world of opportunities. The advent of VLSI and microprocessor technology together with the flexibility and cost effectiveness of digital processing techniques have fuelled the proliferation of digital applications in almost every area of human activities. So much so that it has resulted in a swift transition from analog to digital systems in many fields.

Even in analog environment digital applications have also been widespread. In the music industry, the introduction of digital audio compact discs (CDs) in 1982 has virtually marked the end of an era in which analog phonograph records were used as a recording medium for high quality music reproduction (Ely, 1996). Being recorded in digital form and smaller in physical size, CDs are less susceptible to the encoding of unwanted sounds and to physical damage. Furthermore, CDs improve over conventional records and tape recordings with a more uniform and accurate frequency response, a complete absence of background noise, and a wider dynamic range. Similarly, in the telecommunication industry, digital communications systems have quickly replaced their analog counterparts. This is because digital transmission is more efficient and inherently more robust against circuit deficiencies and transmission impairments. In addition, signal processing in the digital domain is in general far more flexible and cost effective (Zou, 1993). Digital technology has also been applied to photographic imaging whereby a picture is broken up into small dots, called pixels, with average value of light intensity being assigned to each pixel. More recently, digital video and digital television have been actively explored.

Up until the early 1970s, television signals were handled almost entirely in analog forms, that is, video signal of an optical scene was represented as a continuously variable voltage, whose instantaneous value reflected the luminance and chrominance of picture elements being transmitted. However, as digital techniques develop, much of analog video-processing has been replaced by digital signal processing and high-speed sampling that converts continuously varying video signals into digital samples, each representing a discrete signal level. The advantages of handling video signals in

digital forms are that they can be easily manipulated with special effects or used for image overlays or multiple-imaging mixing without any degradation in image quality. In addition, several digital signals can be multiplexed, expediting the transmission and processing of auxiliary information. Also, digital coding provides many benefits for message compression and serves as the basis for interactive telecommunications systems. For cable and direct broadcast satellite television services, digital compression techniques allows their transmission capacity to be instantly increased by more than 10 folds. Digital coding can also be mixed for various media forms, including computer communications on the same carrier, enabling integrated transmission of voice, image, graphics, and data in the same digital data stream.

The emergence of digital versatile disc (DVD) in 1996 marked a new era of consumer video entertainment, in which a digital video format was brought to the mass consumer market for the first time (Ely, 1996). This new format increases the density of the standard 650MB CD to up to 17GB DVD storage capacity, enabling the recording time in MPEG-1 digital video format to be extended from 74 minutes to several hours. In addition, the establishment of various digital compression standards such as H.261 and MPEG-1 and MPEG-2 has contributed significantly to the development of multimedia computing, video-on-demand, digital terrestrial broadcast television, video archiving system, videophone, and video conferencing (Petajan, 1992) (Wright, 1996). Not only has such development of digital technology revolutionised the existing information technology, but it has also brought about the convergence of entertainment, computing, and communications, thereby further enriching human experience.

Being an advanced television standard, high-definition television (HDTV) offers a significantly greater number of scanning lines, and therefore a clearer picture than the conventional 525/625 line television systems (Webster's Concise Encyclopedia, 1994). In 1989, the Japanese broadcasting station NHK and a consortium of manufacturers launched the Hi-Vision HDTV system, an analog HDTV system with 1,125 lines and a wide-screen format. In 1993, however, the United States decided to adopt digital transmission systems for its future HDTV systems. The major

advantage of the proposed U.S. standard for HDTV over the Japanese one is that it is based on digital format. Digital HDTV transmission is preferred to its analog counterpart for several reasons (Aoki, 1994). Firstly, it can be implemented at lower power levels, thus causing significantly less interference with existing television signals, and its quality is also constant throughout a given service area. Secondly, digital TV receivers are more likely to be compatible with a wide variety of computer and telecommunications services. In Australia, the television industry and the government are planning to introduce digital HDTV transmission by Year 2000, coincident with the Olympic Games in Sydney.

Alongside the successful transition from analog to digital, rapid advances have also been made to existing telecommunications infrastructure. Integrated-Services Digital Network (ISDN) has been established as a versatile, high capacity communication networks to provide various digital services such as voice, videophone, computer data or high-quality fax. Satellites have been deployed to provide digital direct broadcasting television services to subscribers. Digital transmission has enabled these satellites to increase the number of television channels substantially. In addition, recent advances in fibre optic technology have led to the deployment of fibre-optic cable instead of the usual copper wire for communications links. While fibre-optic technology has been widely applied in many areas, its greatest impact is perhaps in the field of telecommunications, where optical fibre offers the ability to transmit audio, video, and a variety of digital information. Its advantages over metallic cable include vastly increased information carrying capacity, lower transmission losses, lower cost, much smaller cable size, and almost complete immunity from stray electrical fields or interference.

## 1.3 The importance of digital image compression

Although advances in transmission systems have substantially increased the transmission capability of modern digital telecommunication networks, conserving transmission system resources remains a critical issue. This is mainly because the rapid development of digital imaging and video technology has placed an ever increasing demand on those transmission systems to cater for newer and more demanding applications. Therefore, apart from improving digital system capability,

applying digital compression in general and still image/image sequence compression in particular has been considered as a key approach for dealing with the rapid growth of visual information being exchanged over communication channels or stored in mass storage medium (Gray, 1984).

#### 1.4 Thesis contributions

To date, numerous techniques have already been developed for still image and image sequence compression. However, although considerable effort has been made in developing these techniques, it is generally very difficult for a compression technique to actually achieve optimality in compression performance and computational simplicity simultaneously due to the complexity of the still image/image sequence compression process itself. For this reason, the prime objectives of this research are to explore various possibilities to improve the compression performance of both still image and image sequence compression and at the same time to reduce its computation complexity by adopting more efficient processing operation. In particular, as an alternative approach for still image compression, the proposed Block Adaptive Classified Vector Quantisation (BACVQ) achieves good compression performance and coding efficiency by combining classified VQ and variable blocksize coding technique. More consistent classification and adaptive image-block segmentation algorithms based on both spatial and transform domains have also been developed to further improve the operation of CVQ and variable block-size coding. In addition, highly efficient algorithms have been proposed to accelerate codebook searching operation and to determine the optimal sizes of classified VQ subcodebooks.

For image sequence compression, an adaptive spatial/temporal compression algorithm has been developed with improved compression performance and coding efficiency. To improve the consistency of the scene segmentation process, an adaptive scene segmentation scheme based on the magnitude of the variation in histogram of difference (MHOD) has been developed without adding significant complexity. In addition, a variable block-size motion compensated predictive coding algorithm has been developed to improve the efficiency of the interframe coding process. These improvements include the use of motion estimation errors as a

segmentation criterion to provide more consistent image segmentation operation, the addition of extra search points at the centre of image search windows to eliminate possible motion estimation errors in low motion regions, and the development of an alternative progressive motion estimation strategy to improve the efficiency of motion estimation and to ease implementation difficulties.

Apart from improving still image and image sequence compression algorithms, the application of parallel processing to image sequence compression is also investigated in this study. This is because parallel image compression offers a more effective approach than the sequential counterparts to accelerate the compression process and bring it closer to real-time operation. In particular, because of the independent processing and spatial arrangement natures of most image processing operations, an effective parallel image sequence compression algorithm has been developed to significantly reduce the processing time of the proposed parallel image compression algorithms.

### 1.5 Thesis organisation

The topic of still image compression is investigated in Chapter 2. Following an overview of still image compression in Section 2.1, a discussion of various still image compression techniques is given in the subsequent sections. Typical still image compression techniques include transform coding, subband and wavelet coding, and vector quantisation (VQ). Although VQ has been considered as an optimum compression technique, its computation complexity has severely limited its applications in practice. As such, this has motivated us to develop the proposed block adaptive classified VQ algorithm (BACVQ) for still image compression. A detailed description of the BACVQ algorithm and a discussion of its simulation results are given in Section 2.5, followed by a discussion of lossless compression techniques in Section 2.6.

Various problems relating to lossy image sequence compression are discussed in Chapter 3. Following an overview of various technical issues involved in image sequence compression in Section 3.1, a survey of human visual system is conducted to identify some of its deficiencies which are beneficial to image sequence

compression operations. The importance of scene segmentation and various segmentation criteria are discussed in Section 3.3, followed by an investigation of the operation principle of various motion compensated coding techniques. How adaptive coding techniques such as block size and coding mode adaptation can be applied to improve the performance of image sequence compression is then examined. The basic coding structure of MPEG is briefly discussed in Section 3.6 and some of its terminology has been used to describe the proposed adaptive image sequence compression algorithm in Section 3.7. In this algorithm, a new adaptive scene segmentation technique is investigated, which offers accurate scene transition detection, high tolerance to spurious image activities and computational simplicity. In addition, an alternative approach to variable block-size motion compensation and progressive motion vector estimation is introduced.

Chapter 4 discusses the basic concept of parallel processing. Following an overview of parallel processing in Section 4.1, various parallel processing architectures are discussed. The issues of parallel connectivity are then investigated in Section 4.3. In order to take advantages of parallel processing hardware, considerations must be given to the design of parallel algorithms. Being the most critical operations during parallel processing, process synchronisation, task partitioning and process scheduling are examined in detail in Sections 4.4 and 4.5. To evaluate the performance of digital processing systems quantitatively, various performance measures are described in Section 4.6 with greater emphasis on their accuracy and simplicity. This is followed by a discussion of various issues relating to the design of message-passing and shared-memory MIMD systems.

The topic of parallel image sequence compression is investigated in Chapter 5. Following an overview of parallel image sequence compression and parallel DSP systems in Section 5.1, the characteristics of various commercially available parallel DSP platforms are discussed. The hardware configuration of the proposed prototype parallel DSP platform for the study of parallel still image/image sequence compression and its basic processing operations are described in Sections 5.3 and 5.4. Because dualport memory and semaphore operations contribute significantly to the proper operations of the prototype parallel DSP platform, they are examined in

detail in Sections 5.5 and 5.6. In Section 5.7, the proposed parallel image sequence compression algorithm is described and the performance of the prototype parallel DSP platform is judged by means of experimental results.

Finally, Chapter 6 concludes this thesis with an overall perspective on the algorithms developed and the results obtained in this study. It also provides some recommendations applicable to future research work. Various appendices are included at the end of this thesis to facilitate direct references. While Appendix A to C contain a copy of various conference papers submitted previously, Appendix D to F present the flowchart of the simulation software developed for the studying of still image compression, image sequence compression, and various parallel processing arrangements. Appendix G provides some notes on boot loading operations of the PC-32 cards. While Appendix H presents an example showing some inefficiency in using high level programming, Appendix I provides a sample output of simulation results obtained during the study of parallel image sequence algorithm.

## **Chapter 2: Still Image Compression**

In this chapter, the topic of still image compression is presented because it is an important process not only by itself as a key technique for compressing still images but also for its role in image sequence compression. Although many mainstream compression algorithms have been already developed for still image compression applications, most of them tend to suffer performance or implementation problems to some degree. For this reason, hybrid compression algorithms are more favourable and have been developed aiming at reducing image reconstruction distortion, increasing coding gain, and/or lowering implementation complexity. They enjoy these benefits mainly by combining the advantages of various coding techniques.

Being a hybrid coding algorithm, Block Adaptive Classified Vector Quantisation is presented in this chapter. Its enhanced coding performance is achieved as a result of combining variable block-size coding with classified VQ. Improved image-block classification and codebook generation algorithms have also been developed to provide better classification consistency and to ease implementation issues associated with VQ coding.

#### 2.1 Introduction

Although the rapid technological advance in recent years has enabled many digital systems to expand their system capability substantially in terms of transmission bandwidth and mass storage, conserving system resources remains an important issue. This is mainly because the rapid development of digital imaging technology has imposed an ever increasing demand on those systems to cater for more and more applications involving digital images. Therefore, apart from improving digital system capability, digital image compression also represents a key technology for dealing with the rapid growth of visual information which is exchanged over communication networks or stored on mass storage media (Gray, 1984).

The operation principle of all high performance digital image compression techniques relies heavily on the removal of both statistical and perceptual redundancy within normal images in order to achieve high compression gains. While image

compression techniques based merely on statistical redundancy removal allow original visual information to be fully recovered from compressed data, those based on perceptual redundancy removal or a combination of both do not possess such a property (Fedele et al, 1988). This fundamental difference between these two classes of image compression techniques has led to the development of the so-called lossless and lossy image compression algorithms. In general, while lossless image compression algorithms have very limited compression capability, lossy image compression techniques are capable of offering much higher compression gains but at the expense of some fidelity degradation. Therefore, instead of insisting on perfect reconstruction, lossy image compression techniques are more concerned with preserving the best image fidelity possible for a given rate (Gray et al, 1992). Among the most common lossy image compression techniques are transform coding, subband and wavelet coding, and vector quantisation (VQ).

For many block-based image compression techniques such as transform coding and VQ, coding efficiency can be improved by applying variable block size coding strategy in conjunction with adaptive block segmentation. For image compression applications, it is desirable that perceptually important image areas are segmented into small blocks while low activity regions being segmented into larger ones. This is because not only does this segmentation approach offer higher overall coding efficiency, but it also allows the coding process to achieve uniform spatial distribution of perceptual distortion throughout the reconstructed images, thereby significantly enhancing their perceptual quality. Due to the flexibility and efficiency of quadtree segmentation, most variable block size coding techniques have adopted quadtree segmentation principle during their adaptive block segmentation process (Shusterman et al, 1994) (Vaisey et al, 1992) (Lee & Crebbin, 1994a).

In an effort to improve the consistency of the segmentation process, various assessment criteria for evaluating local image activities within image regions have been reported. In the spatial domain, Vaisey et al (1992) have found that block variance can be used effectively to evaluate local image activities. When the variance of an image block exceeds an empirically determined threshold value, the block shall be considered as being associated with a high detail class, and therefore shall be

segmented into four smaller sub-blocks of equal size. This segmentation process is applied recursively until a low activity sub-block is detected or a minimum sub-block size is reached. Alternatively, image activity measures in the transform domain is also possible. According to Chen et al (1984), the total energy of the AC DCT-coefficients of transformed image blocks can be used as an effective image activity measure.

Being a very important coding algorithm, VQ has attracted considerable interest from the image compression community due to its compression potential. As far as quantisation is concerned, it has been widely acknowledged that optimum quantisation can only be achieved with VQ. However, high quality VQ coding operation usually insists on the use of a very large codebook and high vector dimension, leading to exceptionally high computational cost. Therefore, in an effort to make VQ more practically feasible, recent studies have shown that the coding structure of VQ can be modified with little sub-optimality, thus resulting in the development of various constraint VQs (Vetterli et al, 1992). In particular, classified VQ has been regarded as a typical variant of constraint VQs and its advantages have been well perceived. Not only does it offer a significant reduction in computation complexity as opposed to full-search VQ, but it also plays a key role in enhancing the perceptual quality of reconstructed images. In addition, when combined with variable block size coding, classified VQ would offer even greater performance benefits. As a result, this coding approach has been adopted in the proposed block adaptive classified VQ algorithm (BACVQ).

It should be noted that the performance of classified VQs depends largely on the effectiveness of vector classification process. This is because the extremely high complexity of real images makes it very difficult to maintain consistent classification across all local image textures into their corresponding classes, which in turn affects the efficiency of classified VQs. Therefore, in an effort to improve the classification consistency, various classification schemes operating in either transform or spatial domains have been investigated (Lee et al, 1994a) (Ngan et al, 1992) (Ramamurthi et al, 1986) (Wen et al, 1993). In particular, as a result of this study, an alternative vector classification algorithm operating in both transform and spatial domains has

been proposed. Its operation is based on the use of DCT coefficients, dynamic range and contrast sensitivity. Additionally, dynamic thresholding has been adopted during the classification process in order to exploit the HVS deficiency. As such, this vector classification algorithm was observed to produce highly consistent classification results.

In implementing the proposed BACVQ coding algorithm, a highly efficient partial codebook search approach has been developed for 8x8 codebook search operation. In fact, experimental results have shown that this partial codebook search can offer up to 80% reduction in search time with a small PSNR degradation of 0.03dB. In addition, a new algorithm has been developed for determining the optimal codebook size for classified VQ sub-codebooks. Compared to other codebook size determination methods, the proposed algorithm is capable of determining the optimal codebook size for individual sub-codebooks with significantly reduced computation complexity, especially when large codebook training sets are involved.

And lastly, irrespective of the type of lossy image compression techniques being used in image compression systems, it is a common practice that a statistical encoding technique such as Huffman coding or arithmetic coding is applied as the final stage of the compression process. The aim of this coding stage is to eliminate any remaining statistical redundancy in the coded data stream, and therefore achieving additional compression gain without adding any distortion. This favourable outcome is realised because statistical encoding is basically a lossless compression technique which allows full recovery of the original data (Fedele et al, 1988) (AT&T, 1993).

### 2.2 Transform coding

One of the most popular coding techniques for still image compression is transform coding. Its operation principle is primarily based on orthogonal linear transformation of original signals to the transform domain prior to the quantisation process (Malvar, 1992). As such, its relatively simple coding algorithm coupled with its effectiveness in de-correlating image elements has accounted for its popularity for image

compression applications. In fact, it has been adopted in the specifications of JPEG, a well-known still image compression standard (AT&T, 1993).

Another advantage of applying transform coding to image compression applications is that since natural images do not contain all frequencies, many transformed coefficients in transformed image blocks have zero values, thus representing the redundancy as well as the available compression gain. In an extreme case, for example, a pure grey image block of 16x16 block size effectively has only one DC terms and 255 nil coefficients. This means that a compression gain of 256:1 can be theoretically obtained. Even when these coefficients are not zero, many of them are so small that they fall below visual thresholds and contribute very little to reconstructed image quality. As such, they can be adequately truncated to zero without noticeable visual impairment. This implies higher compression gain is achievable with transform coding when more coefficients of transformed image blocks are set to zero (Ahlgren, 1988).

In general, orthogonal linear transformation can be implemented in various forms. Among the most common forms of orthogonal linear transformation are Karhunen-Loeve transform (KLT), discrete Fourier transform (DFT), discrete Hartley transform, discrete sine transform (DST), and discrete cosine transform (DCT). Although DFT and DCT are very similar in their mathematical formulations, DCT is by far more popular for image processing applications due to its energy compaction efficiency (Malvar, 1992) (Rao et al, 1990).

However, applying conventional DCT coding techniques to image compression applications usually suffers from "blocking" effects because of the discontinuation at block boundaries. In addition, ringing at visual object boundaries is another weakness of DCT coding which severely affects the perceptual quality of reconstructed images. Basically, all these objectionable features occur due to the lossy quantisation of transformed coefficients following the DCT transformation process of image blocks. Therefore, research effort has been recently directed to eliminating such deficiencies of DCT. An example of this is the development of the combined transform coding technique (CTC). Compared to the conventional DCT

approach, CTC has been claimed to offer the desire property of reducing both blocking and ringing effects in addition to improved compression efficiency (Zhang et al, 1993).

From the statistical point of view, KLT is considered as the optimal linear transformation for image compression applications. This is because KLT can ideally produce a set of totally uncorrelated coefficients from the original signals. Furthermore, KLT is capable of maximising the energy compaction in transformed blocks. All of these are regarded as highly desirable features in image compression to lower overall distortion. However, from the practical point of view, KLT has some severe drawbacks when applying to signal coding applications. Firstly, KLT is signal dependent since its transformation requires good modeling of input signal statistics. As a result, efficient implementation of KLT is usually difficult to achieve, especially when signal statistics may change over time and real-time computation is required. Secondly, since the KLT matrix has no particular structure, efficient computation of its transformation is harder to accomplish (Malvar, 1992).

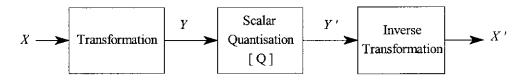

In transform coding, it is a common practice that separate quantisers are used for the quantisation of individual transformed coefficients. This is because transformed coefficients are expected to have different probability distribution functions due to the de-correlation effect of the linear transformation process. A typical transform coding scheme is illustrated in Figure 2.1.

Figure 2.1: Block diagram of transform coding

To assess the performance of a coding scheme, a quantitative distortion measure based on the overall sum of squared errors is frequently used and is given by:

$$D_{TC} = \sum_{i=1}^{k} E[(x_i - x_i)^2] = E[||X - X||^2]$$

where, X and X' represent the original and reconstructed vectors, respectively; and k denotes vector dimension.

An orthogonal transformation of the form Y=TX is normally employed in the above transformation. It is considered as a linear transformation with respect to T satisfying the orthogonality condition, that is,

$$T^t = T^{-1}$$

As distances are preserved in orthogonal transformation, it follows that:

$$D_{TC} = E[||X - X'||^2] = E[||Y - Y||^2]$$

This implies that orthogonal transformation does not magnify quantisation noise so that the sum of squared quantisation errors for the k quantisers is equal to the overall distortion. For this reason, optimal quantisation of transformed coefficients with optimal bit allocation plays a crucial role in determining the overall performance of transform coding.

Zig-zag scanning pattern according to the assigned number

|                          | 1  | 2  | 6  | 7  | 23 | 24 | 28 | 29 |

|--------------------------|----|----|----|----|----|----|----|----|

| Lowest<br>ordered<br>DCT | 3  | 5  | 8  | 13 | 25 | 27 | 30 | 43 |

| coeffici<br>ents         | 4  | 9  | 12 | 14 | 26 | 31 | 42 | 44 |

|                          | 10 | 11 | 15 | 16 | 32 | 41 | 45 | 54 |

|                          | 17 | 18 | 22 | 33 | 40 | 46 | 53 | 55 |

|                          | 19 | 21 | 34 | 39 | 47 | 52 | 56 | 61 |

|                          | 20 | 35 | 38 | 48 | 51 | 57 | 60 | 62 |

|                          | 36 | 37 | 49 | 50 | 58 | 59 | 63 | 64 |

Figure 2:2: A typical zigzag scanning pattern for transformed coefficients quantisation

Apart from separate quantisation, transformed coefficients are commonly quantised in the order of a zigzag pattern (Dufour et al, 1992). The major motivation for this is to achieve better energy compaction, to improve the efficiency of subsequent runlength coding, and to facilitate the implementation of hierarchical coding schemes. For instance, in HDTV compatible coding, the encoded data stream may consist of two components, namely, a compatible data stream and an additional data stream.

The compatible data stream shall contain all the information necessary for the reconstruction of conventional TV sequences. Such a data stream typically contains 16 lowest ordered transformed coefficients of 8x8 DCT blocks following the zigzag scanning process. Subsequently, when inverse DCT is applied to these coefficients, image blocks of 4x4 block size can be reconstructed, which correspond to a lower resolution representation of original 8x8 blocks. In fact, the derivation of conventional TV pictures in this way is equivalent to applying 4:1 decimation to HDTV images. Contrary to the compatible data stream, the additional data stream shall contain extra data necessary for the reconstruction of superior HDTV sequences. Another advantage of the zigzag scanning technique is that it offers a more flexible coding scheme. For example, if a decoder does not receive the total number of transformed coefficients in full, the decoder can simply set the missing coefficients, especially those with higher orders, to zero without affecting its operation. This suggests that the zigzag scanning technique also contributes to the realisation of a more robust coding system. A typical zigzag scanning pattern is illustrated in Figure 2.2.

For image processing applications, linear transformation of image data blocks would theoretically require the application of two dimensional (2D) transformation operators because images are represented as 2D data. However, since image data can also be modelled as separable random processes, separable transformation can be applied without any loss in performance. This means that 2D transform operators can be implemented more efficiently using 1D transform operators and a two-stage computation process. During the first stage, all rows of an image block will be transformed using a 1D transform operator, resulting in an intermediate 2D block. In the second stage, the same transformation is applied to all the columns of the intermediate block to complete the transformation process. Mathematically, this transformation process can be illustrated as follows (Clarke, 1985) (Blinn, 1993):

Assuming, Y, X, and T denote the transformed block, the input block and the orthogonal transformation matrix, respectively, a 2D transformation process based on separable transformation approach can be illustrated as follows:

1) Stage 1: Transform all rows of X

$$B = TX^T$$

where B denotes an intermediate transform vector.

2) Stage 2: Transform all columns of B to complete the 2D transformation process:

$$Y = TB^T = T[TX^T]^T = T[XT^T] = TXT^T$$

#### 2.2.1 Discrete Fourier transform (DFT):

Being a linear transformation, DFT can be described by adopting a general form for the transformation matrix:

$$T = \begin{bmatrix} a_{00} & a_{01} & . & a_{0(M-1)} \\ a_{10} & a_{11} & . & a_{1(M-1)} \\ . & . & . & . \\ a_{(M-1)0} & a_{(M-1)1} & . & a_{(M-1)(M-1)} \end{bmatrix}$$

The basis functions of a transformation matrix can be defined as the columns of the matrix. For DFT, the basis functions are given by:

$$a_{nk} = \sqrt{\frac{1}{M}} \exp \left[ j \frac{2\pi kn}{M} \right]$$

#### 2.2.2 Discrete Hartley transform (DHT):

The basis functions for this transformation are given by:

$$a_{nk} = \sqrt{\frac{1}{M}} cas\left(\frac{2\pi nk}{M}\right)$$

where  $cas(\theta) = cos(\theta) + sin(\theta)$

Since DHT is a real transformation, no complex arithmetic is required during the transformation process. More importantly, since DHT transformation matrix is symmetrical, the direct and inverse transformation processes are identical.

#### 2.2.3 Karhunen-Loeve transform (KLT):

The basis functions for KLT transformation are defined as the eigenvectors of the covariance matrix of the input signal source. For first order auto-regression sources,

such eigenvectors have the properties of being sinusoids whose frequencies are not evenly distributed in a unit circle.

From the statistical point of view, the KLT is considered as the optimal transform (Vetterli et al, 1992). This is because KLT is the only orthogonal transform capable of producing a set of uncorrelated coefficients from a colored source as well as maximising the energy compaction within transformed blocks. This is a highly desirable property for signal coding and signal compression applications.

For linear transformation, the relative coding gain is normally evaluated using the following expression (Malvar, 1992):

$$G_{TC} = \frac{\frac{1}{M} \sum_{k=1}^{M} \sigma_k^2}{\left(\prod_{k=1}^{M} \sigma_k^2\right)^{1/M}}$$

This suggests that KLT maximises the coding gain by minimising the geometric mean of the variance of transformed coefficients in the denominator.

In spite of its desirable properties, applications of KLT to signal coding applications suffer several drawbacks. Firstly, KLT transformation is signal dependent. Therefore, successful applications of KLT are unlikely unless a good model for the source signal statistics can be established, the signal statistics does not change with time, and real-time computation of covariance matrices and eigenvectors is possible. Secondly, since KLT transformation matrix does not have any particular structure, its transformation process does not allow fast computation to be performed.

#### 2.2.4 Discrete Cosine transform (DCT):

The basis functions for this transformation are defined as:

$$a_{nk} = c(k)\sqrt{\frac{2}{M}}\cos\left[\left(n + \frac{1}{2}\right)\frac{k\pi}{M}\right]$$

where

$$c(k) = \begin{cases} 1/\sqrt{2} & if \quad k = 0\\ 1 & otherwise \end{cases}$$

In DCT, when the frequency index k varies from 0 to (M-1), there are M distinct frequencies in the interval  $[0,\pi]$ . As a result, spectral analysis performed with DCT will produce twice the number of frequency bands as opposed to DFT or DHT. In addition, if an input signal has a strong component at a particular DCT frequency but 90 degrees out of phase with respect to a DCT basis function, then the corresponding DCT coefficient will be zero (Malvar, 1992).

## 2.3 Subband and wavelet coding

As an alternative approach to image compression, subband coding can be considered as a frequency domain bit-rate reduction technique (Furukawa et al, 1992). This is because input signals are decomposed into various subbands before compression operation actually takes place. Its development is mainly motivated by the following observations:

- Signal power for high frequency components is generally 40 to 60dB less than the DC power.

- Power spectrum distribution in vertical and horizontal directions are similar.

- Subband coding does not suffer from blocking effects.

- Tree-structured subband decomposition processing facilitates hierarchical coding.

It allows lower resolution images to be more readily accessible from the coding stream.

- The power spectrum of input signals in the logarithmic frequency scale is almost linear except in the very high frequency region.

- Band splitting filters can be implemented using various filter types. However, quadrature mirror filters (QMF) are frequently employed for band splitting operations. In general, band splitting filters must possess such properties as aliasing cancellation, perfect reconstruction, linear phase and good low-pass characteristics in order to minimise coding distortions.

It has been shown that the performance of subband coding is the best when there is a wide variation in the power levels of different subbands. Also, highly correlated signals with high prediction gains are amenable to efficient redundancy removal by

subband coding with the same ultimate performance as being achieved in transform coding. In fact, it can be shown that the worst-case behaviour in terms of reconstruction errors of subband coding is similar to that of DCT due to the close relationship between subband filter banks and unitary transforms. As with DCT coding, ordering subbands according to their energies also helps minimise mean squared errors when a subset of the subbands is used for the reconstruction. This is because the lower bands usually carry basic visual information while the higher ones only adds more detail to the reconstruction (Vetterli et al, 1992).

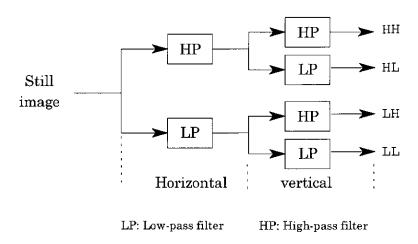

The extension of subband coding to 2D and 3D signals is generally facilitated by the adoption of separable filter banks. For example, in the case of still images where signals are associated with 2D representation over the horizontal and vertical dimensions, a simple subband decomposition can be implemented using separable filter banks as illustrated in Figure 2.3 (Furukawa et al, 1992). These separable filters can be efficiently implemented as row-column filters, which are in turn constructed using 1D QMF filters (Thyagarajan et al, 1987).

Figure 2.3: A typical subband decomposition of still images

However, one of the difficulties in implementing subband coding is that heavily constrained operators have to be used during subband decomposition process. This suggests that a compatible LP channel with reasonable complexity usually cannot produce adequate quality for subband coding operation. What is more, it has been found that maximum reconstruction errors in subband coding are weakly bounded (Vetterli et al, 1992).

For practical reasons, subband coding systems tend to maintain the constraint of critical sampling while relaxing the requirement for an ideal BP filter bank. As such, the filter bank in subband coding is usually replaced with physically realisable filters whose transfer functions are rational functions of  $\exp(j2\pi f/f_s)$  where  $f_s$  represents the sampling frequency. The consequence of this compromise is that some interband interference may occur, thus creating aliasing problems. In order to eliminate this effect, short kernel filters and QMF filters are frequently used for band splitting during subband decomposition process (Coppisitti et al, 1993).

Apart from filter type considerations, there are two other major issues concerning the operation of subband decomposition (Malvar, 1992). Firstly, if incoming signals are simply passed through a set of bandpass filters and their outputs are used directly, the amount of information to be processed would grow proportionally to the number of subbands. This observation suggests that any coding gain achievable by subband coding would be offset by the significant increase in subband information. Fortunately, this is not the case in most situations. In fact, following the band splitting process at the filter bank, subband signals are often sub-sampled or decimated in both horizontal and vertical dimensions, thereby resulting in a 4:1 data compression in each of the subband channels (Malvar, 1992). Secondly, the design of subband filters must be capable of recovering the original signal from its subbands. To meet this requirement, it is necessary that aliasing problems, due to sub-sampling or decimation process primarily, should be eliminated. Malvar (1992) has shown that the frequency spectrum of decimated signals expands with respect to the input signal spectrum by a factor equal to the decimation ratio M. Therefore, if the input signal spectrum is larger than  $\pi/M$ , then as the decimation process takes place, there will be overlapping regions in the spectral replicas, leading to aliasing problems. For this reason, it is a common practice to precede a decimator with a low-pass or band-pass filter with a bandwidth of  $\pi/M$  in order to minimise the possibility of aliasing.

The reverse of the decimation process is known as the interpolation process. Contrary to the decimation process where every *M-th* sample is retained from it original sequence, the interpolation process is implemented by replacing missing samples with zero values. In the frequency domain, this is equivalent to shrinking the

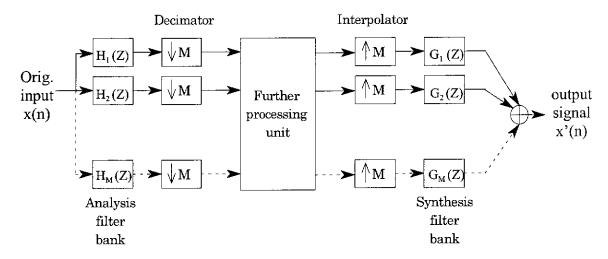

frequency spectrum of the input signal at the interpolator by a factor of M, and replicating this shrunken spectrum (M-1) times (Malvar, 1992). This observation suggests that aliasing is not an issue during the interpolation process. Instead, the output spectrum of the interpolator contains multiple replicas of its input signal spectrum, normally referred to as "imaging". As a result, it is necessary to pass the output signal of the interpolator to a LP or BP filter having a bandwidth of  $\pi/M$  so that only one of the spectral images is retained, thereby enabling a full recovery of the original signal. A typical arrangement of a subband processing system is shown in Figure 2.4.

Figure 2.4: Block diagram of a subband coding system

According to the convolution principle, the output of the k-th analysis filter in Figure 2.4 is given by:

$$X_{k}(i) = \sum_{j=-\infty}^{\infty} x(j)h_{k}(iM - j)$$

and the reconstructed signal is expressed as:

$$x'(n) = \sum_{k=1}^{M} \sum_{i=-\infty}^{\infty} X'_{k}(i) g_{k}(n-iM)$$

If no further processing is applied to the subband signals at the further processing unit, it follows that:

$$X'_{k}(i) = X_{k}(i), \forall k$$

Therefore,

$$x'(n) = \sum_{k=1}^{M} \sum_{i=-\infty}^{\infty} \left[ \sum_{j=-\infty}^{\infty} x(j) h_k (iM - j) \right] g_k (n - iM)$$

Re-organising the summation terms gives:

$$x'(n) = \sum_{j=-\infty}^{\infty} x(j) \sum_{k=1}^{M} \sum_{i=-\infty}^{\infty} h_k (iM - j) g_k (n - iM)$$

In order to achieve perfect reconstruction, Malvar (1992) has showed that the filter banks  $\{H_k(Z)\}$  and  $\{G_k(Z)\}$  must satisfy the following condition:

$$\sum_{k=1}^{M} \sum_{i=-\infty}^{\infty} h_k (iM - j) g_k (n - iM) = \delta(n - j - D)$$

so that,

$$x'(n) = \sum_{j=-\infty}^{\infty} x(j)\delta(n-j-D) = x(n-D)$$

This suggests that when the above condition is satisfied, the overall effect of the subband coding process is simply equivalent to introducing a delay into the original signal. This result is in fact consistent with those presented by Kim (1993), where a different analytical approach has been undertaken.

As mentioned earlier, the decimation process in subband coding plays a key role in reducing subband information associated with individual subband signals. However, the ultimate compression gain of subband coding is in fact achieved by compressing each individual subband signal with an appropriate bit allocation scheme which takes into account not only statistical redundancy in subband signals but also psycho-visual deficiency of human visual system. As such, it allows more bits to be allocated to the lower subbands because of their perceptually importance and less to the higher ones.

Recent studies of human visual characteristics in perceiving visual images have revealed the possibility of achieving high image compression with minimal image impairment using subband coding (Kim, 1993). Specifically, it has been found that human visual system seems to exhibit LP filtering in the temporal domain and BP in the spatial domain. Therefore, subband coding presents a sensible approach because it offers an efficient way to exploit this result, in which more emphasis is placed on lower bands while components of higher bands can be progressively eliminated.

As an alternative approach, discrete wavelet coding can be applied equally well to image compression applications. From the theoretical point of view, discrete wavelet

coding can be considered as a special form of subband coding with a logarithmic decomposition tree structure. The application of the logarithmic tree structure in discrete wavelet coding enables the doubling of image resolution every time a wavelet channel is added. Basically, the development of discrete wavelet coding has been motivated by recent studies of human visual system modeling. Various psychovisual experiments have suggested that the retinal processing in human eyes uses independent BP filters which are almost linear and have a constant relative bandwidth of about 1 octave among them. Therefore, if one assigns a roughly constant number of bits per octave, it is then possible to maintain equally perceived quality across filtered channels (Vetterli et al, 1992).

The filter bank used in wavelet coding is usually constructed using a special type of LP filter called regular filters. These regular LP filters possess the same properties of orthogonality and linear phase as normally exhibited by subband filters. In addition, when connected in a cascade filter/sub-sampling configuration, these filters tend to produce a smooth equivalent impulse response. It is the smoothing feature of these regular LP filters that results in very little energy being retained in the high bands during the wavelet analysis process, hence significantly enhancing the performance of subsequent compression operations. However, if the above regularity property is not satisfied, this may result in equivalent filters with fractal impulse response, which in turn affects the reconstruction of the signal (Vetterli et al, 1992).

# 2.4 Vector quantisation

#### 2.4.1 Overview

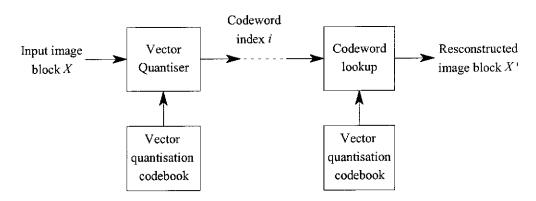

Vector quantisation (VQ) is typically a lossy compression technique for signal compression applications. A general coding structure of vector quantisation is presented in Figure 2.5. Conceptually, vector quantisation can be regarded as Shannon's model of source coding. Its central idea is to encode signal samples as a group instead of one at a time as in the case of scalar quantisation, resulting in a more efficient way to exploit the redundancy among signal samples.

As Gersho & Gray (1992) have demonstrated, a regular VQ can be visualised as having a polytopal structure in which each cell in the partition is a convex polytope.

For a k-dimension polytopal structure, the (k-1) dimensional faces of the cells constitute hyperplane segments. These hyperplane segments serve as boundaries among polytopal regions in the entire structure. In general, the number of hyperplanes typically bounding a polytope increases very rapidly with respect to its space dimension. This result partially explains why the complexity of VQ encoders grows dramatically with increased vector dimension.

Figure 2.5: Block diagram of vector quantisation coding systems

Statistically, for the same total bit allocation, it has been proven that VQ indeed offers better performance than scalar quantisation because its coding algorithm allows it to exploit the redundancy among vector samples more efficiently. In addition, it has been found that VQ is capable of offering compression gain not only when correlation exists among vector components but also in the case where little correlation is anticipated. Other advantages of VQ include (Gray et al, 1992):

- The ability to exploit both linear and non-linear dependency among vector components;

- The extra freedom in choosing multi-dimensional quantiser cell shapes;

- Offering fixed coding rates in the case of conventional vector quantisation;

- The flexibility in setting codebook size and choosing arbitrary partitions;

- The simplicity of the decoding process because its decoding algorithm is basically based on table look-up operations and requires very little computation;