# Australian Telecommunications Research Institute

New Techniques for Measurement and Tracking of Phase and Frequency

**Martin Terence Hill**

This thesis is presented as part of the requirements for the award of the Degree of Doctor of Philosophy of the Curtin University of Technology.

#### Abstract

This thesis presents and analyses new techniques to measure and track the phase and frequency of high frequency narrow bandwidth signals. In particular, these techniques are all digital in nature or can be implemented in digital integrated circuit technology.

Presented first is a frequency measurement technique which involves sampling at regular intervals a binary quantized narrow band signal. The binary quantized samples are digitally processed to obtain the instantaneous frequency of the signal.

It is shown that small phase movements in the signal can be detected even though the sampling occurs at a rate much lower than the signal frequency; that there are no frequency offsets in the frequency measurement technique; that the phase error in the technique is small and bounded provided the signal frequency is maintained within derived limits. Other properties of the technique are also derived.

The frequency measurement technique is experimentally demonstrated in a number of typical applications.

Secondly, a new phase tracking system is presented, which has similarities to conventional phase locked loops. However, unlike phase locked loops, the new system incorporates a local reference source which effectively stabilizes the phase estimate of the signal input being tracked.

It is shown that the new system has the following advantages: Precise centre frequency, controllable lock range, and elimination or reduction of the effects of imperfections like voltage controlled oscillator phase noise. General behaviour in noise of the new phase tracking system is derived.

An implementation of the new system is presented which employs the frequency measurement technique described above. This implementation is characterized by very precise centre frequency, high phase noise suppression, and can be built almost entirely in digital integrated circuit technology. The new system is experimentally demonstrated in some typical applications.

The techniques presented in this thesis provide improvements of several orders of magnitude in the ability of systems implemented in digital integrated circuit technology to: Measure and control phase and frequency of narrow band signals; Implement high performance phase tracking systems.

# Contents

| Chapter | 1 | Introduction                                                 | 1  |

|---------|---|--------------------------------------------------------------|----|

|         |   | 1.1. Introduction 1                                          |    |

|         |   | 1.2. Contributions of Thesis 4                               |    |

|         |   | 1.3. Structure of Thesis 5                                   |    |

| Chapter | 2 | Digital Frequency Measurement of a Square Wave               | 6  |

|         |   | 2.1. Introduction 6                                          |    |

|         |   | 2.1.1. Outline of Chapter 2 8                                |    |

|         |   | 2.1.2. Contributions of Chapter 2 9                          |    |

|         |   | 2.2. Overview of PDFD Operation 10                           |    |

|         |   | 2.2.1. Basic Terms and Definitions 10                        |    |

|         |   | 2.2.2. PDFD Operation 10                                     |    |

|         |   | 2.3. The Simple Frequency Detector 13                        |    |

|         |   | 2.4. The PDFD, an Array of Simple Frequency Detectors 16     |    |

|         |   | 2.5. Operating Limits 19                                     |    |

|         |   | 2.6. Generalized Sampling Rate 22                            |    |

|         |   | 2.7. Operating Limits for Generalized Frequency Detectors 23 |    |

|         |   | 2.8. Instantaneous Error 25                                  |    |

|         |   | 2.9. Spectral Characteristics 27                             |    |

|         |   | 2.10. PDFD Operation for Time Varying Frequency 31           |    |

|         |   | 2.11. Summary 31                                             |    |

| Chapter | 3 | A Frequency Steered Phase Locked Loop                        | 32 |

|         |   | 3.1. Introduction 32                                         |    |

|         |   | 3.1.1. Outline of Chapter 3 35                               |    |

|         |   | 3.1.2. Contributions of Chapter 3 36                         |    |

|         |   |                                                              |    |

|         |   |      | 3.2.1. Analysis of SFPLL 37                                 |    |

|---------|---|------|-------------------------------------------------------------|----|

|         |   |      | 3.2.2. Phase Tracking System with VCO stabilized by Phase   |    |

|         |   |      | Locking 42                                                  |    |

|         |   | 3.3. | Noise Performance of a Class of SFPLLs 44                   |    |

|         |   |      | 3.3.1. SFPLL with Additive Noise 45                         |    |

|         |   | 3.4. | Type II SFPLL Transfer and Step Response Characteristics 49 | 9  |

|         |   |      | 3.4.1. Transfer Function Characteristics 51                 |    |

|         |   |      | 3.4.2. Step Response Characteristics 56                     |    |

|         |   | 3.5. | Effects of VCO Phase Noise and Parameter Variations 58      |    |

|         |   |      | 3.5.1. Effects of Parameter Variations on Bandwidth 58      |    |

|         |   |      | 3.5.2. Effects of VCO Phase Noise on SFPLL Performance      | 59 |

|         |   | 3.6. | Simulation of SFPLL with Additive Noise 61                  |    |

|         |   | 3.7. | Digital Implementation 63                                   |    |

|         |   |      | 3.7.1. Filter Realization 64                                |    |

|         |   |      | 3.7.2. Frequency Detector and Frequency Loop 64             |    |

| •       |   |      | 3.7.3. VCO and Phase Detector 66                            |    |

|         |   | 3.8. | Experimental SFPLL 66                                       |    |

|         |   |      | 3.8.1. SFPLL System 66                                      |    |

|         |   |      | 3.8.2. Results 67                                           |    |

|         |   | 3.9. | Summary 68                                                  |    |

| Chapter | 4 | Арр  | olications of the PDFD                                      | 70 |

|         |   | 4.1. | Introduction 70                                             |    |

|         |   | 4.2. | Demodulation of a Frequency Modulated Signal 71             |    |

|         |   |      | 4.2.1. Modulation Format and PDFD Parameters 71             |    |

|         |   |      | 4.2.2. PDFD Realization and Demodulation System 72          |    |

|         |   |      | 4.2.3. Results 73                                           |    |

|         |   |      | 4.2.4. Demodulation for Signals in Noise 73                 |    |

|         |   | 4.3. | Frequency Synthesis 75                                      |    |

|         |   |      | 4.3.1. Requirements and PDFD Parameters 75                  |    |

|         |   |      | 4.3.2. Frequency Synthesis System 75                        |    |

|         |   |      | 4.3.3. Results 78                                           |    |

|         |   |      |                                                             |    |

3.2. The SFPLL and its Linear Model 37

| Chapter   | 5  | Applications of the SFPLL                                        | 79  |

|-----------|----|------------------------------------------------------------------|-----|

|           |    | 5.1. Introduction 79                                             |     |

|           |    | 5.2. Synthesis of High Rate Clock from Low Rate Reference in the | ıe  |

|           |    | Presence of Jitter 80                                            |     |

|           |    | 5.2.1. Introduction 80                                           |     |

|           |    | 5.2.2. SFPLL Realization 80                                      |     |

|           |    | 5.2.3. Results 81                                                |     |

|           |    | 5.3. Demodulation of a Frequency Modulated Signal 83             |     |

|           |    | 5.3.1. Introduction 83                                           |     |

|           |    | 5.3.2. SFPLL Realization 84                                      |     |

|           |    | 5.3.3. Results 85                                                |     |

| Chapter   | 6  | SFPLL Implementation with Simple Frequency Measurement           | 86  |

| -         |    | 6.1. Introduction 86                                             |     |

|           |    | 6.2. System Overview 87                                          |     |

|           |    | 6.2.1. Phase and Frequency Detectors 89                          |     |

|           |    | 6.3. Phase Loop Parameters 90                                    |     |

|           |    | 6.4. Frequency Loop Parameters 92                                |     |

|           |    | 6.5. Disturbance Reduction 93                                    |     |

|           |    | 6.6. Frequency Loop Filter 94                                    |     |

|           |    | 6.7. Experimental Results for SONET STS-3c Clock Recovery        | 15  |

|           |    | 6.8. Summary 97                                                  |     |

| Chapter   | 7  | Conclusion                                                       | 98  |

|           | -  | 7.1. Further Work 98                                             | 30  |

|           |    | 7.2. Conclusion 99                                               |     |

|           |    |                                                                  |     |

| Reference | es |                                                                  | 102 |

| Appendix  | A  | PDFD Derivations                                                 | 108 |

|           |    | A.1. Introduction 108                                            |     |

|           |    | A.2. Simple Frequency Detector Operation 108                     |     |

|           |    | A.3. Operating Limits 111                                        |     |

| Appendix C | Development of a BRM Based Digital Filter          | 126 |

|------------|----------------------------------------------------|-----|

|            | B.2. Fokker-Planck Operator 123                    |     |

|            | B.1. Introduction 123                              |     |

| Appendix B | Eigenfunctions of Fokker-Planck Operator           | 123 |

|            | A.5.2. The Array of Simple Frequency Detectors 119 |     |

|            | A.5.1. Simple Frequency Detector Operation 116     |     |

|            | A.5. PDFD Operation for Time Varying Frequency 115 |     |

|            | A.4. Instantaneous Errors 113                      |     |

# Introduction

#### 1.1. INTRODUCTION

High frequency signals in electronic systems often require some type of signal processing. Current signal processing techniques typically rely on either down conversion using heterodyning followed by high speed analog to digital conversion and digital processing. Or the use of analog systems to perform the signal processing.

Considerable effort has gone into developing sophisticated digital signal processing techniques [1],[2]. However, less attention has been paid to developing techniques to digitally perform even simple signal processing, without down conversion and analog to digital conversion [3].

In some applications the use of high speed analog to digital conversion and digital processing may not be possible due to: The nature of the signal is not suitable for down conversion. Or the cost and complexity of the converters and digital processing is considered excessive.

This thesis presents and analyses new techniques to measure and track the phase and frequency of high frequency narrow bandwidth signals. In particular these techniques are all digital in nature or can be implemented in digital integrated circuit technology. The techniques do not employ down conversion via heterodyning, or analog to digital converters.

The techniques presented in this thesis are applicable to a number of common, simple signal processing tasks. For example, modulation and demodulation of narrow bandwidth signals, frequency synthesis, and filtering [5],[4].

The techniques presented are also experimentally demonstrated in typical applications to:

- Verify the theoretical results.

- Demonstrate the simplicity and elegance of the implementations of the new techniques, and the ease of application to common problems.

- Highlight the high performance that can be achieved.

Two related techniques for measuring and tracking phase and frequency are described: a frequency measurement technique, and a phase tracking system.

The frequency measurement technique involves sampling at regular intervals a narrow band signal which has been binary quantized. That is, the narrow band signal can be represented by a square wave. The binary quantized samples are digitally processed to obtain the instantaneous frequency of the signal.

The frequency measurement technique has the advantages that: It is constructed from simple digital components such as logic gates and flip flops. Small phase changes in the signal square wave can be detected even when the frequency measurement system is clocked at a low rate.

Properties of the new frequency measurement technique are derived. It is shown that there are no frequency offsets, also that the phase error in the technique is small and bounded provided the signal frequency is maintained within derived limits. It is highlighted that the frequency measurement technique is most suited for very narrow bandwidth signals. The spectral characteristics of the frequency estimator are also derived.

The frequency measurement technique is demonstrated in typical applications, specifically frequency synthesis and demodulation of a high frequency signal.

The new phase tracking system presented has similarities to conventional phase locked loops. However, unlike phase locked loops [6], the new system incorporates a stable and accurate local reference signal source.

The local reference source effectively stabilizes the phase estimate of the signal input being tracked. The stabilization is achieved via a frequency difference measurement between the local reference and the phase tracking system output.

A small signal model of the new phase tracking system is presented and some properties derived. The general non-linear behaviour is also derived for some important classes of the new phase tracking system, specifically when the input signal is corrupted with noise. Further properties are derived, including the effects of component imperfections like voltage controlled oscillator phase noise.

The analysis results show that the new phase tracking system has significant advantages such as: Very precise and controllable centre frequency. The range of frequencies to which the phase tracking system can lock, can be confined to a small and controllable region around the local reference. The effects of voltage controlled oscillator phase noise can be reduced to an insignificant level.

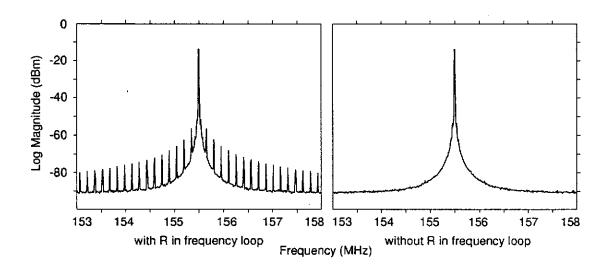

The centre frequency and phase noise advantages are particularly important when the phase tracking system employs voltage controlled oscillators made in digital integrated circuit technology. The phase noise reduction advantage is dramatically illustrated in the experimental results of one of the example applications.

Many frequency measurement techniques can be used in an implementation of the new phase tracking system. However, an implementation employing the new frequency measurement technique presented first in this thesis, is described. This particular implementation is characterized by very precise centre frequency, high phase noise suppression, and can be built almost entirely in digital integrated circuit technology.

As mentioned previously the new frequency measurement technique is restricted to signal inputs of narrow bandwidth. In contrast, the new phase tracking system can have broadband signal inputs. Hence, the new phase tracking system can also be thought of as providing a broadband interface for the new frequency measurement technique.

The new phase tracking system is experimentally demonstrated in the application of demodulation of a frequency modulated signal. Furthermore, it is demonstrated in the application of a very narrow bandwidth phase locking system. The narrow bandwidth

system is used to synthesize a high rate clock from a low rate reference [7], and also provide filtering for the jitter and noise on the low rate reference.

Aspects of this thesis have been reported in [8], [9], [10] and are the subject of two patent applications [11], [12].

Furthermore, a clock recovery system in a digital application specific integrated circuit employed the new phase tracking system. The digital integrated circuit, integrated functions ranging from clock recovery, physical layer framing, to asynchronous transfer mode cell switching.

#### 1.2. CONTRIBUTIONS OF THESIS

The contributions of this thesis are as follows:

- The proposal of a new frequency measurement technique which involves sampling at regular intervals a binary quantized narrow band signal.

- The analysis of the frequency measurement technique, deriving its operating limits and errors that arise.

- The proposal of a new phase tracking system, which diminishes or overcomes many problems associated with phase locked loops.

- The development of models to quantitatively describe the behaviour of the new phase tracking system. Furthermore the verification of these models and analysis results through simulations and experiments.

- The proposal of a digital implementation of the new phase tracking system,

which provides a high precision low cost realization.

#### 1.3. STRUCTURE OF THESIS

In the introduction of the chapters describing the frequency measurement technique and phase tracking system, the relevant existing techniques are referenced and described.

This thesis is organized as follows:

In Chapter 2 the new frequency measurement technique is described. Various properties and operating limits of the frequency measurement method are derived.

In Chapter 3 the new phase tracking system is described. Models are proposed to describe the behaviour of the new phase tracking system, and key properties are derived from these models. A digital implementation of the new phase tracking system is proposed. Experimental verification of the properties derived from the models confirms the accuracy of the models and analysis.

In Chapter 4 the new frequency measurement technique is experimentally demonstrated in typical applications. Experimental results verify the operation of the new frequency measurement technique.

The new phase tracking system is demonstrated in typical applications in Chapter 5.

An implementation of the new phase tracking system employing another frequency measurement technique is presented in Chapter 6. The frequency measurement technique is very simple, but some benefits such as phase noise reduction cannot be obtained when it is employed. However, this particular implementation is useful for applications with undemanding phase noise requirements, such as clock recovery.

Finally, Chapter 7 gives suggestions for further work and concludes the thesis.

# Digital Frequency Measurement of a Square Wave

#### 2.1. INTRODUCTION

This chapter describes a new digital method to measure the frequency difference between two square waves. For convenience the new method is called the *precise* digital frequency detector (PDFD) (patent pending).

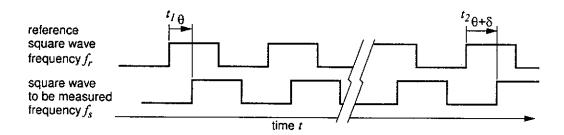

Figure 2-1 illustrates the task that is addressed by the PDFD. At time  $t_1$  the reference square wave leads the signal square wave by  $\theta$ , at time  $t_2$  the relative phase lead has increased a small amount to  $\theta+\delta$ , because of a difference in frequency. The PDFD must be able to detect these small relative phase movements and indicate the appropriate difference in frequency.

Figure 2-1. Frequency Measurement of a Square Wave. The frequency measurement needs to detect small phase movements between the two square waves, possibly occurring over many cycles.

It is assumed that the phase slipping of the signal square wave of frequency  $f_s$  relative to a reference square wave of frequency  $f_r$  occurs over several reference cycles, that is

$$|f_r - f_s| \ll f_r \tag{2-1}$$

We assume that the frequency  $f_r$  is constant and is the 'nominal' or 'expected' frequency of the signal to be measured of frequency  $f_s$ .  $f_s$  may be constant or time varying. In many PDFD applications the reference square wave signal of frequency  $f_r$  need not exist. However, as will be shown later, to design the PDFD the value  $f_r$  needs to be known.

**Previous Work.** Many methods have been described to measure the frequency of a square wave signal, the methods are divided here into three classes:

- Digital methods.

- Analog methods

- Mixed methods employing analog to digital converters with some analog processing of the square wave.

The existing digital methods can only detect large phase movements between the signal and reference (typically a complete cycle)[13]. Or, they require clock rates much higher than the signal frequency to measure small phase movements. These need to measure accurately the period or difference in phase of every signal clock cycle, thus limiting their application to moderately low frequencies [14],[15]. Some methods employ delay line time digitizers to accurately measure the period of every signal clock cycle without resorting to high clock rates [16]. Unfortunately these methods require delay elements with very small and accurate delays which require full custom integrated circuit design. Furthermore application to high signal frequencies is again limited.

The analog methods are able to detect small phase changes between the signal and reference. Some examples are the quadricorrelator [17], and classic FM discriminators involving the differentiation of the signal by use of tuned filters or time delays [18]. Some examples of mixed analog digital methods are, heterodyning the signal to a much lower frequency whose period can be accurately measured digitally [15],[19]. Converting the square wave to a sine wave by low pass filtering and / or down conversion, then digitizing the waveform using analog to digital converters. There is a

significant amount of literature on using the samples to determine the frequency of the signal [14],[1],[2]. A mixed analog digital method employing analog integration and delta-sigma modulation techniques is presented in [3].

In contrast to the current techniques described above, the PDFD involves sampling the square wave at discrete times. Typically employing a flip flop as the sampler. The binary quantized samples are then digitally processed to obtain the phase movement between the signal and reference square waves.

The PDFD has the following important advantages over the current techniques just described. It can be constructed from simple digital components such as logic gates and flip flops. Small phase movements between the signal and reference square waves can be detected, even when the PDFD is clocked at low rates. Finally, as will be shown, the PDFD has no frequency offsets.

#### 2.1.1. Outline of Chapter 2

This chapter is organized as follows:

Section 2.2 provides an overview of the PDFD operation to aid in the understanding of the more detailed descriptions which follow.

In Section 2.3 equations which describe the operation of the simple frequency detector are derived.

Section 2.4 further details how PDFDs can be implemented using an array of simple frequency detectors and how the output of the array is processed.

Section 2.5 details how to design a PDFD with uniform starting phases and derives operating limits for the PDFD. The operating limits of the PDFD are also discussed.

Section 2.6 generalizes the sampling rate of the PDFD.

Section 2.7 details how to design a PDFD and derives operating limits when the generalized simple frequency detectors described in Section 2.6 are used in the PDFD.

Section 2.8 derives some further limits on the PDFD operating range.

In Section 2.9 the spectral characteristics of the frequency estimator output by the PDFD are determined.

Section 2.10 states that the results on PDFD operating limits are valid when the frequency of the signal square wave is time varying.

Finally, Section 2.11 summarizes the chapter.

Also in Appendix A some derivations concerning aspects of the PDFD are given.

#### 2.1.2. Contributions of Chapter 2

The all digital measurement of small phase movements in a square wave without resorting to high clock speeds has not been described in the literature.

The contributions of this chapter are as follows:

- The proposal of the PDFD method to measure the frequency of a square wave. The advantages the PDFD has over current techniques are given above.

- The analysis of the PDFD, deriving its operating limits and errors that arise in the PDFD.

#### 2.2. OVERVIEW OF PDFD OPERATION

#### 2.2.1. Basic Terms and Definitions

Some terms and definitions important for the understanding of the operation of the PDFD will now be introduced.

The concept of phase for a square wave will be defined at this point. The square wave waveform v(t) is related to the square wave phase  $\theta(t)$  as follows:

$$v(t) = \begin{cases} 1, & m \le \theta(t) < m + 1/2 \\ 0, & m + 1/2 \le \theta(t) < m + 1 \end{cases} \quad m \in Z$$

(2-2)

Where Z denotes the set of integers. As can be seen from (2-2),  $\theta(t)$  going from 0 to 1 delineates one cycle of the square wave. The time between rising edges of the square wave is  $\frac{1}{f}$  seconds, where f is considered the constant frequency of the square wave. f is related to the square wave phase  $\theta(t)$  as follows:

$$\theta(t) = ft + \theta_0 \tag{2-3}$$

Other frequencies besides  $f_s$  and  $f_r$  which will appear in text and equations throughout this chapter will now be described. The PDFD samples the signal square wave at regular intervals. The time between sample instants is  $\frac{1}{f_c}$  seconds, that is, the PDFD samples at a constant frequency  $f_c$ , referred to as the sampling rate of the PDFD.

The ultimate task of the PDFD is to measure the phase movements of the signal square wave with respect to the reference square wave of frequency  $f_r$ . However, to achieve this ultimate objective the PDFD utilizes an intermediate measurement which is the phase movements of the signal square wave with respect to another square wave of constant frequency  $f_{cmp}$ . The origin of and precise definition of this signal is described later in Section 2.3.

#### 2.2.2. PDFD Operation

The operation of a simple PDFD will now be qualitatively described to aid understanding of the mathematical description which follows.

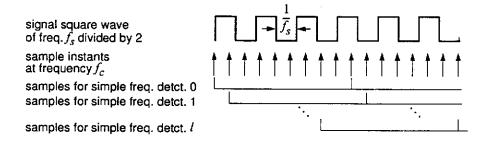

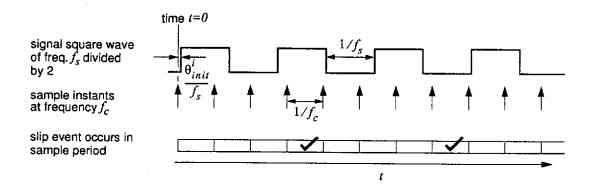

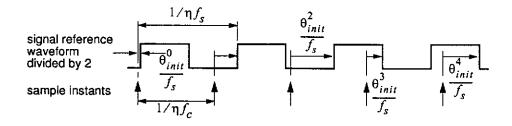

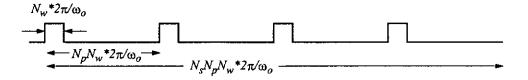

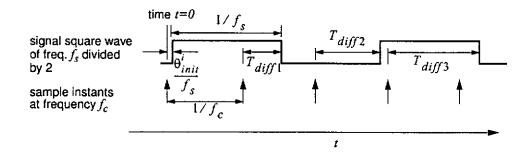

The signal square wave of frequency  $f_s$  is divided by two to produce a square wave of 50/50 mark space ratio and frequency  $\frac{f_s}{2}$ . This divided down square wave is then sampled at a rate of  $f_c$  samples per second. Figure 2-2 illustrates the sampling of the square wave.

Figure 2-2. Sampling of the signal and pairing the samples to create simple frequency detectors.

To simplify the explanation of the operation of the PDFD and also to simplify its subsequent analysis it is assumed that the signal square wave has a constant frequency  $f_s$ . The restriction of constant frequency  $f_s$  is later relaxed in Section 2.10.

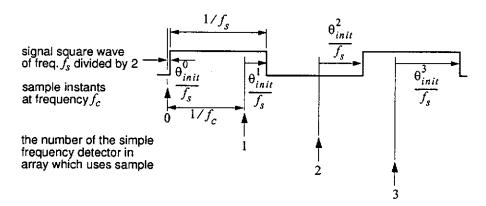

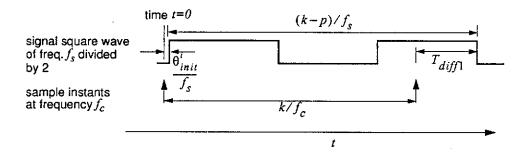

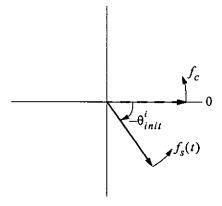

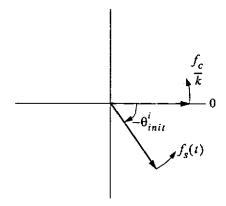

A first step in the processing is to divide the stream of binary samples into k lower sample rate streams. Each stream consists of samples spaced  $\frac{k}{f_c}$  seconds apart. Furthermore, l out of the possible k streams are used (see Figure 2-2). Consecutive samples in each stream (that is samples spaced  $\frac{k}{f_c}$  seconds apart) are processed by a mechanism referred to here as a 'simple frequency detector'. Figure 2-3 shows a section of Figure 2-2 in detail. As shown in Figure 2-3 each simple frequency detector has an initial starting phase, for the  $i^{th}$  simple frequency detector the starting phase is denoted by  $\theta^i_{init}$ , ( $i \in [0, 1, 2, ..., l-1]$ ).  $\theta^i_{init}$  is the phase relationship between the instant of the first sample in one of the k streams and the next edge of the signal square wave.  $\theta^i_{init}$  is a dimensionless quantity defined such that  $\theta^i_{init}/f_s$  is the actual time delay between the relevant epochs.

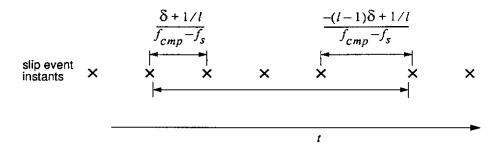

Each simple frequency detector indicates when the signal square wave phase moves a complete cycle with respect to a square wave of frequency  $f_{cmp}$ . More precisely, the simple frequency detector will indicate a phase movement corresponding to a complete cycle when  $(\theta_{init}^i + \theta_{slip})$  equals an integer, and where  $\theta_{slip}$  is the phase movement of the signal square wave with respect to a square wave of frequency  $f_{cmp}$ , that is,

$$\theta_{slip} = (f_{cmp} - f_s)t \tag{2-4}$$

The simple frequency detector is assumed to emit one when a phase movement corresponding to a full cycle is detected and a zero otherwise. The simple frequency detector produces this one output immediately after receiving its sample of the signal square wave. Recall that the simple frequency detector operates on samples spaced  $\frac{k}{f_c}$  seconds apart.

Figure 2-3. The sampling process creates diverse starting phases.

As shown in Figure 2-3, the  $\theta_{init}^i$  for each of the simple frequency detectors will be different, due to the different starting times of the simple frequency detectors. Out of the k possible simple frequency detectors the l used in the PDFD can be chosen (see Section 2.5) so that the  $\theta_{init}^i$  will be uniformly distributed across a signal square wave cycle.

The l simple frequency detectors are considered to form an array of l phased simple frequency detectors. In a period of  $\frac{k}{f_c}$  seconds each of the l simple frequency detectors will have an opportunity to report its decision on a phase movement of a complete cycle. Let the integers  $N_j$  represent the total number of complete cycle phase movements reported by all simple frequency detectors in the j<sup>th</sup> interval.  $N_j$  will have a value between 0 and l. The value of a particular  $N_j$  in the sequence represents the phase movement of the signal square wave with respect to a square wave of frequency  $f_{cmp}$  that occurred in the j<sup>th</sup> interval.

By accumulating the successive  $N_j$  generated by the PDFD, the phase movement of the signal square wave with respect to a square wave of frequency  $f_{cmp}$  can be found. This phase movement is quantized to 1/l <sup>th</sup> of the signal square wave cycle. Thus the PDFD acts as a phase movement quantizer. Dividing the phase movement measured by the PDFD by the time taken for the PDFD to measure the phase movement yields an estimate of relative frequency. Since the error in the phase measurement is bounded, the frequency measurement has no long term offset from the true value.

### 2.3. THE SIMPLE FREQUENCY DETECTOR

In this section we develop equations which describe the operation of a simple frequency detector. As noted previously, the square wave signal to be measured is divided down by two using a flip flop to ensure a good mark space ratio in the resulting square wave. The resulting square wave is sampled at rate  $f_c$  such that

$$f_s < f_c < 2f_s \tag{2-5}$$

As a first step, consider a simple frequency detector which uses every sample as illustrated in Figure 2-4. The simple frequency detector starting phase  $\theta^i_{init}$  (see Figure 2-4) is a dimensionless quantity defined such that  $\theta^i_{init}/f_s$  is the actual time delay between the relevant epochs. Thus  $\theta^i_{init}$  will take on a value in the range 0 to 1.

**Figure 2-4.** The sampling process. Simple frequency detectors are formed by comparing consecutive samples, or by comparing samples spaced *k* samples apart.

For the simple frequency detector which uses every sample,  $\theta_{slip}$  is given by

$$\theta_{slip} = (f_c - f_s)t \tag{2-6}$$

The key element of the simple frequency detector is a mechanism that identifies when two sampling instants of the sampling process fall within a single period of the signal square wave. As shown in Figure 2-4, this event can be identified by simply checking the last two successive samples to see if they have the same value. Identification of the event can logically be accomplished using the exclusive OR of successive samples followed by an inversion. A logical 1 is output to report when the event occurs. The event will be referred to as a 'slip event'. It is shown in Appendix A.2 that a slip event will be reported on the sampling instants following the time instants given by (2-7). Where  $Z^+$  denotes the positive integers.

$$t_m = \frac{m - \theta_{init}^i}{f_c - f_s}, \qquad m \in Z^+$$

(2-7)

The system comprised of the signal sampler and a mechanism for reporting slip events behaves as a simple frequency detector in the sense that the average frequency of slip event reports is given by

$$f_p = f_c - f_s \tag{2-8}$$

From inspection of (2-7) and (2-8) it can be seen that a slip event occurs when  $\theta_{init}^i + \theta_{slip}$  equals an integer. That is, a slip event indicates a phase movement of a complete cycle between the signal square wave of frequency  $f_s$  and a square wave of frequency  $f_c$ .

In the PDFD described in Section 2.2, the simple frequency detectors used only every  $k^{th}$  sample of the signal to be measured. Thus consider a system where only every  $k^{th}$  sample of the signal is used. For k odd, the slip event that is to be identified corresponds to an occurrence of two consecutive samples having the same value. Again, a pulse is output by the system to report when one of these slip events occurs.

#### Define p as

$$p \equiv \left\lfloor \frac{k(f_c - f_s)}{f_c} \right\rfloor,\tag{2-9}$$

where  $\lfloor x \rfloor$  denote the floor function, that is the greatest integer less than or equal to x [20]. It is shown in Appendix A.2 that if p is even then a slip event will be reported on the sampling instants following the time instants given by (2-10),

$$t_m = \frac{m - \theta_{init}^i}{f_{cmp} - f_s} \tag{2-10}$$

where

$$f_{cmp} \equiv f_c \left( 1 - \frac{p}{k} \right) \tag{2-11}$$

From (2-10) it can be seen again that a slip event occurs when  $\theta_{init}^i + \theta_{slip}$  equals an integer. Where  $\theta_{slip}$  is now given by (2-4). Note that no signal with frequency  $f_{cmp}$  actually exists.  $f_{cmp}$  is simply the frequency of a square wave relative to which the signal square wave  $f_s$  is effectively measured.

If p is odd, then a slip event will be reported on all sampling instants other than those sampling instants immediately following the instants defined by (2-10).

The simple frequency detector is linear in the range defined by (2-12), and has negative slope if p is even, and a positive slope if p is odd.

$$f_c \left(1 - \frac{p+1}{k}\right) < f_s < f_c \left(1 - \frac{p}{k}\right)$$

(2-12)

Up to now it has been assumed that k is odd. When k is even, an identical result is obtained. However, the slip event that is to be identified corresponds to occurrence of two consecutive samples with a different value, instead of the same value.

The simple frequency detector just described, in which every  $k^{th}$  sample is used, can be modified to ensure that the detector has only a negative slope. If p is odd the action of

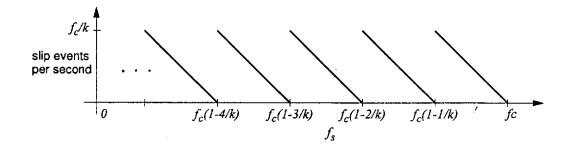

not reporting a slip event and reporting a slip event are swapped. In this way, the frequency detector characteristic always has a negative slope, as shown in Figure 2-5.

Figure 2-5. Modified frequency detector characteristics

# 2.4. THE PDFD, AN ARRAY OF SIMPLE FREQUENCY DETECTORS

In this section we derive equations relating the PDFD array output  $N_j$  to the phase movement  $\theta_{slip}$  (2-4). Furthermore, in this section we show that the PDFD acts as a quantizer of phase movement.

As described in Section 2.2, in the PDFD l streams are processed by an array of the simple frequency detectors. These l simple frequency detectors can be constructed to have staggered starting phases  $\theta_{init}^i$  as illustrated in Figure 2-3. Note that the l simple frequency detectors will have correspondingly staggered outputs. The start time of each simple frequency detector in the array will be separated by at least  $\frac{1}{f_c}$  seconds.

Each of the simple frequency detectors reports whether or not it has detected a slip event every k clock periods, this period of  $\frac{k}{f_c}$  seconds is referred to as the "reporting period" of the PDFD.

The starting phases  $\theta_{init}^i$  of the l simple frequency detectors, will be distributed in some manner in the interval [0,1). By a judicious choice of l, k,  $f_s$ ,  $f_c$  and the actual l streams utilized, the distribution of the  $\theta_{init}^i$  can be made close enough to uniform for practical purposes. With uniformly distributed  $\theta_{init}^i$ , the slip event instant for each of the l frequency detectors, given by (2-10), will be uniformly distributed in time.

As described in Section 2.2, a sequence of integers  $N_j$  is generated as follows: Once every  $\frac{k}{f_c}$  seconds, the decisions on phase movements corresponding to a complete

cycle (or slip events) output by the l simple frequency detectors are added up to form  $N_j$ . In each reporting period, the average number of the l frequency detectors that will report a slip event can be found from (2-10). This average value of  $N_j$  which is denoted by  $N_{ave}$ , is given by:

$$N_{ave} = \frac{lk}{f_c} (f_{cmp} - f_s) = l \left( k - p - \frac{kf_s}{f_c} \right)$$

(2-13)

Since the l starting phases  $\theta_{init}^i$  are assumed to be uniformly distributed in the interval [0,1), their values will be in the set given by (2-14)

$$[\phi_0, \phi_0 + \frac{1}{l}, \phi_0 + \frac{2}{l}, ..., \phi_0 + \frac{l-1}{l}]$$

(2-14)

where  $\phi_0$  is the smallest of the  $\theta_{init}^i$ .

Consider now the addition of all the  $N_j$  generated since the initialization of the PDFD up to the end of the  $n^{\text{th}}$  reporting period and multiplying this sum by  $\frac{1}{l}$ . This sum, denoted by  $\theta_{out}$ , is given by (2-15)

$$\theta_{out} = \frac{1}{l} \sum_{i=0}^{l-1} \left[ \theta_{slip} + \theta_{init}^{i} \right]$$

(2-15)

where

$$\theta_{slip} = \frac{nk}{f_c} (f_{cmp} - f_s), \qquad n \in Z^+$$

(2-16)

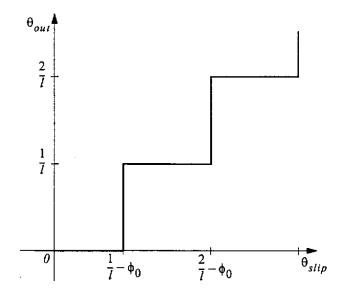

It can be shown (Appendix A.3) that for  $\theta_{init}^{i}$  given by (2-14),  $\theta_{out}$  can be expressed as

$$\theta_{out} = \frac{\lfloor l(\theta_{slip} + \phi_0) \rfloor}{l}$$

(2-17)

From (2-17) it can be seen that the PDFD acts a quantizer of phase movement. As illustrated in Figure 2-6, the quantization level is 1/l <sup>th</sup> of a signal square wave cycle,

and there is an offset of  $-\phi_0$ . The relationship between  $\theta_{out}$  and  $\theta_{slip}$  given in (2-15) is referred to here as the PDFD characteristic.

**Figure 2-6.** PDFD Characteristic for uniformly distributed starting phases. The PDFD acts as a quantizer of phase movement.

In many applications, the phase movement of the signal square wave with respect to a reference square wave of the nominal frequency  $f_r$  (Figure 2-1) will be required. The phase movement of the signal square wave with respect to a reference square wave of frequency  $f_r$  is obtained as follows: The average number of frequency detectors which report a slip each reporting period  $N_{ave}$ , (2-13) is found for  $f_s = f_r$ . This specific value of  $N_{ave}$  is denoted  $N_{nom}$ .  $N_{nom}$  is then subtracted from the actual PDFD output  $(N_j)$  each reporting period, to obtain the phase movements with respect to a reference square wave of frequency  $f_r$

Alternatively, two arrays of simple frequency detectors can be used, one measuring the phase movement of the signal square wave with frequency  $f_s$  with respect to  $f_{cmp}$ . The other measuring phase movement of the reference square wave with frequency  $f_r$  with

respect to  $f_{cmp}$ . The phase movement of the signal square wave with respect to the reference square wave can be obtained by subtracting the  $f_r$  measurement from the  $f_s$  measurement.

#### 2.5. OPERATING LIMITS

In this section we determine the range of values of the signal square wave frequency  $f_s$  for which the PDFD correctly reports phase movements. A key factor to be considered is the distribution of the starting phases  $\theta_{init}^i$ . Therefore we initially show how k, l and  $f_c$  can be chosen to obtain the  $\theta_{init}^i$  evenly distributed (Figure 2-3) for the case when the frequency of the signal square wave is exactly  $f_c$  that is when  $f_s = f_c$

The specific, but important case, where the l simple frequency detectors use l successive samples of the signal waveform is considered. The  $\theta_{init}^i$  values generated by this process are illustrated in Figure 2-3. The value  $\theta_{init}^i$  for the i<sup>th</sup> frequency detector can be determined given the value  $\theta_{init}^j$  for one other frequency detector, say j=0, and the frequencies  $f_r$  and  $f_c$  (see Figure 2-3):

$$\theta_{init}^{i} = 1 + \theta_{init}^{0} - \frac{f_{r}^{i}}{f_{c}} + \left\lfloor \frac{f_{r}^{i}}{f_{c}} - \theta_{init}^{0} \right\rfloor, \qquad i \in [0, 1, 2, ..., l-1]$$

(2-18)

For a given  $f_r$  and l, the  $\theta_{init}^i$  will be evenly distributed (Figure 2-3) if  $f_c$  satisfies

$$f_c = \left(\frac{l}{l-p}\right) f_r \tag{2-19}$$

and l and (l-p) have no common factors.

k is chosen so that the individual frequency detectors are maintained in their linear region (2-12) for the expected values of  $f_s$ .

Note that it will not be possible to use successive samples of the signal square wave in applications were the sampling rate  $f_c$  is not freely chosen. In these cases, which samples are observed to obtain even starting phases will be specific to  $f_r$  and  $f_c$ .

However, many of the results obtained here are applicable to this more complex situation.

Although l, k, and  $f_c$  may be chosen to obtain uniformly distributed starting phases when the signal square wave frequency is exactly the nominal frequency  $f_r$ , this will in general not result in perfectly uniformly distributed starting phases for sampling the signal square since its frequency  $f_s$  is not known. However, it is shown in Appendix A.3 that for  $f_s$  close to the nominal frequency  $f_r$ , the  $\theta^i_{init}$  generated by sampling the signal square wave will not be significantly perturbed from those generated by sampling a square wave of frequency  $f_r$  Below we quantify how close  $f_s$  needs to be to the nominal frequency  $f_r$

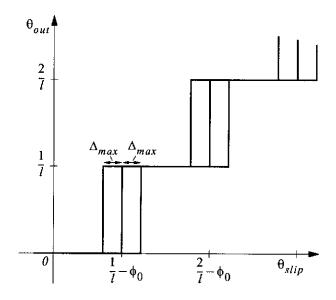

It is shown in Appendix A.3 that for  $f_s$  close to  $f_r$  the PDFD characteristic (2-15) is bounded by two quantizer functions (2-20), that is,

$$\frac{\left\lfloor l(\theta_{slip} + \phi_0 - \left| \Delta_{max} \right|) \right\rfloor}{l} \le \theta_{out} \le \frac{\left\lfloor l(\theta_{slip} + \phi_0 + \left| \Delta_{max} \right|) \right\rfloor}{l} \tag{2-20}$$

The two bounding quantizer functions are shown in Figure 2-7. The  $\Delta_{max}$  in (2-20) is the maximum perturbation of the starting phases from their nominal uniform distribution.

**Figure 2-7.** PDFD Characteristic for non-uniformly distributed starting phases as will occur in practice.

The PDFD Characteristic is bounded by two quantizer functions.

Based on (2-20), it is shown in Appendix A.3 that the operating range for  $f_s$  is given by (2-21)

$$f_{smin} \le f_s \le f_{smax} \tag{2-21}$$

Where

$$f_{smin} = f_r \left( 1 - \frac{\gamma}{(l-p)(l-1)} \right)$$

(2-22)

$$f_{smax} = f_r \left( 1 + \frac{\gamma}{(l-p)(l-1)} \right)$$

(2-23)

$$\left|\Delta_{max}\right| = \frac{\gamma}{l} \tag{2-24}$$

$\gamma$  is chosen to be less than one, so that  $\Delta_{max}$  is some fraction of  $\frac{1}{l}$  (2-24) which is the PDFD quantization interval.

Clearly it is desirable to have the distance between the two bounding quantizers (2  $\Delta_{max}$ ) as small as possible (Figure 2-7). However, the results of this section and Appendix A.3 demonstrate that when the PDFD is required to measure phase movements much less than one cycle (i.e. large l), and the sampling rate  $f_c$  is not high, the operating range of  $f_s$  (2-21) is narrow. For example, for a PDFD with l equal to one hundred, and a sampling rate approximately equal to the signal frequency (p equal to one, q equal to 0.5),  $f_s$  must be within  $\pm 51$  parts per million (ppm) of  $f_r$  (2-22), (2-23), (2-21). Nevertheless, in many systems the signals will be in a narrow range of frequencies as they are of low data rate and modulated onto a high carrier frequency [21]. Or the signals may not contain data themselves, but rather timing information to facilitate the synchronization of transmitting and receiving components in a communication system.

To increase the range of  $f_s$  the following methods can be employed: The sampling rate  $f_c$  can be increased (p greater than one) to increase the operating range. Choosing a smaller l dramatically increases the operating range as  $f_{smax}-f_{smin}$  (2-21) is approximately proportional to  $1/l^2$ .

The different starting phases  $\theta_{init}^i$  may be obtained in a 'parallel' fashion. The different  $\theta_{init}^i$  is obtained by delaying the signal by different amounts before it is sampled. The delayed versions of the signal are sampled simultaneously. This 'parallel' method is in contrast to the 'serial' like method used up to this point, where the different  $\theta_{init}^i$  arises from the sampling process itself (see Figure 2-3). It can be shown that the obtaining of many samples in parallel increases the operating range of  $f_s$  (2-21). However, the hardware complexity is increased when using parallel methods. Furthermore, the accuracy with which the delay elements can be made may limit the smallest phase movement that can be measured.

Finally, a combination of the 'serial' and 'parallel' methods described above is possible with parallel groups of serial simple frequency detectors. In this situation hardware complexity can be traded off against the operating range of  $f_s$ .

#### 2.6. GENERALIZED SAMPLING RATE

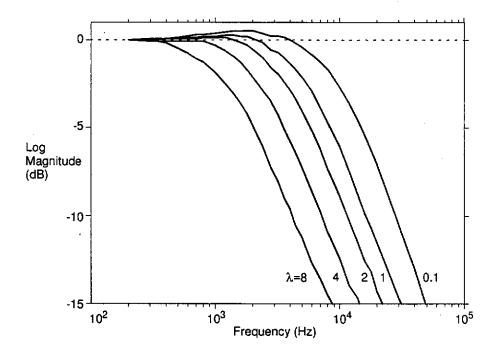

In Section 2.3 the sampling rate of the PDFD,  $f_c$ , was required to be in the restricted range given by (2-5). However, in this section the simple frequency detector is generalized so that PDFD sampling rate can be outside the restricted range of (2-5).

Consider that the signal square wave is now sampled at the rate  $\eta f_c$ , where  $f_c$  is in the range given by (2-5), and  $\eta$  is in the set

$$\eta \in \left(..., \frac{1}{3}, \frac{1}{2}, 1, 2, 3, ...\right)$$

(2-25)

Firstly consider the cases where  $\eta$  is an integer. If only every  $\eta^{th}$  sample is used. Then the generalized simple frequency detector is equivalent to the simple frequency detector described in Section 2.3 that uses every sample at rate  $f_c$ .

Consider now the cases where  $\eta$  is a fraction. If only every  $\eta k^{th}$  sample is used. Then the generalized simple frequency detector is equivalent to the simple frequency detector described in Section 2.3 that uses every  $k^{th}$  sample of a sampler running at rate  $f_c$ .

#### 2.7. OPERATING LIMITS FOR GENERALIZED FREQUENCY DETECTORS

In this section the range of values of the signal square frequency  $f_s$  for which a PDFD employing generalized simple frequency detectors (Section 2.6) correctly reports phase movements, is found.

Note that the generalized simple frequency detector described in Section 2.6 uses only one in  $\eta k$  samples. Thus, using a single sampler running at rate  $\eta f_c$  an array of l simple frequency detectors can be constructed for

$$1 \le l \le \eta k \tag{2-26}$$

Note that slip events for the PDFD using the generalized simple frequency detector are reported every  $\eta k$  clock periods which have period  $\frac{1}{\eta f_c}$  seconds. Hence the PDFD has the reporting period of  $\frac{k}{f_c}$  seconds.

As in Section 2.5, we initially show how  $\eta$ , k, l and  $f_c$  can be chosen to obtain the  $\theta_{init}^i$  evenly distributed for the case when the frequency of the signal square wave is exactly  $f_r$ , that is when  $f_s = f_r$ . Note that initially only  $\eta$  less than or equal to one is considered.

Again, the specific but important case, where the l simple frequency detectors use l successive samples of the signal waveform is considered. The  $\theta_{init}^i$  values generated by this process are illustrated in Figure 2-8. The value  $\theta_{init}^i$  for the i<sup>th</sup> frequency detector can be determined given the value  $\theta_{init}^j$  for one other frequency detector, say j=0, and the frequencies  $f_r$  and  $f_c$  (see Figure 2-8):

$$\theta_{init}^{i} = 1 + \theta_{init}^{0} - \frac{f_r}{\eta f_c} i + \left| \frac{f_r}{\eta f_c} i - \theta_{init}^{0} \right|, \qquad i \in [0, 1, 2, ..., l-1]$$

(2-27)

For a given  $f_r$  and l, the  $\theta_{init}^l$  will be evenly distributed across 0,1 if  $f_c$  satisfies

$$f_c = \frac{l}{l - p\eta} f_r \tag{2-28}$$

and l and  $(l-p\eta)$  have no common factors.

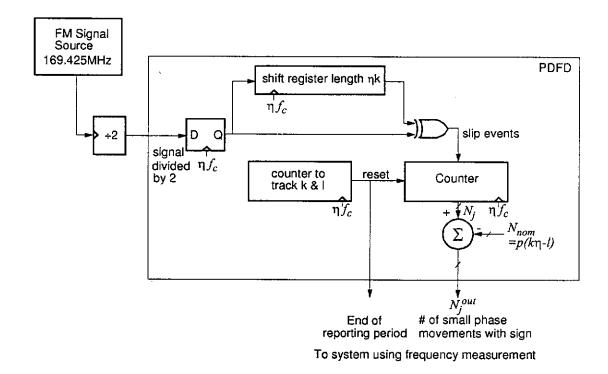

Furthermore, the value of  $N_{ave}$  when the signal frequency  $f_s$  is equal to  $f_r$ ,  $N_{nom}$  will be

$$N_{nom} = p(k\eta - l) \tag{2-29}$$

k is chosen so that the individual frequency detectors are maintained in their linear region (2-12) for the expected values of  $f_s$ .

The operation of the PDFD using the generalized simple frequency detectors is similar to PDFD operation described in Section 2.4 and Section 2.5. Again the PDFD characteristic (2-15) when  $f_s$  is close to  $f_r$  can be shown to be bounded by two quantizer functions (2-20). Where again  $\Delta_{max}$  in (2-20) is the maximum perturbation of the starting phases from their nominal uniform distribution.

As in Section 2.5 with  $\Delta_{max}$  set to some fraction  $\gamma$  of  $\frac{1}{l}$  (2-24) limits  $f_{smin}$ ,  $f_{smax}$  for  $f_s$  (2-22) can be found

$$f_{smin} = f_r \left( 1 - \frac{\gamma \eta}{(l - p\eta)(l - 1)} \right) \tag{2-30}$$

$$f_{smax} = f_r \left( 1 + \frac{\gamma \eta}{(l - p\eta)(l - 1)} \right)$$

(2-31)

**Figure 2-8.** Frequency detector start phases for generalized sampling rate. In this section the sampling frequency is chosen so that using successive samples yields evenly distributed starting phases. Using successive samples simplifies the analysis and yields simplified hardware.

The limits  $f_{smin}$ ,  $f_{smax}$  can be found for more general situations when  $\eta$  is greater than one or when successive samples are not used. Suppose the time between the sample instant for the first simple frequency detector (0<sup>th</sup>) and the sample instant for the last (l-1<sup>th</sup>) simple frequency detector is  $T_{max}$ .  $T_{max}$  can be expressed as a fraction  $\chi$  of  $\frac{1}{f_r}$

$$T_{max} = \frac{\chi}{f_r} \tag{2-32}$$

Then  $\Delta_{max}$  can be found to be

$$\Delta_{max} = \chi \left( 1 - \frac{f_s}{f_r} \right) \tag{2-33}$$

and with  $\Delta_{max}$  set to some fraction  $\gamma$  of  $\frac{1}{l}$  (2-24) limits  $f_{smin}$ ,  $f_{smax}$  are found

$$f_{smin} = f_r \left( 1 - \frac{\gamma}{\chi l} \right) \tag{2-34}$$

$$f_{smax} = f_r \left( 1 + \frac{\gamma}{\chi l} \right) \tag{2-35}$$

From (2-34), (2-35) a useful bound can be found on the minimum sampling rate required to achieve  $\Delta_{max} < \frac{1}{2I}$ :

$$\eta f_c > l^2 (f_{smax} - f_{smin}) \tag{2-36}$$

#### 2.8. INSTANTANEOUS ERROR

Thus far we have considered the error between the accumulated reported phase movements,  $\theta_{out}$  (2-15), and the actual phase movement since the PDFD start  $\theta_{slip}$ .

However, the PDFD may also incorrectly report the phase movement between the square waves of frequency  $f_s$  and  $f_{cmp}$  that has occurred in the last reporting period as follows: With  $f_s$  not equal to  $f_r$  the array of frequency detectors should report a phase movement of  $\lfloor N_{ave} \rfloor$  or  $\lfloor N_{ave} \rfloor + 1$  1/l th cycles between  $f_s$  and  $f_{cmp}$ . However for a particular detector the  $\theta_{init}$  may be sufficiently perturbed from its nominal value such that  $\lfloor N_{ave} \rfloor - 1$  or  $\lfloor N_{ave} \rfloor + 2$  is reported. Hence the instantaneous phase movement measurement is in error by more than 1/l th of a cycle. The limits between which  $f_s$  may range before this instantaneous measurement error occurs will now be given.

Case p=1,  $\eta \le 1$ . Consider the case of  $f_s$  slightly greater than  $f_r$ , and p equal to one. A frequency  $f_{smax1}$  (2-37) can be found (Appendix A.4), such that: For  $f_s$  greater than  $f_{smax1} \lfloor N_{ave} \rfloor$ -1 may be reported and for  $f_s$  less than  $f_{smax1} \lfloor N_{ave} \rfloor$ -1 will never be reported.  $\lfloor N_{ave} \rfloor$ -1 is the first error to occur for  $f_s$  greater than  $f_r$

$$f_{smax1} = f_r \left( 1 + \frac{\eta}{(l - \eta)(2l + 1)} \right)$$

(2-37)

For the case of  $f_s$  slightly less than  $f_r$  and p equal to one a frequency  $f_{smin1}$  (2-38) can be found (Appendix A.4), such that: For  $f_s$  less than  $f_{smin1} \lfloor N_{ave} \rfloor + 2$  may be reported and for  $f_s$  greater than  $f_{smin1} \lfloor N_{ave} \rfloor + 2$  will never be reported.  $\lfloor N_{ave} \rfloor + 2$  is the first error to occur for  $f_s$  less than  $f_r$

$$f_{smin1} = f_r \left( 1 - \frac{\eta}{(l - \eta)(2l - 1)} \right)$$

(2-38)

Case p>1,  $\eta \le 1$ . Now considering the cases were p is greater than one. To make the problem more tractable only the cases were l is chosen as follows are considered.

$$l = pr + 1 \qquad r \in \mathbb{Z}, r \ge 2 \tag{2-39}$$

As for the p equal to one cases, the frequencies  $f_{smaxp}$ ,  $f_{sminp}$  can be found (Appendix A.4), such that when  $f_s$  is greater than  $f_{sminp}$  and less than  $f_{smaxp}$  the  $\lfloor N_{ave} \rfloor$ -1 and  $\lfloor N_{ave} \rfloor$ +2 errors discussed above do not occur.

$$f_{smaxp} = f_r \left( 1 + \frac{\eta p}{(l - p\eta)(l(2p - 1) + 1)} \right)$$

(2-40)

$$f_{sminp} = f_r \left( 1 - \frac{\eta p}{(l - p\eta)(l(p+1) - 1)} \right)$$

(2-41)

#### 2.9. SPECTRAL CHARACTERISTICS

Denote the difference between the accumulated PDFD output  $\theta_{out}$  (2-15) and  $\theta_{slip}$  at the end of the  $n^{th}$  reporting period by the sequence  $\phi_n$ , that is

$$\phi_n = \theta_{slip} - \theta_{out} \tag{2-42}$$

In this section the spectral characteristics of the sequence  $\phi_n$  are derived. For certain applications of the PDFD, it may be necessary to low pass filter the output of the PDFD. For example filtering may be used to reduce the high frequency variation or jitter of  $\phi_n$ . So the spectrum of  $\phi_n$  will be required to ascertain the effects of filtering. The spectral characteristics of  $\phi_n$  are similar to the spectral characteristics of waiting time jitter described in [22], [23].

Define the sequences  $v_n^i$  as follows

$$v_n^i = \xi_n + \theta_{init}^i - \left| \xi_n + \theta_{init}^i \right| \tag{2-43}$$

$$\xi = \frac{k}{f_c} (f_{cmp} - f_s) \tag{2-44}$$

$\phi_n$  (2-42) can be given as a linear combination of the  $v_n^i$  and a constant

$$\phi_n = \frac{1}{l} \left( \sum_{i=0}^{l-1} \upsilon_n^i - \sum_{i=0}^{l-1} \theta_{init}^i \right)$$

(2-45)

The periodic function v(t) (2-46) has the Fourier series representation (2-47)

$$\upsilon(t) = \xi t - \lfloor \xi t \rfloor \tag{2-46}$$

$$v(t) = \sum_{w = -\infty}^{\infty} F_w e^{j2\pi w \xi t} \qquad F_w = \begin{cases} \frac{1}{2} & w = 0\\ \frac{-1}{j2\pi w} & w \neq 0 \end{cases}$$

(2-47)

The periodic functions  $v^i(t)$  (2-48) are time shifted versions of v(t) and hence have the same Fourier series representation as v(t) but with coefficients  $F_w^i$ .

$$\upsilon^{i}(t) = \xi t + \theta^{i}_{init} - \left| \xi t + \theta^{i}_{init} \right| \tag{2-48}$$

$$F_w^i = F_w e^{j2\pi w \theta_{init}^i} \tag{2-49}$$

When the  $v^{i}(t)$  are sampled at the equispaced times (2-50) the sequences  $v_{n}^{i}$  are obtained.

A periodic function  $\phi(t)$  can be constructed from the functions  $v^i(t)$ , which when sampled at the equispaced times (2-50) the sequence  $\phi_n$  is obtained.

$$t = 1, 2, 3... (2-50)$$

From (2-45), (2-47), and (2-49) the Fourier series representation of  $\phi(t)$  is the same as v(t) but with coefficients  $F_w^T$ .

$$F_{w}^{T} = \begin{cases} \frac{1}{2} - \frac{1}{l} \sum_{i=0}^{l-1} \theta_{init}^{i} & w = 0 \\ i = 0 & \\ I - 1 & \\ F_{w} \frac{1}{l} \sum_{i=0}^{l-1} e^{j2\pi w \theta_{init}^{i}} & w \neq 0 \end{cases}$$

(2-51)

The Fourier transform of  $\phi(t)$  is found to be

$$\Phi(j2\pi f) = 2\pi \sum_{w=-\infty}^{\infty} F_w^T \delta(f - \xi w)$$

(2-52)

Furthermore, the Fourier transform of the sampled  $\phi(t)$ ,  $\phi_n$  is found to be

$$\Phi_s(j2\pi f) = 2\pi \sum_{w=-\infty}^{\infty} F_w^T \sum_{m=-\infty}^{\infty} \delta(f - \xi w - m)$$

(2-53)

Confining ourselves to the frequency interval [0,1), the spectrum of the  $\phi_n$  sequence can be written as

$$\Phi_{s}(j2\pi f) = 2\pi \sum_{w=-\infty}^{\infty} F_{w}^{T} \delta(f - (\xi w - \lfloor \xi w \rfloor))$$

(2-54)

The frequency interval [0,1) physically corresponds to the frequency interval [0,  $\frac{f_c}{k}$ ) as the physical reporting rate of the PDFD is  $\frac{f_c}{k}$ .

Thus the spectrum of  $\phi_n$  consists of a number of spectral lines (infinitely many if  $\xi$  irrational) who amplitudes are given by the  $F_w^T$ .

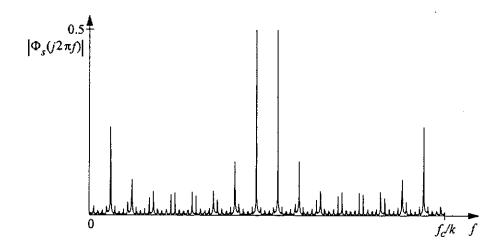

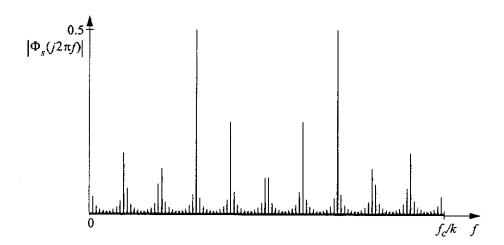

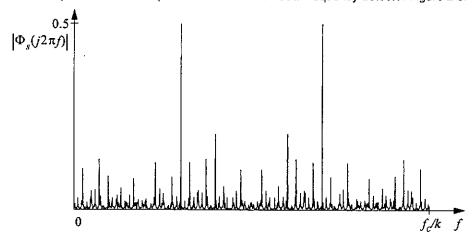

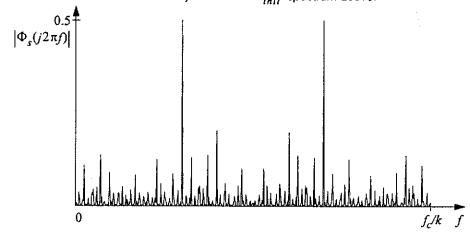

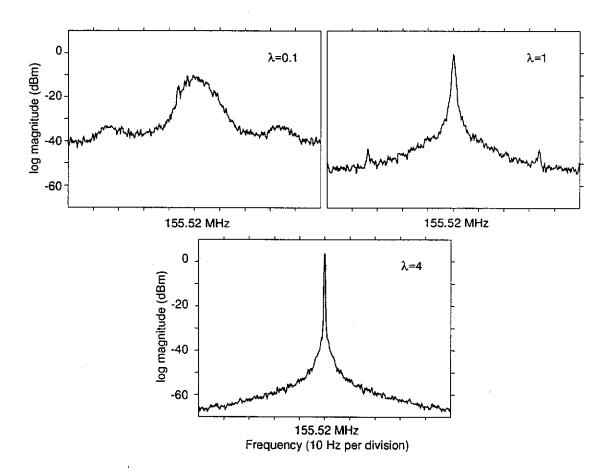

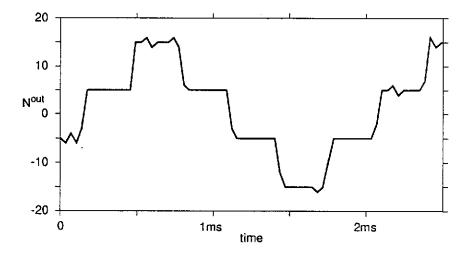

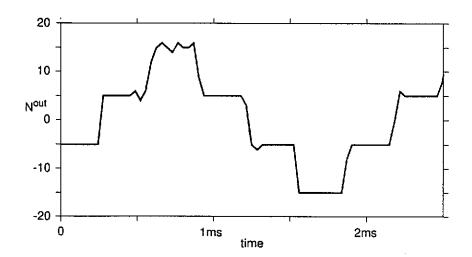

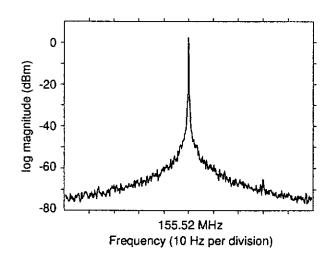

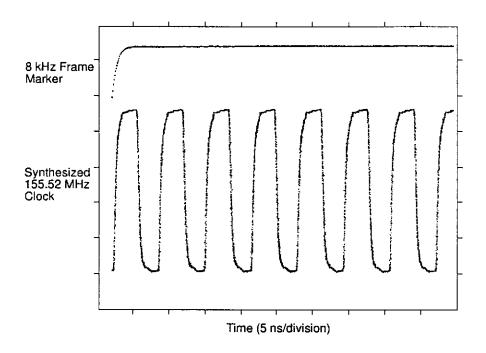

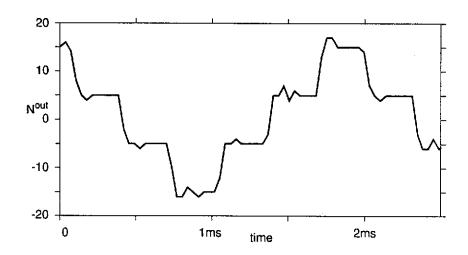

To verify the prediction of the spectral characteristics of  $\phi_n$ , a  $\phi_n$  sequence of length one thousand was generated for a PDFD with l=10 and  $\xi=0.5301$ . A discrete Fourier transform was performed on the sequence. The resulting spectrum is shown in Figure 2-11. Also shown in Figure 2-9 and Figure 2-10 are spectrum for the  $\upsilon_n^i$  sequence and the  $\phi_n$  sequence if the  $\theta_{init}^i$  were uniformly distributed.

The spectrum for  $\phi_n$  was also generated using (2-54) for one thousand terms. The result is shown in Figure 2-12 and as can be seen, is in good agreement with the spectrum obtained from the sequence. In Figure 2-9 to Figure 2-12 the spectral line at f=0 has been removed, and the scales in the figures are linear. Furthermore the figures are intended only to show similarities or differences in the shape of the spectrum and not provide detailed results for the specific example.

Figure 2-9. Spectrum for sequence  $v_n^i$

Figure 2-10. Spectrum for sequence  $\phi_n$  with uniformly distributed  $\theta_{init}^i$ . Note the difference between this spectrum and the spectrum for each individual frequency detector Figure 2-9.

Figure 2-11. Spectrum for sequence  $\phi_n$ . Note how this spectrum contains the dominate features of the uniformly distributed  $\theta^i_{init}$  spectrum above.

**Figure 2-12.** Predicted Spectrum for sequence  $\phi_n$ . Agrees well with the actual spectrum Figure 2-11.

## 2.10. PDFD OPERATION FOR TIME VARYING FREQUENCY

Thus far it has been assumed that the signal square wave frequency  $f_s$  is constant. Assuming  $f_s$  was constant permitted a succinct derivation of the PDFD properties. Furthermore some of the more specific properties such as spectral characteristics and instantaneous error can likely only be derived with the assumption of constant  $f_s$ .

However in many applications the signal square wave frequency  $f_s$  is a function of time  $f_s(t)$ . It is shown in Appendix A.5 that if the function  $f_s(t)$  is bounded as follows

$$f_{smin} \le f_s(t) \le f_{smax} \tag{2-55}$$

with  $f_{smin}$  and  $f_{smax}$  as given by (2-22)(2-23), (2-30)(2-31), or (2-34)(2-35). Then the PDFD characteristic (2-15) relating  $\theta_{out}$  to  $\theta_{slip}$  will be bounded by the two quantizer functions given in (2-20).

#### 2.11. SUMMARY

A new method has been presented to measure small frequency differences between two square waves. The method called the PDFD involves the use of a large number of simple frequency detectors each with different start phases. Importantly, arbitrarily small phase movements between the signal and reference square waves can be detected, even when the PDFD is clocked at a low rate. The PDFD is totally digital and has no frequency offsets. For many applications it will permit the removal of analog subsystems, or high speed analog to digital converters used for frequency detection.

The operating limits of the PDFD were derived. It was found that the allowable deviation from the nominal frequency of the signal being measured was approximately proportional to  $1/l^2$ . That is, approximately proportional to the square of the smallest measurable phase change.

The PDFD offers significant advantages for applications wherever small frequency differences have to be measured. For example in the demodulation or modulation of angle modulated signals, measurement and reconstruction of frequency in baseband digital transmission systems, and frequency synthesis.

# A Frequency Steered Phase Locked Loop

#### 3.1. INTRODUCTION

Phase locked loops (PLL) are one of the most frequently used communications circuits. PLLs have been used for filtering, frequency synthesis, frequency and phase modulation, demodulation, signal detection and a variety of other applications. The PLL commonly has a number of defects when constructed from typical components. Some of the defects of the PLL that are relevant to this chapter include:

- Rapid, reliable locking to the desired signal of narrow bandwidth PLLs. Particularly when there is significant frequency difference between the PLL's voltage controlled oscillator (VCO) and the input signal. This problem is especially serious when the VCO has a poorly specified centre frequency and can operate over a wide frequency range. Additionally, the PLL may false lock to a sideband of the input signal. Or even to an unwanted signal if the signal is buried in noise and other signals.

- The effects of VCO phase noise can cause significant errors in the tracking of the input signal. This problem is especially serious when a very narrow bandwidth PLL is required and/or low quality VCOs are employed.

**Previous Work - Acquisition.** Much work has been done in developing techniques to aid acquisition and prevent false lock in PLLs. Some of the techniques employed to aid acquisition include:

Sweeping of the VCO [6].

- Switching of loop filter in tracking and acquisition modes [24].

- Injection of the input signal into the VCO [25].

- Addition of a non-linearity in the loop filter [26].

- Use of combined phase and frequency detectors, either as separate devices [27] or as a single device with both phase and frequency discrimination characteristics [28], [29], [30].

- Use of multiple phase detectors [31].

- Accurate initial VCO frequency and limited tuning range by use of a voltage controlled crystal oscillator.

In many applications it is difficult to apply the above techniques due to one or more of the following reasons: Input signal deeply buried in noise and other signals. Missing signal transitions for example in clock recovery. High cost, and low level of integration.

In the field of clock recovery for baseband digital data transmission, a number of techniques have been reported to obtain accurate initial VCO tuning to aid acquisition, without having to resort to expensive voltage controlled crystal oscillators. These techniques include:

- The use of high speed digital PLLs using novel methods to generate the very high speed clocks and to process the phase information [32].

- A Master/Slave dual loop architecture employing highly matched VCOs

[33].

- Switching the VCO between a crystal controlled "training" loop and the input signal at start-up and when false locking is detected [34], [35].

All the above techniques employ a fixed frequency crystal oscillator to either obtain a very high speed clock for use in a digital PLL. Or to influence the tuning of the VCO. These techniques may suffice for clock recovery, but for more demanding applications

where the signal is deeply buried in noise they may not be adequate. Furthermore, detailed mathematical models of their operation have not been developed.

**Previous Work - Phase Noise.** The problem of VCO phase noise in PLLs has not received much attention. The compromise between increasing the PLL bandwidth to reduce the effects of VCO phase noise, and reducing the PLL bandwidth to obtain the required filtering of the signal has been studied [36]. For the application of frequency synthesis a type of frequency feedback employing delay line frequency discriminators [18] has been used to reduce VCO phase noise. However only VCO phase noise outside the main PLL bandwidth [37]. But, no general solutions to the problem of VCO phase noise appear to have been proposed.

Hence very narrow bandwidth PLLs can be difficult and costly to realise as they require very low phase noise VCOs. Certainly, VCOs with poor phase noise (such as integrated circuit relaxation oscillators) can not be used in narrow bandwidth applications.

In many communications systems the frequencies at which data is transmitted are specified with tight tolerances. Typically, in the order of several or several tens of parts per million (ppm) [38], [39]. Some communication systems have even tighter tolerances [21]. In the application of clock recovery, the bandwidth of the PLL used would typically be in the order of a thousand ppm of the transmission frequency [38].

The Steered Frequency Phase Locked Loop. A new phase tracking system is presented, the Steered Frequency Phase Locked Loop (SFPLL) (patent pending). The SFPLL presented in this chapter is a system that will phase lock to an input signal as in a conventional PLL. But the SFPLL overcomes many of the problems associated with PLLs. The SFPLL technique allows the PLL used in the receiver component of the communication system to be centred at the appropriate frequency, with the same accuracy and stability associated with the transmission component. Exploiting the fact that the transmission frequency is often very accurately specified, the PLL can be centred very close and within the PLL bandwidth, to the transmission frequency. This close initial tuning of the PLL avoids sideband lock and achieves fast frequency acquisition.

Like conventional PLLs the SFPLL takes an input signal which it is required to phase lock to. In addition to this input signal, the SFPLL has an accurate reference frequency input of frequency  $\omega_r$ . The reference frequency  $\omega_r$  is chosen to be close to (though not necessarily the same as) the frequency of the input signal which the SFPLL is required to phase lock to. The SFPLL does not require any monitoring nor any switching of the frequency reference signal which is always acting.

The key advantages of the SFPLL are:

- the output frequency is  $\omega_r$  (or is close to  $\omega_r$ ) when no input signal is present.

- The range of frequencies to which the SFPLL can lock can be confined to a small and controllable region around  $\omega_r$

- For a particular class of SFPLLs, the effects of VCO phase noise can be reduced to an insignificant amount. And the SFPLL bandwidth made less dependent on component parameters.

- The SFPLL can be realized in simple digital integrated circuit technology.

Allowing low cost miniaturized realizations, and also extremely precise and controllable positioning of the frequency the SFPLL is centred on.

# 3.1.1. Outline of Chapter 3

This chapter is organised as follows:

In Section 3.2 the structure of the SFPLL is described and a small signal linear model for the SFPLL is analyzed. Some general properties of SFPLLs are obtained, and some extensions to the basic SFPLL are mentioned.

In Section 3.3 further properties of an important class of SFPLL are obtained. In particular, the performance of the SFPLL when the input signal is corrupted with additive white Gaussian noise. It is shown that the SFPLL has a mathematical model which is equivalent to certain types of PLLs. This model equivalence allows the non-linear noise theory developed for PLLs to be applied to SFPLLs.

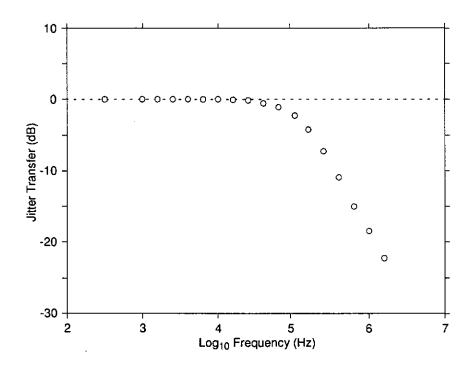

In Section 3.4 the frequency and step response characteristics of an important type of SFPLL are investigated. It is shown that undesirable peaking and overshoot in the frequency and step responses can be eliminated.

The effects of VCO phase noise in the SFPLL are then studied in Section 3.5. It is shown that in theory the SFPLL can reduce the effects of VCO phase noise to an insignificant amount.

In Section 3.6 simulations are performed to verify that the SFPLL and PLL models are equivalent. Furthermore, that the SFPLL performance with the input signal corrupted by noise is predicted well using established techniques.

A digital implementation of the SFPLL is outlined in Section 3.7. Then in Section 3.8 experimental results from a prototype of the SFPLL implementation are presented.

Finally Section 3.9 summarizes the chapter.

Note that some details relating to the non-linear behaviour of the SFPLL in noise, are given in Appendix B.

## 3.1.2. Contributions of Chapter 3

The introduction of the third signal source  $\omega_n$  independent from the input signal and the VCO signal, into a phase locking system has not been dealt with in the literature. The use of frequency feedback in PLLs using delay line discriminators has been considered in [37]. It was used to reduce VCO phase noise outside the main PLL bandwidth and noise generated by digital phase detectors, for frequency synthesis applications. In contrast, in the SFPLL frequency feedback is not employed merely as an addition to alleviate some problems, but instead dominates the SFPLL behaviour.

The contributions of this chapter are as follows:

• The proposal of the SFPLL which diminishes or overcomes the following problems inherent in PLLs: Reliable frequency acquisition, accurate free run frequency, locking to unwanted signals or sidebands, bandwidth change due to component variations, and VCO phase noise.

- The development of models to quantitatively describe the behaviour of the SFPLL and the verification of these models through simulations and experiments.

- The proposal of a digital implementation of the SFPLL which provides a high precision low cost realization of the SFPLL.

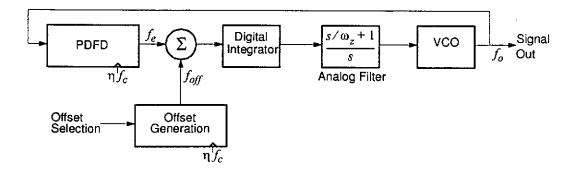

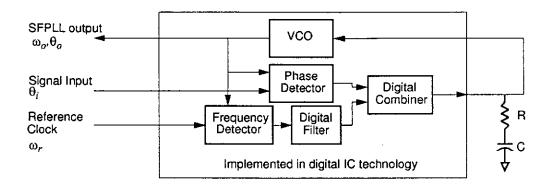

## 3.2. THE SFPLL AND ITS LINEAR MODEL

# 3.2.1. Analysis of SFPLL

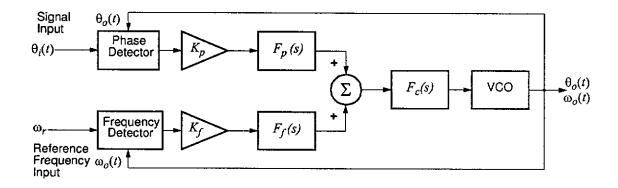

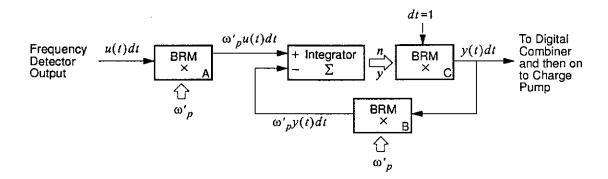

The structure of the SFPLL is shown in Figure 3-1. In Figure 3-1 the Phase Detector, Frequency Detector, and VCO have the gains  $K_{pd}$ ,  $K_{fd}$  and  $K_o$  respectively.  $K_p$  and  $K_f$  is additional gain.  $F_p(s)$ ,  $F_f(s)$  are filters which do not have poles at the origin.  $F_c(s)$  is a filter which may have one pole at the origin or may have no poles at the origin. Note that the phase detector detects only phase difference and doesn't perform any frequency discrimination.

**Figure 3-1.** The Steered Frequency Phase Locked Loop (SFPLL). The SFPLL can be thought of as two parts in competition against each other: a phase loop and a frequency loop. Each loop fights for control of the VCO.

The SFPLL can be thought of as two parts in competition against each other: a phase loop and a frequency loop. The frequency loop acts to force the VCO to be equal to the reference frequency. The phase loop acts to force the VCO to be equal to the frequency of the signal input. For a controllable range of input signal frequencies the phase loop is

able to phase lock to the input signal. The phase loop uses a static phase error to counteract the effects of the frequency loop.

Note that the phase variables  $\theta_i(t)$ ,  $\theta_o(t)$  describe the instantaneous angle of the signal. For example if the input signal is of constant frequency  $\omega$  and initial phase  $\theta_{i0}$ :

$$\theta_i(t) = \omega t + \theta_{i0} \tag{3-1}$$

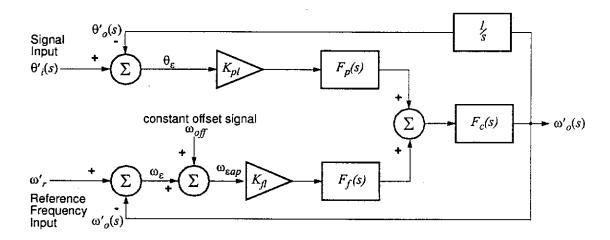

When the SFPLL is in the steady state and is locked to the signal input it can be represented by the small signal linear model shown in Figure 3-2.

Figure 3-2. Small signal linear model for the SFPLL with reference frequency offset

With reference to Figure 3-2, the new variables  $\omega'_{n}$  and  $\theta'_{i}(t)$  are defined as offsets from the free running frequency of the VCO  $\omega_{f}$ :

$$\theta'_{i}(t) = \theta_{i}(t) - \omega_{f}t \tag{3-2}$$

$$\omega'_{r} = \omega_{r} - \omega_{f} \tag{3-3}$$

$\omega'_{o}(t)$  and  $\theta'_{o}(t)$  are similarly defined as offsets from  $\omega_{f}$ :  $K_{pl}$  accounts for all the gains in the phase loop, and  $K_{fl}$  for all the gains in the frequency loop.

$$K_{pl} = K_{pd}K_pK_o (3-4)$$

$$K_{fl} = K_{fd}K_fK_o (3-5)$$

The output of the SFPLL can be determined for the case when the phase detector output  $\theta_{\varepsilon}(s)$  equals 0. For certain phase detectors, particularly in the field of clock recovery [28], the output  $\theta_{\varepsilon}(s)$  equals 0 when there is no input signal present. The SFPLL output when  $\theta_{\varepsilon}(s)$  equals 0 can be written as

$$\omega'_{o}(s) = \frac{K_{fl}F_{f}(s)F_{c}(s)}{1 + K_{fl}F_{f}(s)F_{c}(s)}(\omega'_{r}(s) + \omega_{off}(s))$$

(3-6)

A constant offset signal  $\omega_{off}$  has been added into the frequency loop of the SFPLL. The introduction of an offset in the frequency loop may be intentional or it may be due to undesirable offsets occurring in the frequency loop components. In the initial discussion of the small signal linear model the signal  $\omega_{off}$  should be assumed to be zero.

When  $\omega'_r$  is a constant reference frequency, the steady state value of  $\omega'_o(t)$  can be found using the final value theorem. For the case where  $F_c(s)$  does not contain a pole at the origin

$$\lim_{t \to \infty} \omega'_{o}(t) = \frac{K_{fl}}{1 + K_{fl}} (\omega'_{r} + \omega_{off})$$

(3-7)

For the case where  $F_c(s)$  does contain a pole at the origin

$$\lim_{t \to \infty} \omega'_{o}(t) = \omega'_{r} + \omega_{off}$$

(3-8)

Hence when the phase detector output  $\theta_{\varepsilon}(s)$  equals 0 the SFPLL tracks the reference frequency, as shown by (3-7) and (3-8).

Now consider when the input signal is present and the phase detector output  $\theta_{\varepsilon}(s)$  does not equal 0. The phase error  $\theta_{\varepsilon}(s)$  as a function of  $\theta'_{i}(s)$  is

$$\theta_{\varepsilon}(s) = \frac{s(1 + K_{fl}F_{f}(s)F_{c}(s))\theta'_{i}(s) - K_{fl}F_{f}(s)F_{c}(s)\frac{(\omega'_{r} + \omega_{off})}{s}}{s(1 + K_{fl}F_{f}(s)F_{c}(s)) + K_{pl}F_{p}(s)F_{c}(s)}$$

(3-9)

If the input signal is a signal of constant frequency  $\omega'$ . Then for the case where  $F_c(s)$  doesn't contain a pole at the origin, the steady state phase error  $\theta_{\varepsilon}$  is

$$\lim_{t \to \infty} \theta_{\varepsilon}(t) = \frac{(1 + K_{fl})\omega' - K_{fl}(\omega'_r + \omega_{off})}{K_{pl}}$$

(3-10)

If the assumption is made that

$$K_{fl} \gg 1$$

(3-11)

then

$$\lim_{t \to \infty} \theta_{\varepsilon}(t) \approx \frac{K_{fl}}{K_{pl}} (\omega' - (\omega'_r + \omega_{off}))$$

(3-12)

For the case where  $F_c(s)$  does contain a pole at the origin assumption (3-11) is not required and, the steady state phase error  $\theta_{\varepsilon}$  is

$$\lim_{t \to \infty} \theta_{\varepsilon}(t) = \frac{K_{fl}}{K_{pl}} (\omega' - (\omega'_r + \omega_{off}))$$

(3-13)

Equations (3-12) and (3-13) can be interpreted as follows. For the SFPLL to lock to an incoming frequency of  $\omega'$  the phase loop has to provide the appropriate phase lag/lead  $(\theta_{\rm E})$  to overcome the  $\omega'_r$  'pulling'.

Note that the maximum absolute value of  $\theta_{\varepsilon}(t)$  is finite, with maximum value  $\theta_{\varepsilon max}$

$$\left|\theta_{\varepsilon}(t)\right| \le \theta_{\varepsilon max} \tag{3-14}$$

Normally  $\theta_{\epsilon max}$  is at most  $2\pi$  and depending on the particular phase detector  $\theta_{\epsilon max}$  may be less. From (3-13) and (3-14)

$$\left|\omega' - (\omega'_r + \omega_{off})\right| \le \theta_{\epsilon max} \frac{K_{pl}}{K_{fl}}$$

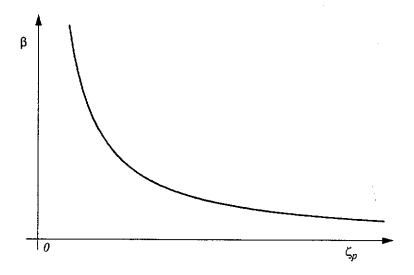

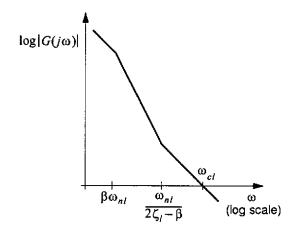

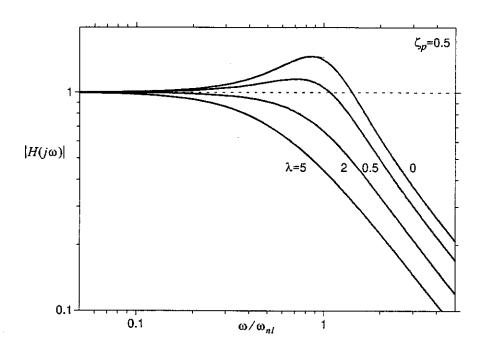

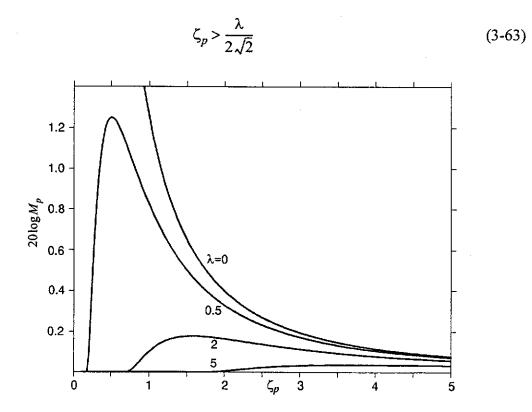

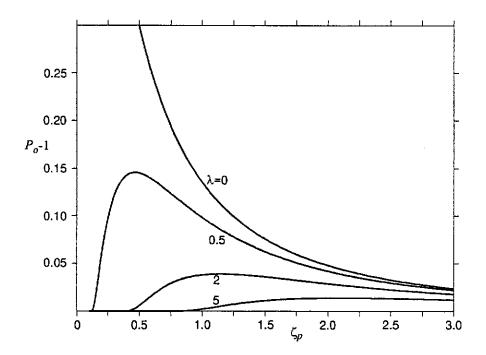

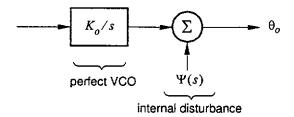

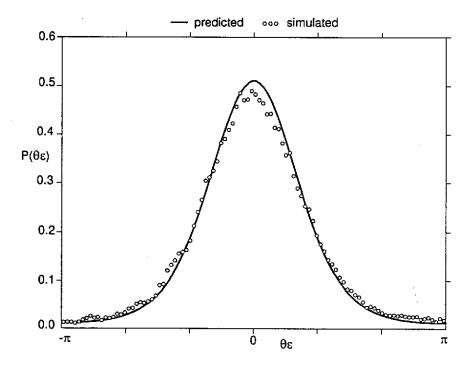

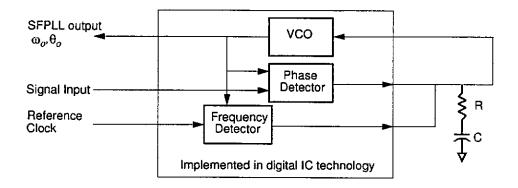

(3-15)