## **Faculty of Engineering and Science**

## A New Topology of Cross-Switched Multilevel Inverter

Nur Atiqah Binti Jefry

0000-0001-7835-9425

This thesis is presented for the Degree of Doctor of Philosophy of Curtin University **Declaration**

To the best of my knowledge and belief, this thesis contains no material previously

published by any other person except where due acknowledgment has been made.

This thesis contains no material which has been accepted for the award of any other

degree or diploma in any university.

Signature:

Date: 21st May 2022

i

## **List of Publications**

- "The new Topology of MLI with Reduced Number of Switches" in 2020 11th IEEE Control and System Graduate Research Colloquium

- "The New Hybrid Multilevel Inverter with Reduced Number of Switches" in 2021 IEEE 11<sup>th</sup> International Conference on System Engineering and Technology

### **Abstract**

Due to its importance in the power industry, multilevel inverter (MLI) is constantly researched for improvements. MLI that could produce a high level of output voltage with a reduced number of components is highly sought. The higher level of output will improve the THD percentage which eliminates the need for an output filter. The proposed topology was designed based on Cascaded H-Bridge (CHB)-MLI, Diode Clamped (DC)-MLI, and Cross Connected Source (CCS) – MLI. It consisted of 4 isolated DC sources, 4 diodes, and 10 switches. It can be configured with identical (symmetrical) and non-identical (asymmetrical) DC sources that resulted in 9-level, 13-level, and 17-level of voltage output. The proposed topology is also hybridized with H-MLI to produce 51-level of output. The proposed topology was verified with Matlab/Simulink simulation and supported by experimental testing. The testing was conducted in no-load and loading conditions with the modulation index, m equal to 1.0, 0.8, 0.5, and 0.3. The THD percentage (from simulation in loading conditions) produced by 9-level, 13-level, 17-level, and 51-level configurations is 10.21%, 7.83%, 6.42%, and 1.78%, respectively. The 51-level configuration was also implemented into a STATCOM as an example of an industrial application, and the operation was verified with simulation. Finally, the proposed topology was compared with the conventional MLIs and recently published MLI topologies. The outcomes concluded that the proposed topology uses a smaller number of components to generate a high level of output voltage, has a low THD percentage, and has a simpler structure. This study demonstrates that the proposed topology still has room for further improvements. Perhaps, in the future, the proposed topology can be cascaded to achieve a higher level of output voltage, or the dc-link capacitor can be introduced to reduce the dependency on the isolated DC sources.

## Acknowledgement

In the name of Allah, the Most Gracious and the Most Merciful.

First and foremost, I would like to thank Dr. Ammar Masaoud and Dr. Law Kah Haw, now ex-lecturer of Department of Electrical and Computer Engineering, for their guidance, encouragement, and help throughout this study. Their unbounded guidance has made it possible for me to overcome the difficulties and complete this thesis. Their advice, recommendations, and suggestions help me to produce a reliable, dependable, and authentic thesis. Their never-ending encouragement also helped me to bounce back to my feet whenever I was on the verge of giving up. I am also thankful to Dr. Wong Kiing Ing for assisting me after Dr. Ammar and Dr. Law left. He reached out to me and make sure I am not alone and lost. Thank you very much.

I also would like to express my gratitude to the Head of the Electrical and Computer Engineering Department, Dr. Lenin for his continuous support towards my postgraduate affairs as well to the Graduate School for their willingness in assisting me to navigate through my study welfare.

Special thanks to my parents for their unwavering faith, unconditional love, and for every sacrifice they did for me to ensure my journey proceed smoothly. Without them, I doubt I will be writing this today. I am also thankful to my friends and family who never give up encouraging me. It is truly because of them I decided to brace through this journey till the end.

Finally, I would like to thank Curtin Sarawak for giving me the opportunity to conduct this study smoothly and able to contribute to the academic world.

Only Allah can repay your kindness!

Nur Atiqah Binti Jefry

## **Table of Contents**

| Declaration                                        | i                  |

|----------------------------------------------------|--------------------|

| List of Publication                                | ii                 |

| Abstract                                           | iii                |

| Acknowledgment                                     | iv                 |

| Table of Contents                                  | v                  |

| List of Figures                                    | viii               |

| List of Tables.                                    | xii                |

| Abbreviation List                                  | xiv                |

| Chapter 1: Introduction                            |                    |

| 1.1 Building Justification                         |                    |

| 1.1.1 The Research Field                           | 2                  |

| 1.1.2 The Research Gaps                            | 3                  |

| 1.1.3 Research Questions                           | 4                  |

| 1.2 Objectives                                     | 4                  |

| 1.3 Outcome and Significance                       | 4                  |

| 1.4 Ethical Issues                                 | 5                  |

| 1.5 Facilities and Resources.                      | 5                  |

| 1.6 Data Storage                                   | 5                  |

| 1.7 Thesis Outline                                 | 6                  |

| Chapter 2: Literature Review on MLI, Modulation Te | chniques & STATCOM |

| 2.1 Chapter Introduction                           | 7                  |

| 2.2 The Overview of Inverter.                      | 7                  |

| 2.2.1 The Two-level Inverter                       | 7                  |

| 2.2.2 CHB-MLI                                      | 8                  |

| 2.2.3 FC-MLI                                       | 10                 |

| 2.2.4 DC-MLI                                       | 14                 |

| 2.2.5 CCS-MLI                                      | 16                 |

| 2.3 Modulation Techniques                          | 18                 |

| 2.3.1 CB-PWM                                       | 19                 |

| 2.3.2 SV-PWM                                       | 20                 |

| 2.3.3 SHE                                                  | 22 |

|------------------------------------------------------------|----|

| 2.3.4 Nearest Control Method                               | 23 |

| 2.4 STATCOM                                                | 24 |

| 2.4.1 STATCOM Overview                                     | 24 |

| 2.4.2 The Control Scheme                                   | 25 |

| 2.5 Conclusion.                                            | 26 |

| Chapter 3: Research Methodology                            |    |

| 3.1 Chapter Introduction                                   | 28 |

| 3.2 Research Methodology                                   | 28 |

| 3.3 TI Control Suite and Code Composer Studio              | 31 |

| 3.4 Measuring Instruments                                  | 35 |

| 3.5 Conclusion.                                            | 36 |

| Chapter 4: The Proposed Topology & Hardware Implementation |    |

| 4.1 Chapter Introduction.                                  | 37 |

| 4.2 The Proposed Topology                                  | 37 |

| 4.3 Hybrid Configuration                                   | 40 |

| 4.4 The Proposed Topology Prototype                        | 42 |

| 4.5 Conclusion.                                            | 46 |

| Chapter 5: Simulation and Experimental Results Analysis    |    |

| 5.1 Chapter Introduction.                                  | 47 |

| 5.2 Simulation Analysis                                    | 47 |

| 5.2.1 9-level Configuration                                | 47 |

| 5.2.2 13-level Configuration.                              | 52 |

| 5.2.3 17-level Configuration                               | 58 |

| 5.2.4 51-level Configuration.                              | 62 |

| 5.3 Experimental Testing Analysis                          | 69 |

| 5.3.1 9-level Configuration                                | 70 |

| 5.3.2 13-level Configuration.                              | 76 |

| 5.3.3 17-level Configuration                               | 83 |

| 5.3.4 51-level Configuration                               | 90 |

| 5.4 Conclusion.                                            | 98 |

# **Chapter 6: Comparative Analysis & STATCOM**

| 6.1 Chapter Introduction                            | 100 |

|-----------------------------------------------------|-----|

| 6.2 Comparative Analysis                            | 100 |

| 6.2.1 Comparison with Conventional MLI              | 100 |

| 6.2.2 Comparison with Recently Presented MLI        | 104 |

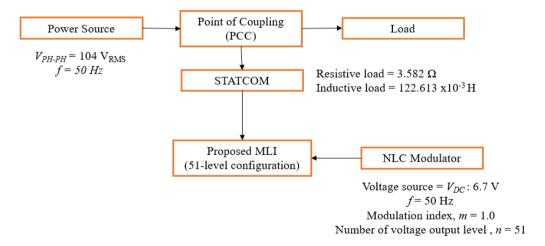

| 6.3 STATCOM as an Example of Industrial Application | 108 |

| 6.3.1 The Simulation Result                         | 109 |

| 6.4 Conclusion                                      | 112 |

| Chapter 7: Conclusion & The Recommendation          |     |

| 7.1 Chapter Introduction.                           | 113 |

| 7.2 Conclusion                                      | 113 |

| 7.3 Recommendation & Improvement                    | 114 |

| Reference                                           |     |

| Appendix A                                          |     |

| Appendix B                                          |     |

| Appendix C                                          |     |

| Appendix D                                          |     |

## **List of Figures**

# Chapter 2

| Figure 2.1: The three phase two-level inverter                              | 8     |

|-----------------------------------------------------------------------------|-------|

| Figure 2.2: H-MLI configuration.                                            | 9     |

| Figure 2.3: The basic suggested MLI unit for topology presented in          |       |

| (Samsami, Taheru, & Samanbakhsh, 2017)                                      | 10    |

| Figure 2.4: Five-level capacitor clamped converter (Fujita,                 |       |

| 2012)                                                                       | 11    |

| Figure 2.5: Circuit configuration per phase for n-level FC-MLI              |       |

| (Mochidate, Matsuo, Obara, & Sato, 2016)                                    | 12    |

| Figure 2.6: The presented topology in (Franquello, et al., 2008)            | 14    |

| Figure 2.7: (Left) The type 1 and (Right) type 2                            | 15    |

| Figure 2.8 : Topology presented in (Zolfaghar, Najafi, & Hasanzadeh, 2018)  | 16    |

| Figure 2.8: A five-level CCS-MLI as being presented in                      | 10    |

| (Gupta & Jain, 2014)                                                        | 17    |

| Figure 2.9: The proposed CCS-MLI in (Dewangan, Gurjar, Ullah, &             |       |

| Zafar, 2014)                                                                | 18    |

| Figure 2.11: (a) Phase/in-phase disposition, (b) Alternative phase opposite |       |

| disposition, and (c) Phase opposite disposition                             | 20    |

| Figure 2.12: The switching diagram for two-level inverter                   |       |

| (Space Vector Modulation, 2017)                                             | 21    |

| Figure 2.13: Multiple switching angle of PWM (Ahmadi, Zou, Li, Huang,       |       |

| & Wang, 2011)                                                               | 22    |

| Figure 2.14: The single-phase equivalent circuit of the                     |       |

| STATCOM system (Subramaniam, Ramkumar, A.Amudha, &                          |       |

| Kuppusamy, 2017)                                                            | 25    |

| Chapter 3                                                                   |       |

| Figure 3.1: The NLC modulator setup                                         | 29    |

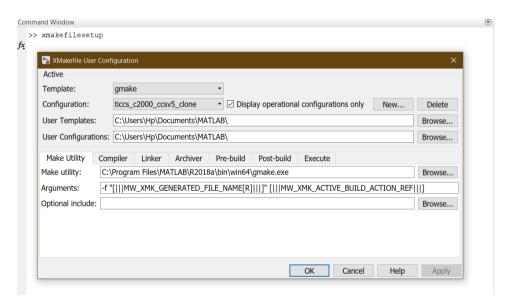

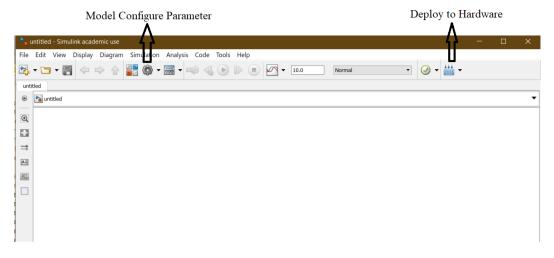

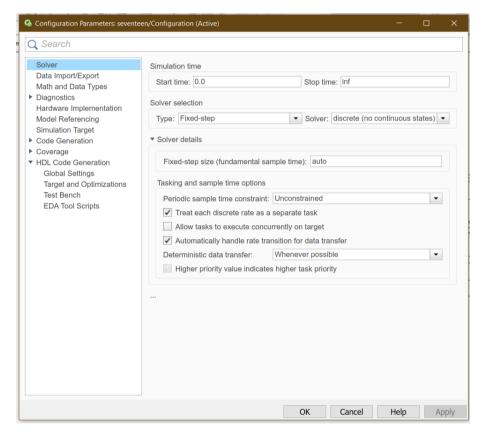

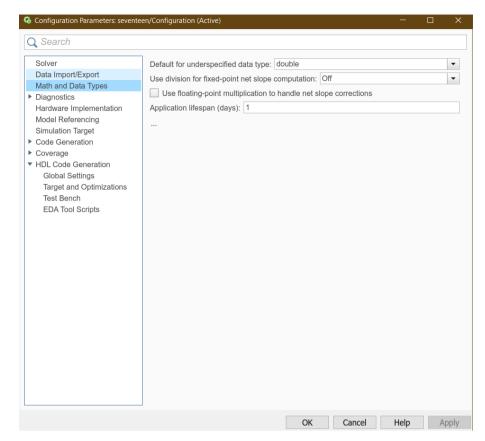

| Figure 3.2: The "xmakefilesetup" configuration                              | 31    |

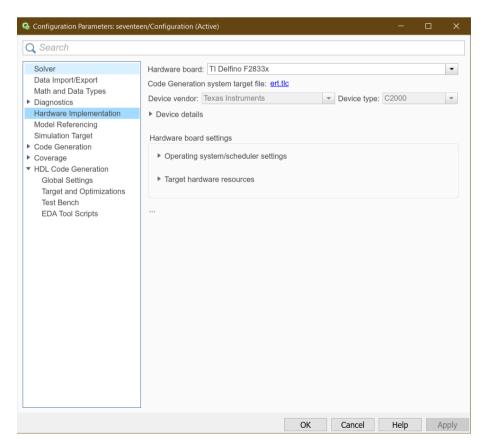

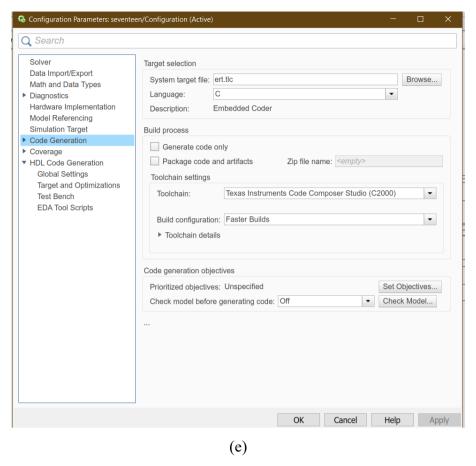

| Figure 3.3 (a-e): The parameter configuration                               | 32-34 |

| Figure 3.4: The flow of switching signals                                   | 34    |

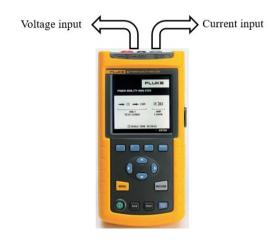

| Figure 3.5: A photo of Fluke 43B (Fluke, 2001)                              | 35    |

# Chapter 4

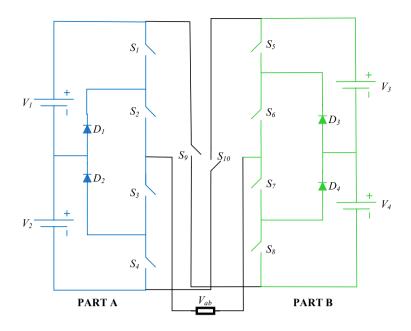

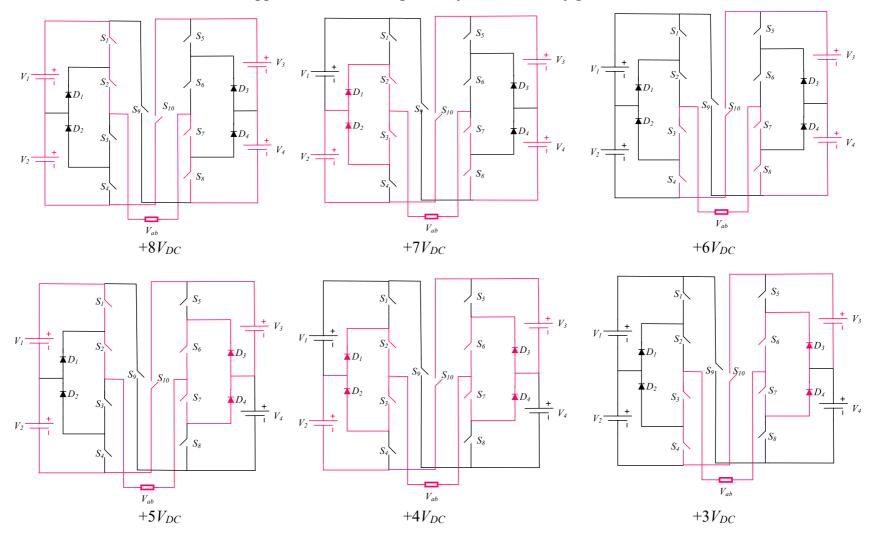

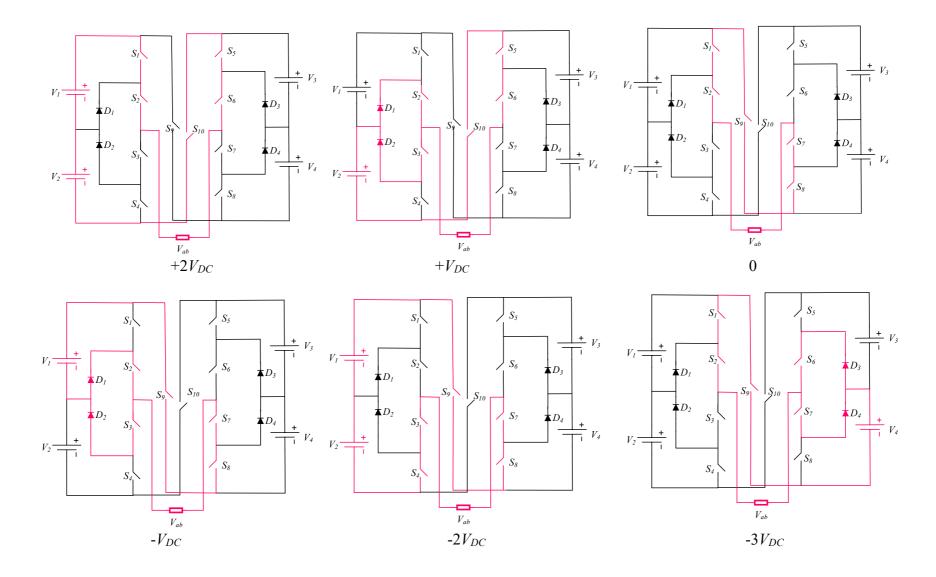

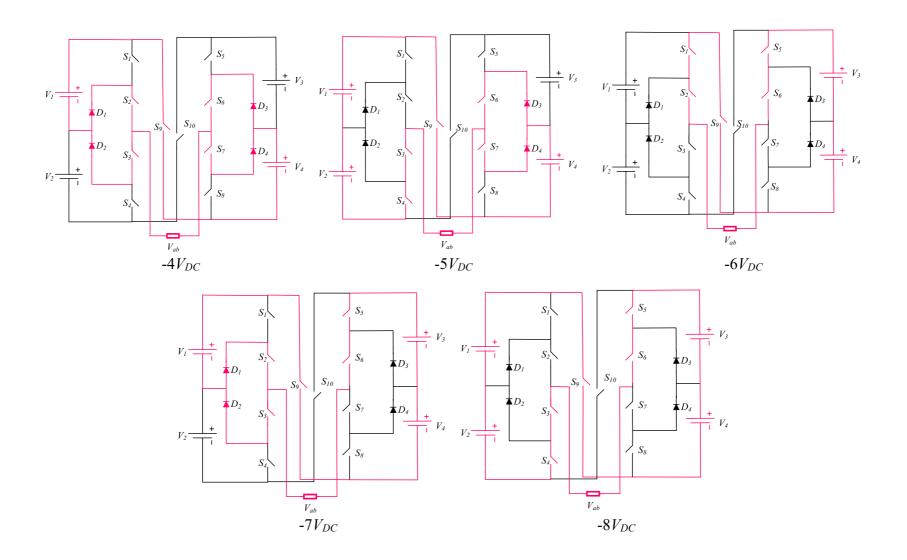

| Figure 4.1: The proposed topology                                                     | 38    |

|---------------------------------------------------------------------------------------|-------|

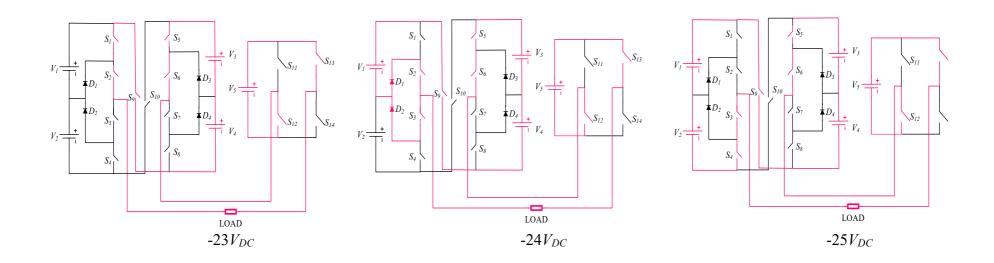

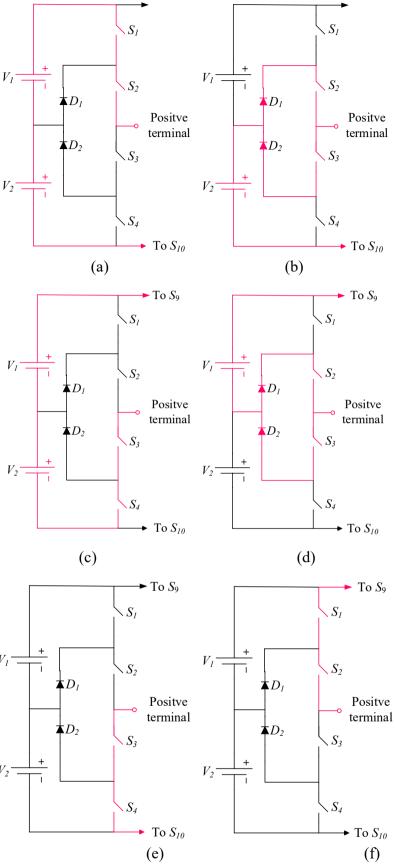

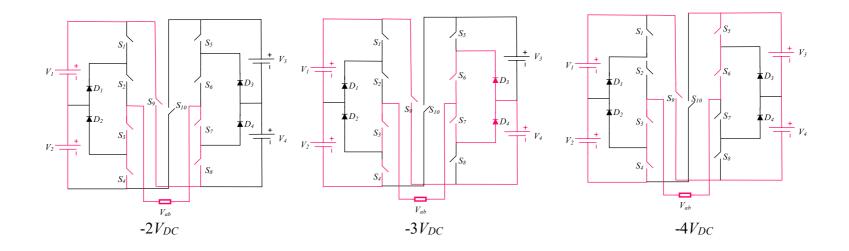

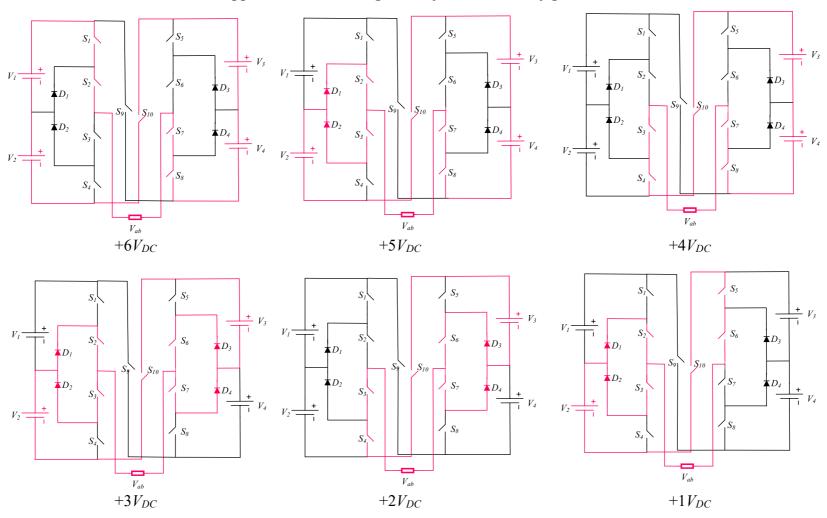

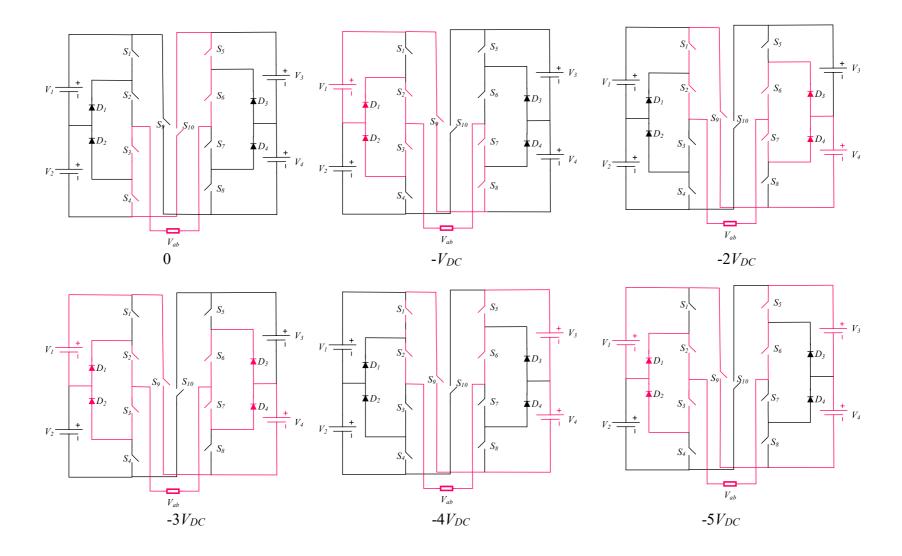

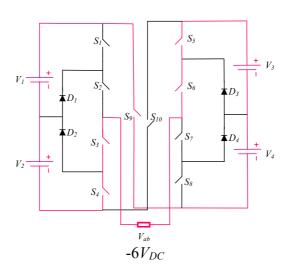

| Figure 4.2: The switching mode for (a) $V_1+V_2$ , (b) $V_2$ , (c) $-(V_1+V_2)$ , (d) |       |

| $-V_I$ , and (e)-(f) zero state                                                       | 39    |

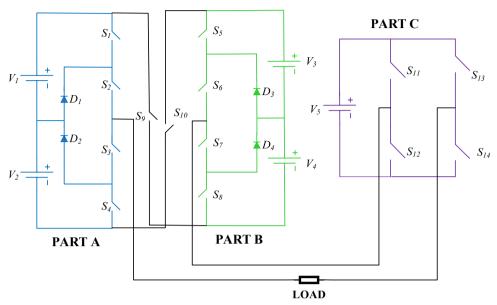

| Figure 4.3: The hybrid configuration                                                  | 41    |

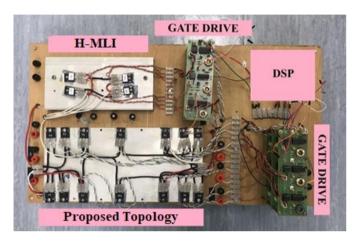

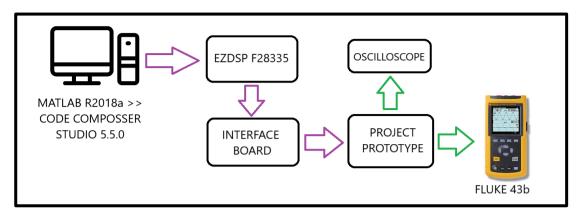

| Figure 4.4: The hardware prototype                                                    | 42    |

| Figure 4.5: The experimental testing arrangement                                      | 43    |

| Figure 4.6: The (a) the schematic diagram and,                                        |       |

| (b) the actual photo (IRG4PH50UDPbF,2004)                                             | 43    |

| Figure 4.7: The actual photo of DSP                                                   | 44    |

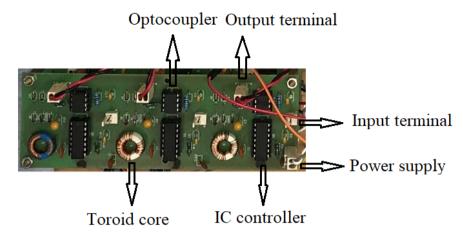

| Figure 4.8: The gate drives that are fixed onto interface board                       | 45    |

| Chapter 5                                                                             |       |

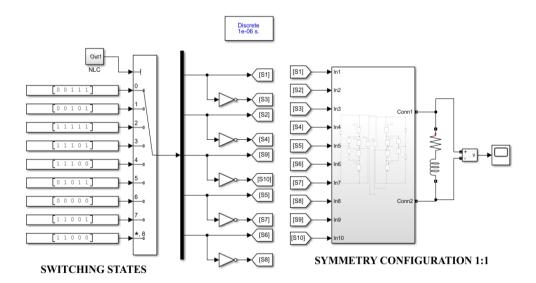

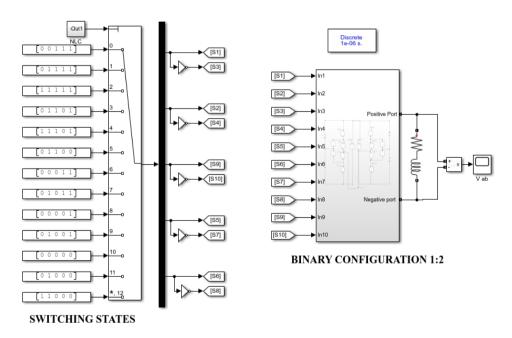

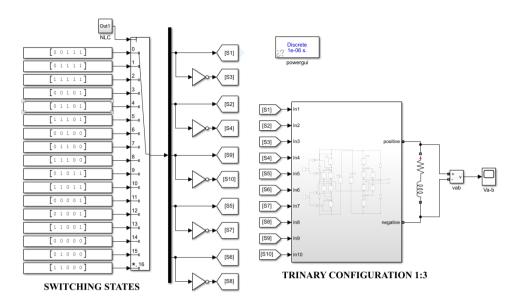

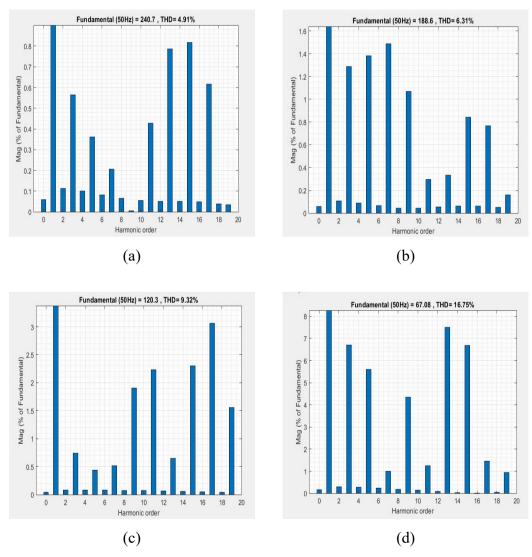

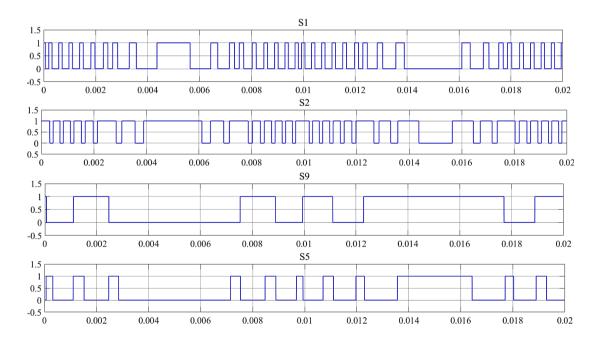

| Figure 5.1: The simulation setup for 9-level configuration                            | 48    |

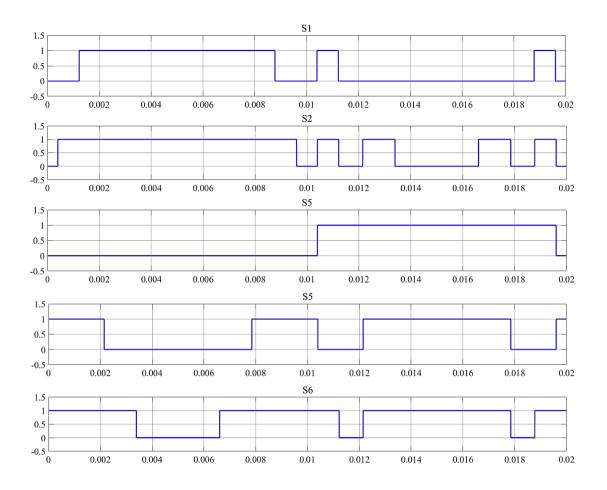

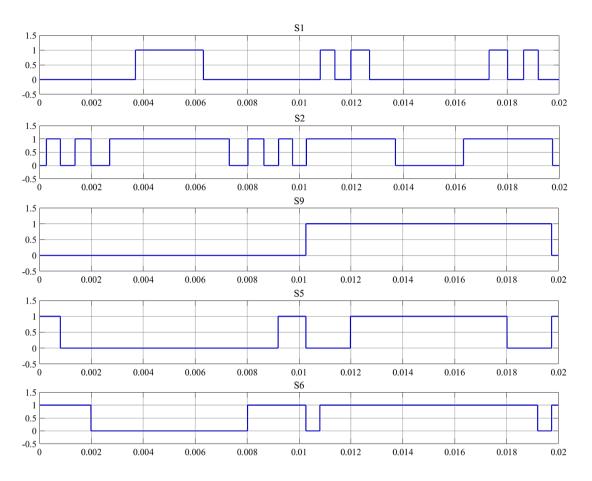

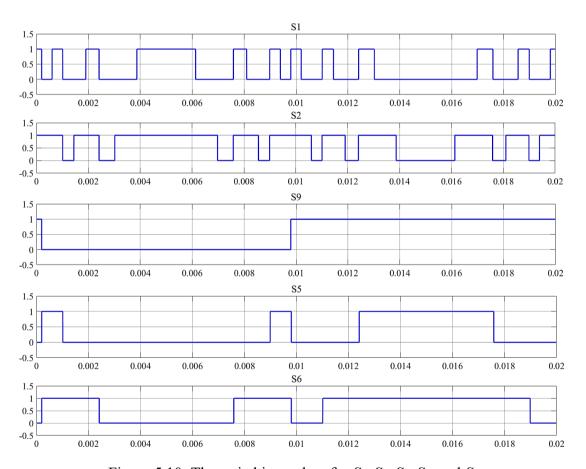

| Figure 5.2: The switching pulses for $S_1$ , $S_2$ , $S_9$ , $S_5$ , and $S_6$        | 49    |

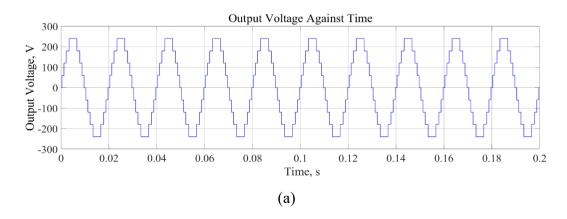

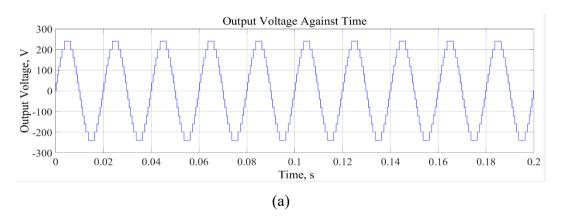

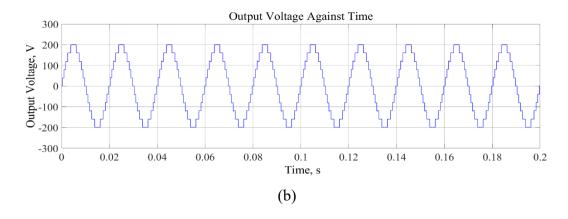

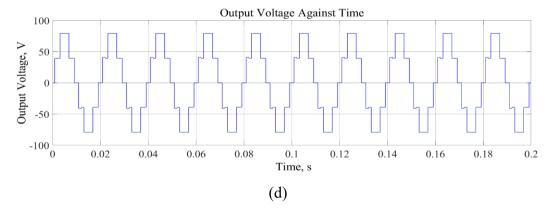

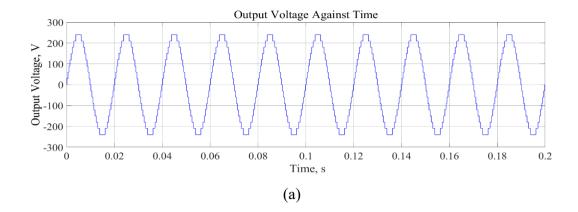

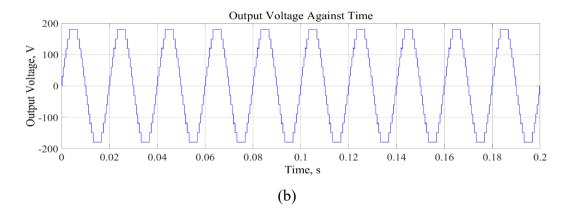

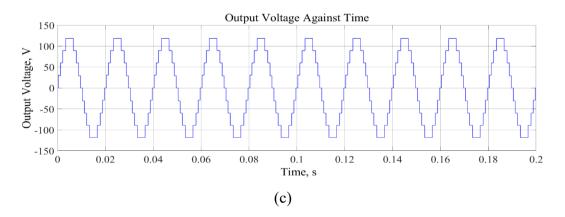

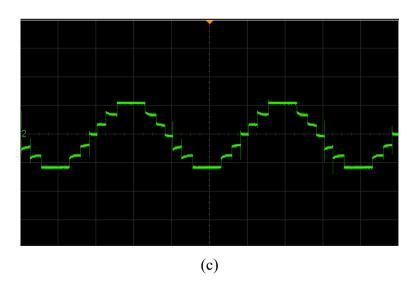

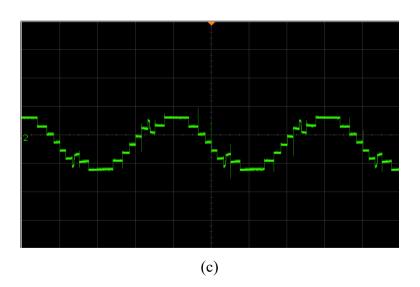

| Figure 5.3: The output voltages for $m = (a) 1$ , $(b) 0.8$ , $(c) 0.5$ ,             |       |

| and (d) 0.3                                                                           | 49-50 |

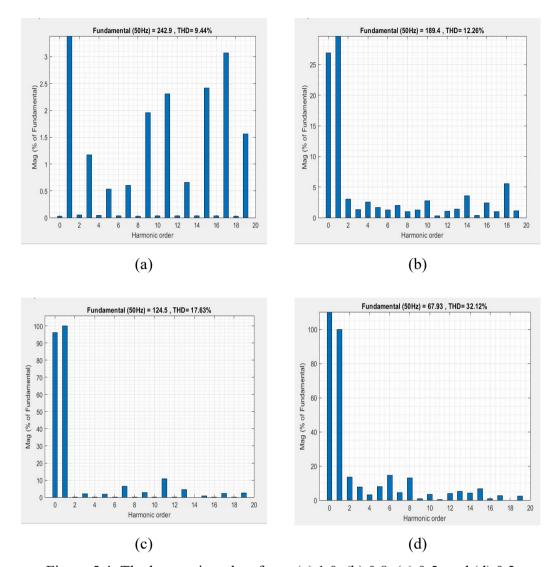

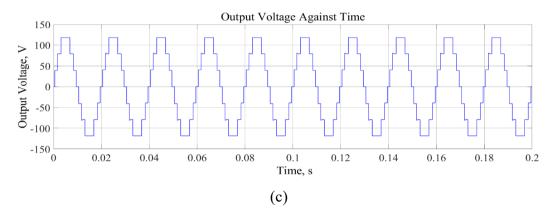

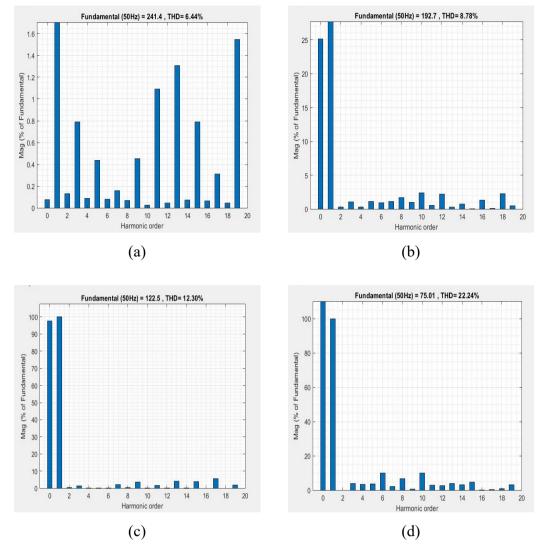

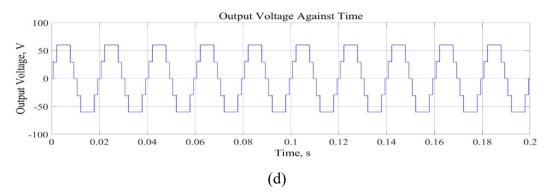

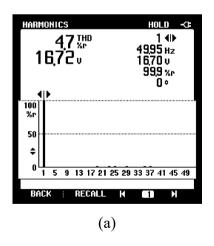

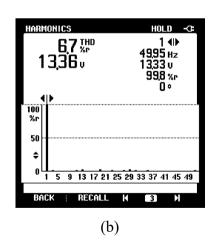

| Figure 5.4: The harmonic orders for $m$ (a) 1.0, (b) 0.8,                             |       |

| (c) 0.5, and (d) 0.3                                                                  | 51    |

| Figure 5.5: The simulation setup for the 13-level configuration                       | 53    |

| Figure 5.6: The switching pulses for $S_1$ , $S_2$ , $S_9$ , $S_5$ , and $S_6$        | 54    |

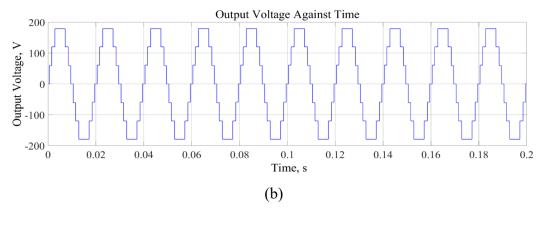

| Figure 5.7: The output voltages for $m = (a) 1.0$ , (b) 0.8, (c) 0.5                  |       |

| and (d) 0.3                                                                           | 54-55 |

| Figure 5.8: The harmonic orders for $m = (a) 1.0$ , (b) 0.8, (c) 0.5,                 |       |

| and (d) 0.3                                                                           | 56    |

| Figure 5.9: The simulation setup for the 17-level configuration                       | 59    |

| Figure 5.10: The switching pulses for $S_1$ , $S_2$ , $S_9$ , $S_5$ , and $S_6$       | 59    |

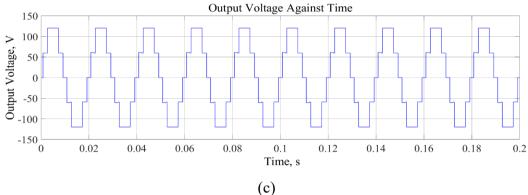

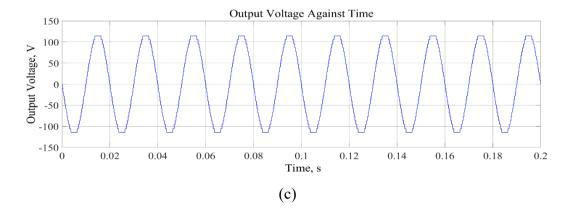

| Figure 5.11: The output voltages for $m = (a) 1.0$ , $(b) 0.8$ , $(c) 0.5$ ,          |       |

| and (d) 0.3                                                                           | 60-61 |

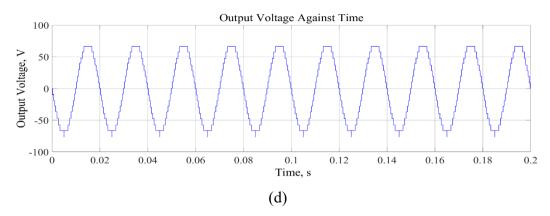

| Figure 5.12: The harmonic orders for $m = (a) 1.0$ , (b) 0.8, (c) 0.5,                |       |

| and (d) 0.3                                                                           | 61    |

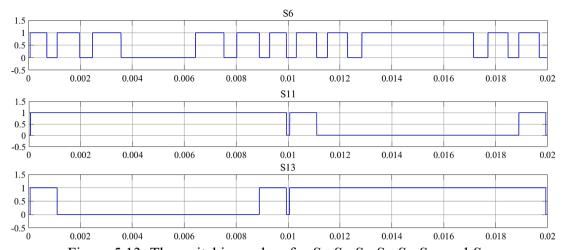

| Figure 5.13: The switching pulse for $S_1$ , $S_2$ , $S_9$ , $S_5$ , $S_6$ , $S_{11}$ , and $S_{13}$ | 64- |

|------------------------------------------------------------------------------------------------------|-----|

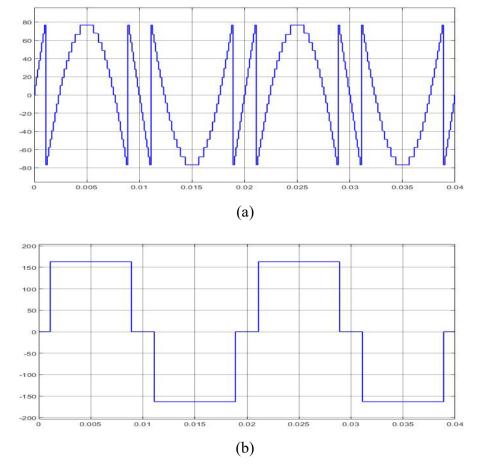

| Figure 5.14: The voltage trains from (a) Part A and Part B,                                          |     |

| and (b) Part C                                                                                       | 65  |

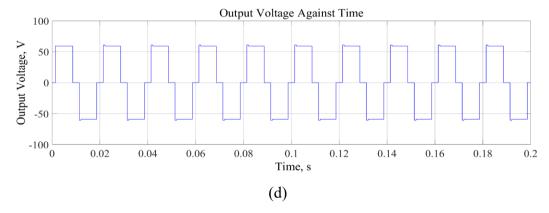

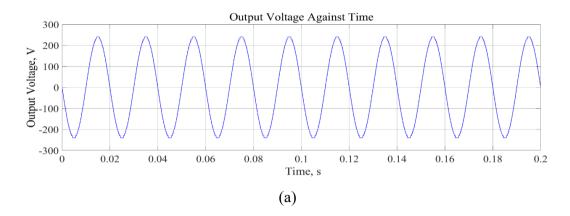

| Figure 5.15: The output voltages for $m = (a) 1.0$ , $(b) 0.8$ , $(c) 0.5$ ,                         |     |

| and (d) 0.3                                                                                          | 66- |

| Figure 5.16: The harmonic orders when $m = (a) 1.0$ , $(b) 0.8$ , $(c) 0.5$ ,                        |     |

| and (d) 0.3                                                                                          | 68  |

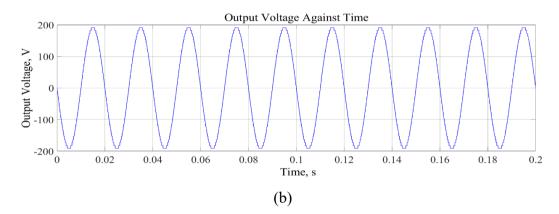

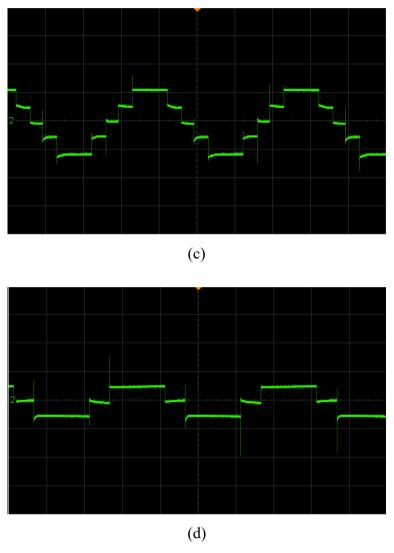

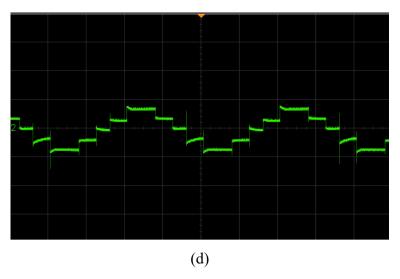

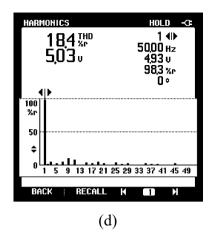

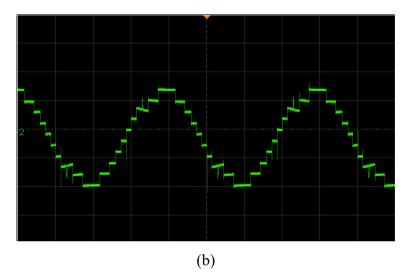

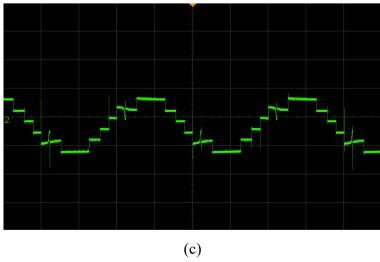

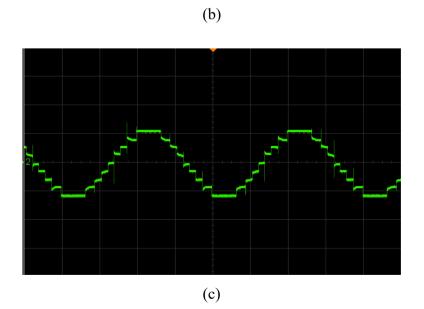

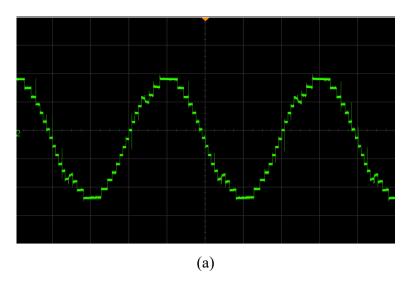

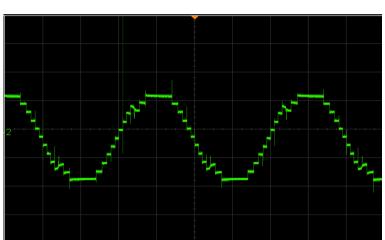

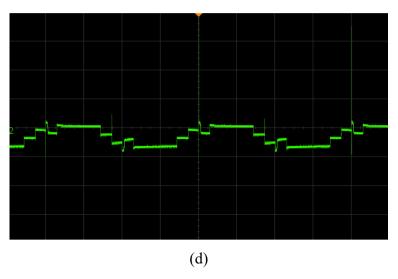

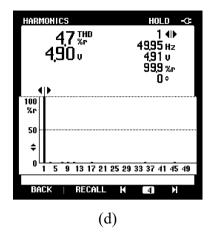

| Figure 5.17: The output voltages for $m = (a) 1.0$ , $(b) 0.8$ , $(c) 0.5$ ,                         |     |

| and (d) 0.3                                                                                          | 70  |

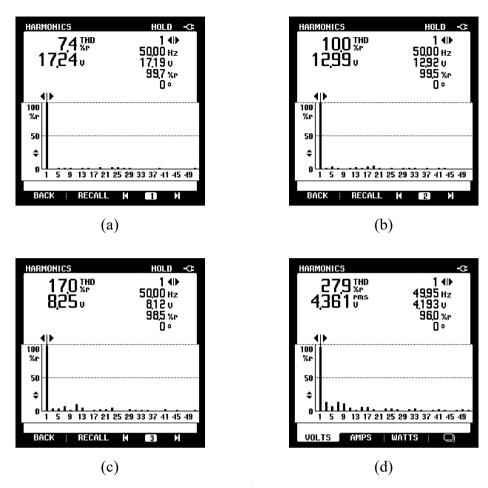

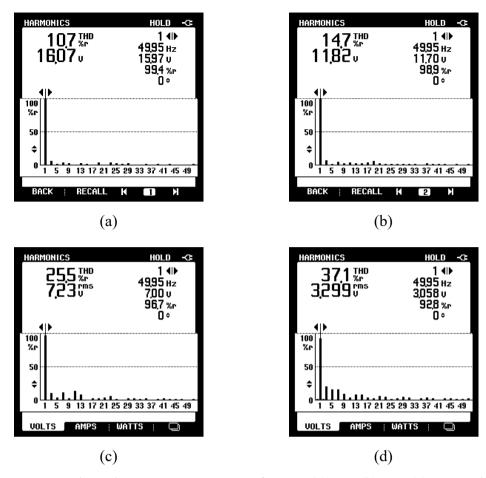

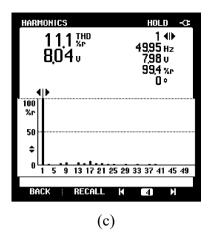

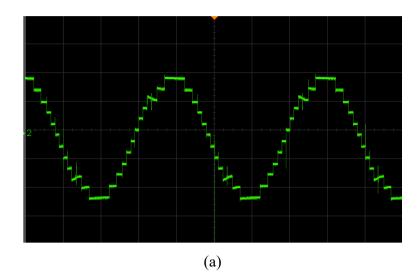

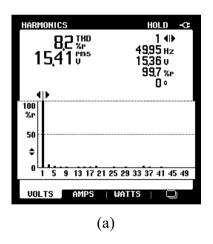

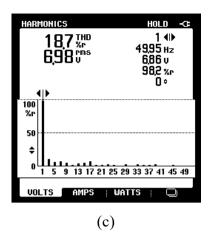

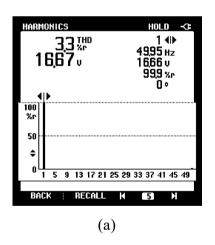

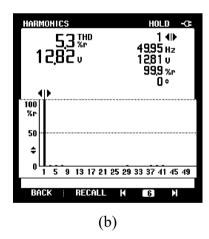

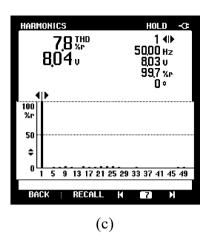

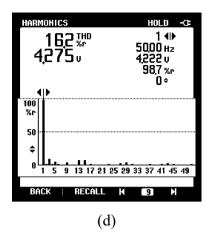

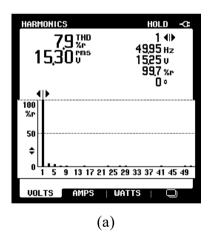

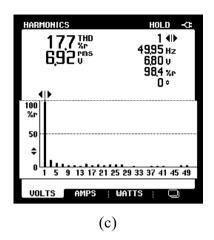

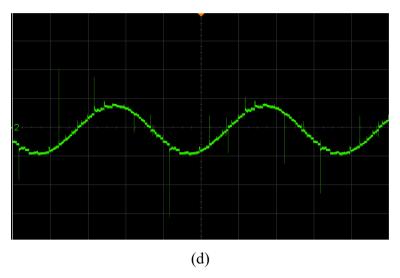

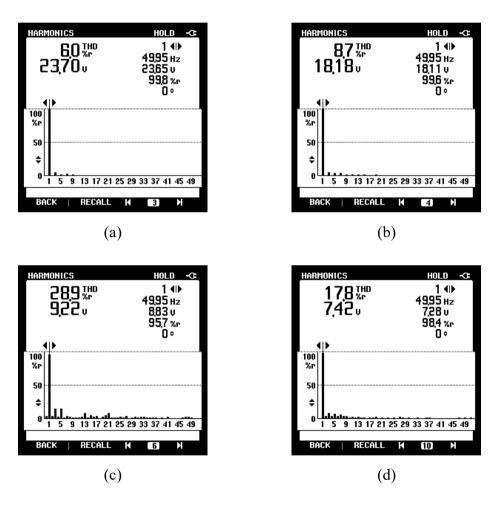

| Figure 5.18: The voltage THD percentages for $m = (a) 1.0$ , $(b) 0.8$ , $(c)$                       |     |

| 0.5, and (d) 0.3                                                                                     | 72  |

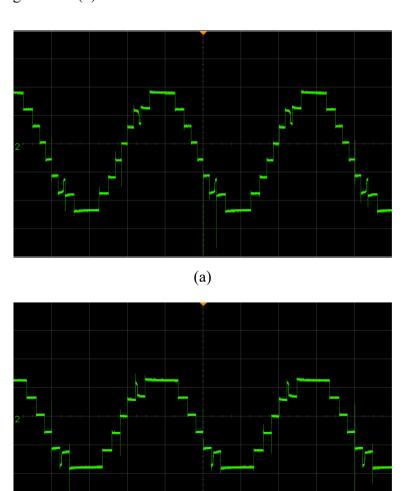

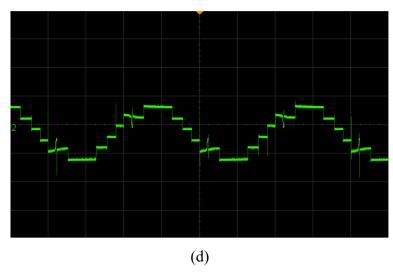

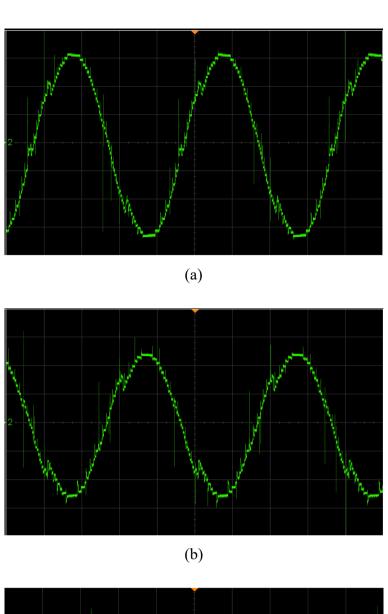

| Figure 5.19: The voltage output voltages for $m = (a) 1.0$ , $(b) 0.8$ , $(c) 0.5$ ,                 |     |

| and (d) 0.3                                                                                          | 73  |

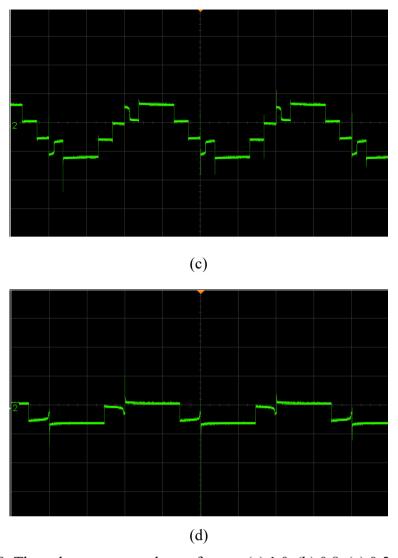

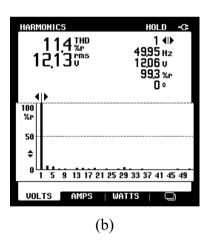

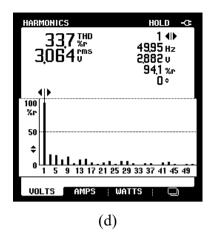

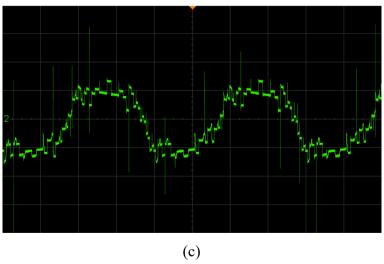

| Figure 5.20: The voltage THD percentages for $m = (a) 1.0$ , $(b) 0.8$ , $(c) 0.5$ ,                 |     |

| and (d) 0.3                                                                                          | 75  |

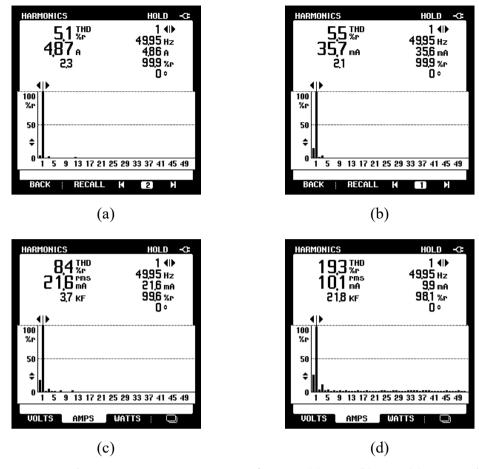

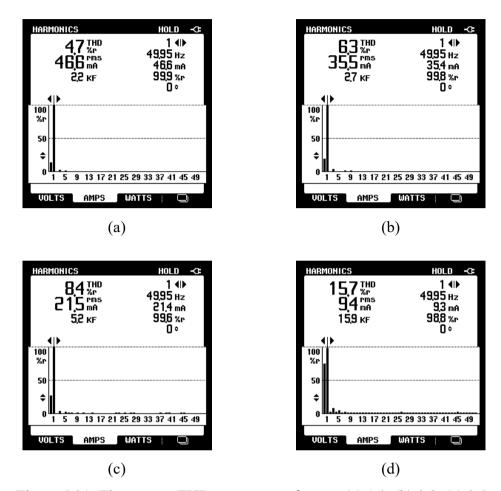

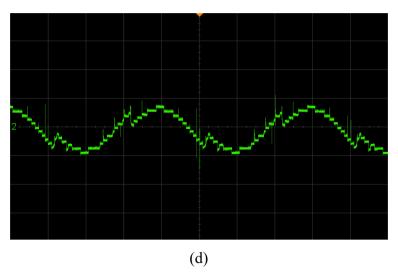

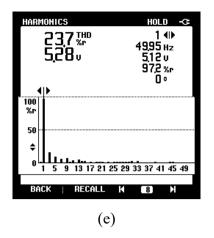

| Figure 5.21: The current THD percentages for $m = (a) 1.0$ , $(b) 0.8$ , $(c) 0.5$ ,                 |     |

| and (d) 0.3                                                                                          | 76  |

| Figure 5.22: The output voltages for $m = (a) 1.0$ , (b) 0.8, (c) 0.5,                               |     |

| and (d) 0.3                                                                                          | 77  |

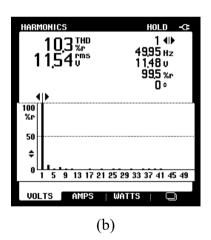

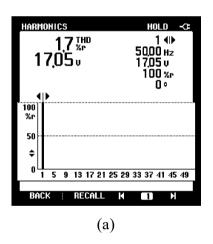

| Figure 5.23: The voltage THD percentages for $m = (a) 1.0$ , $(b) 0.8$ , $(c) 0.5$ ,                 |     |

| and (d) 0.3                                                                                          | 78  |

| Figure 5.24: The output voltages for $m = (a) 1.0$ , $(b) 0.8$ , $(c) 0.5$ ,                         |     |

| and (d) 0.3                                                                                          | 80  |

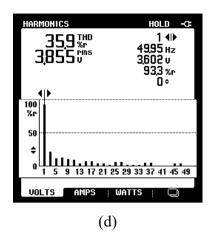

| Figure 5.25: The voltage THD percentages for $m = (a) 1.0$ , $(b) 0.8$ , $(c) 0.5$ ,                 |     |

| and (d) 0.3                                                                                          | 81  |

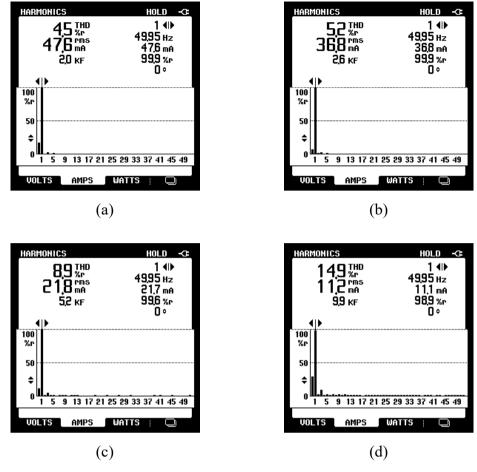

| Figure 5.26: The current THD percentages for $m = (a) 1.0$ , $(b) 0.8$ , $(c) 0.5$ ,                 |     |

| and (d) 0.3                                                                                          | 83  |

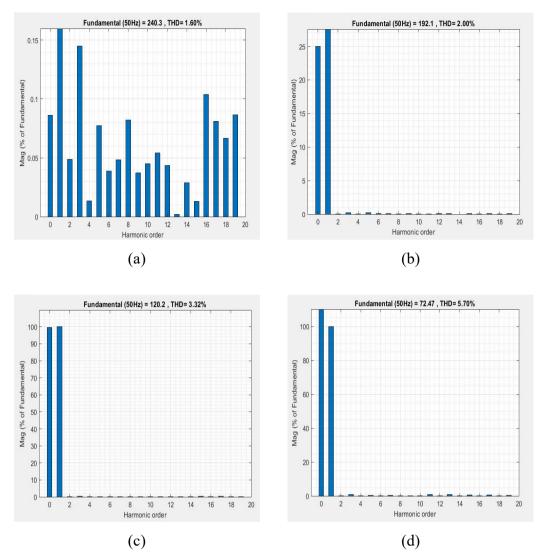

| Figure 5.27: The output voltages for $m = (a) 1.0$ , $(b) 0.8$ , $(c) 0.5$ ,                         |     |

| and (d) 0.3                                                                                          | 84  |

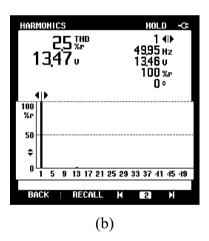

| Figure 5.28: The voltage THD percentages for $m = (a) 1.0$ , $(b) 0.8$ , $(c)$                       |     |

| 0.5, and (d) 0.3                                                                                     | 85  |

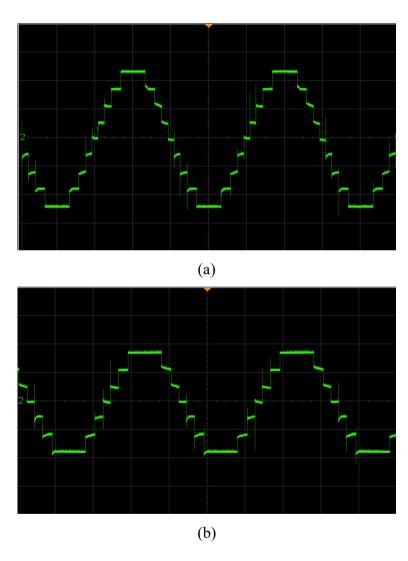

| Figure 5.29: The output voltages for $m = (a) 1.0$ , $(b) 0.8$ , $(c) 0.5$ ,                         |     |

| and (d) 0.3                                                                                          | 87  |

| Figure 5.30: The voltage THD percentages for $m = (a) 1.0$ , $(b) 0.8$ , $(c) 0.5$ ,     |       |

|------------------------------------------------------------------------------------------|-------|

| and (d) 0.3                                                                              | 88-89 |

| Figure 5.31: The current THD percentages for $m = (a) 1.0$ , $(b) 0.8$ , $(c) 0.5$ ,     |       |

| and (d) 0.3                                                                              | 90    |

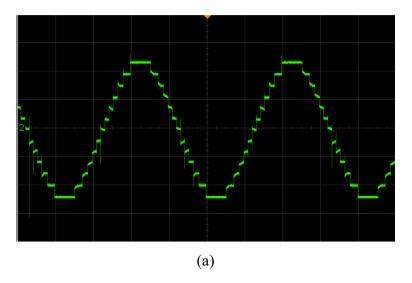

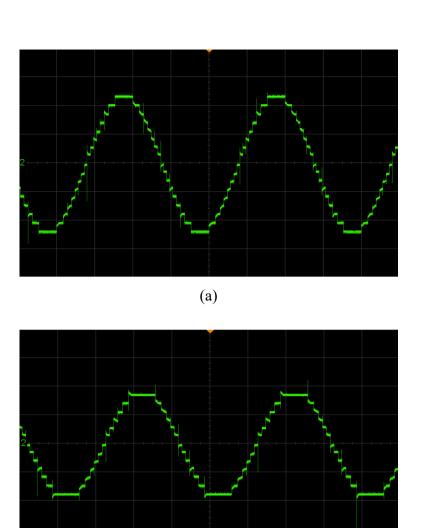

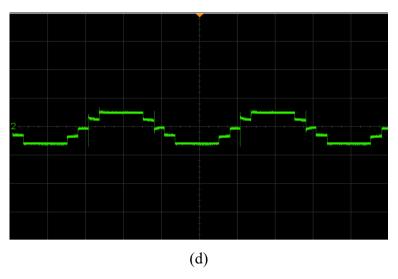

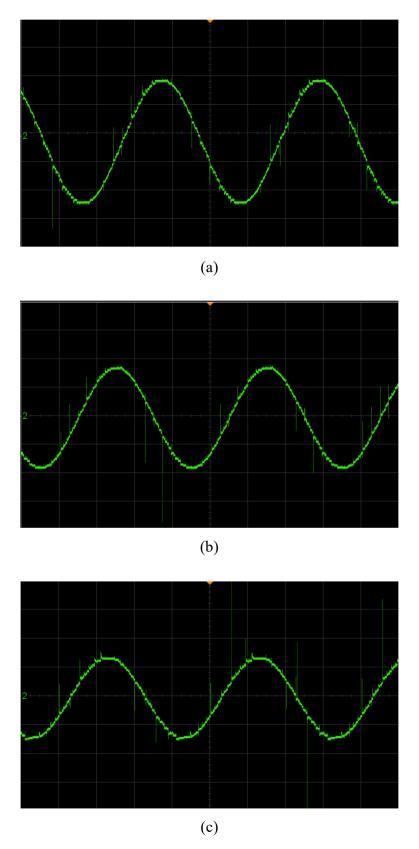

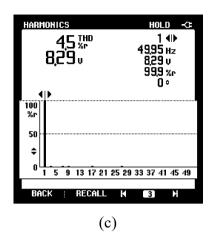

| Figure 5.32: The output voltages for $m = (a) 1.0$ , (b) 0.8, (c) 0.5,                   |       |

| and (d) 0.3                                                                              | 91-92 |

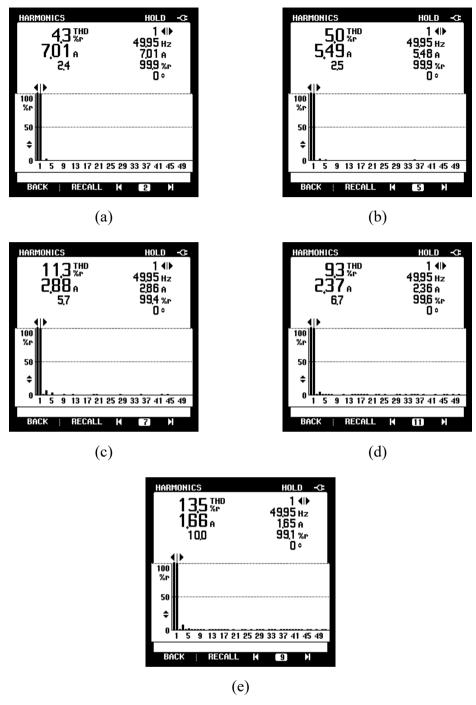

| Figure 5.33: The voltage THD percentages for $m = (a) 1.0$ , $(b) 0.8$ , $(c) 0.5$ ,     |       |

| and (d) 0.3                                                                              | 92-93 |

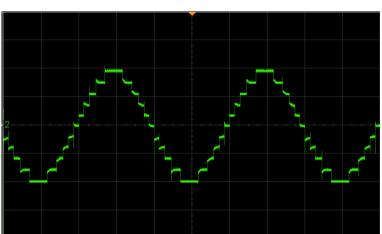

| Figure 5.34: The output voltages for $m = (a) 1.0$ , (b) 0.8, (c) 0.5,                   |       |

| and (d) 0.3                                                                              | 94-95 |

| Figure 5.35: The output voltages for $m = 0.4$                                           | 95    |

| Figure 5.36: The THD percentages for $m = (a) 1.0$ , $(b) 0.8$ , $(c) 0.5$ , $(d) 0.4$ , |       |

| and (e) 0.3                                                                              | 96-97 |

| Figure 5.37: The THD percentages for $m = (a) 1.0$ , $(b) 0.8$ , $(c) 0.5$ , $(d) 0.4$ , |       |

| and (e) 0.3                                                                              | 98    |

| Chapter 6                                                                                |       |

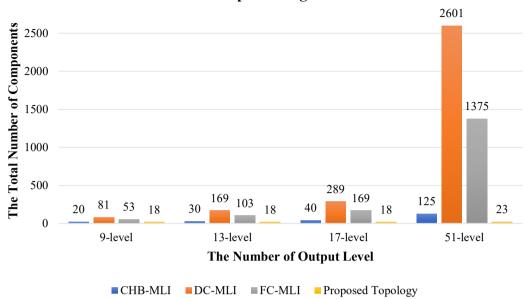

| Figure 6.1: The comparison between the number of components and the                      |       |

| number of voltage output level for CHB-MLI, DC-MLI, FC-MLI, and the                      |       |

| proposed topology                                                                        | 103   |

| Figure 6.2: STATCOM simulation flowchart                                                 | 109   |

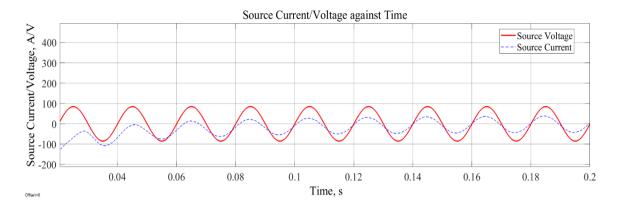

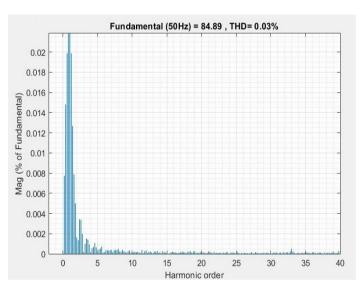

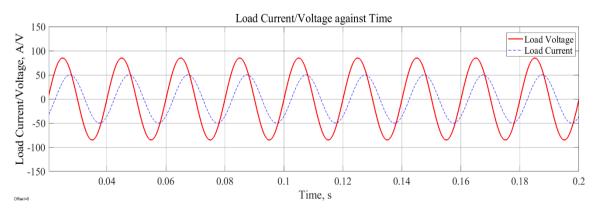

| Figure 6.3: The voltage and current waveform at source                                   | 110   |

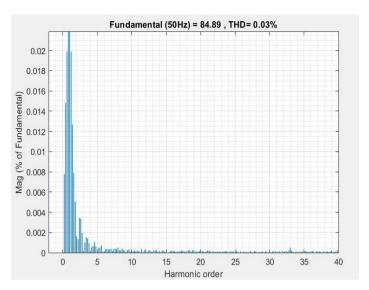

| Figure 6.4: The THD percentage for voltage                                               | 110   |

| Figure 6.5: The voltage and current at the load                                          | 110   |

| Figure 6.6: The THD percentage for voltage                                               | 111   |

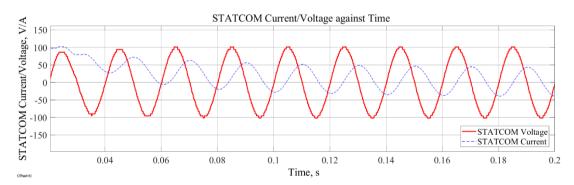

| Figure 6.7: The current and voltage waveform at STATCOM                                  | 111   |

## **List of Tables**

## Chapter 2

| Table 2.1: The comparison of total component counts                    |       |

|------------------------------------------------------------------------|-------|

| for five-level output                                                  | 17    |

| Table 2.2: The switching state for two-level inverter                  | 21    |

| Chapter 4                                                              |       |

| Table 4.1: List of components to build the prototype                   | 42    |

| Table 4.2: The electronic components used to build gate drivers        | 45    |

| Chapter 5                                                              |       |

| Table 5.1: The switching state for 9-level configuration               | 48    |

| Table 5.2: The parameters obtained from 9-level configuration          | 51    |

| Table 5.3: The mean current and voltage for every switch               | 52    |

| Table 5.4: The switching states for 13-level configuration             | 53    |

| Table 5.5: The parameters obtained from this 13-level configuration    | 57    |

| Table 5.6: The mean current and voltage for every switch               | 57    |

| Table 5.7: The switching states for 17-level configuration             | 58    |

| Table 5.8: The parameters obtained from this 17-level configuration    | 62    |

| Table 5.9: The mean current and voltage for every switch               | 62    |

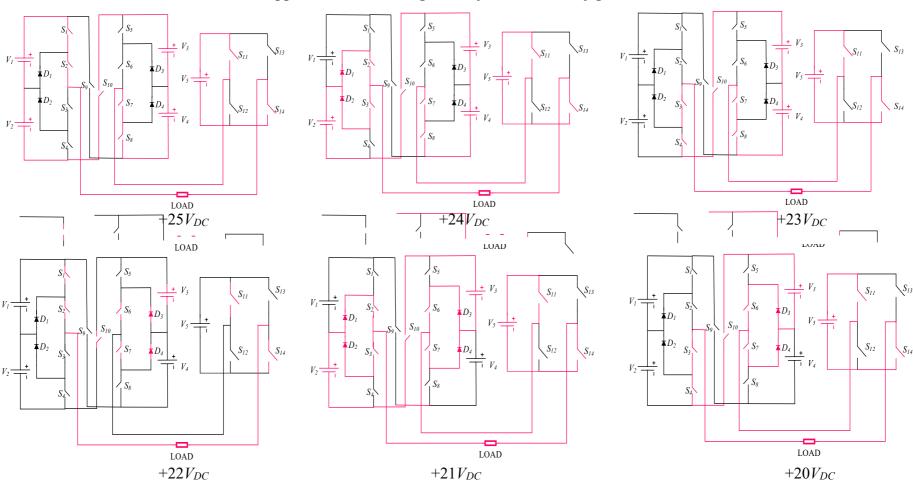

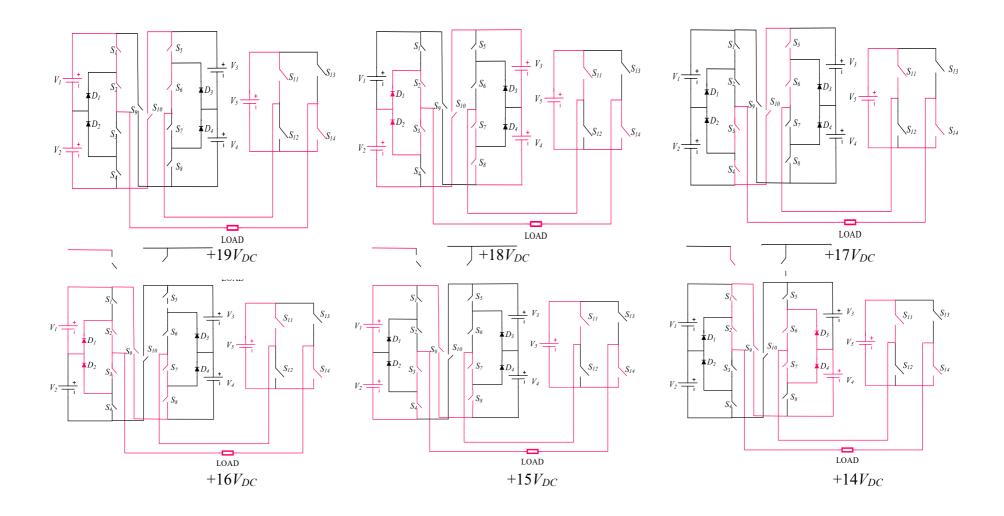

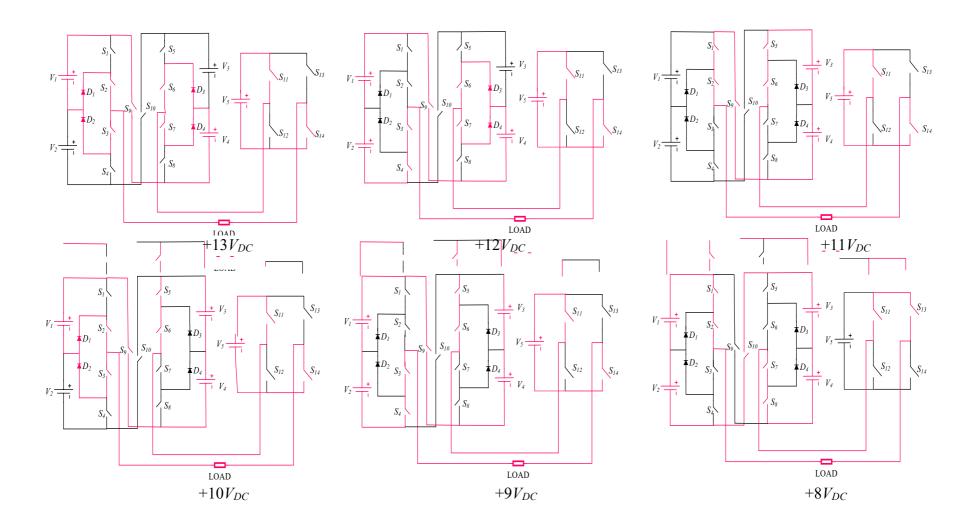

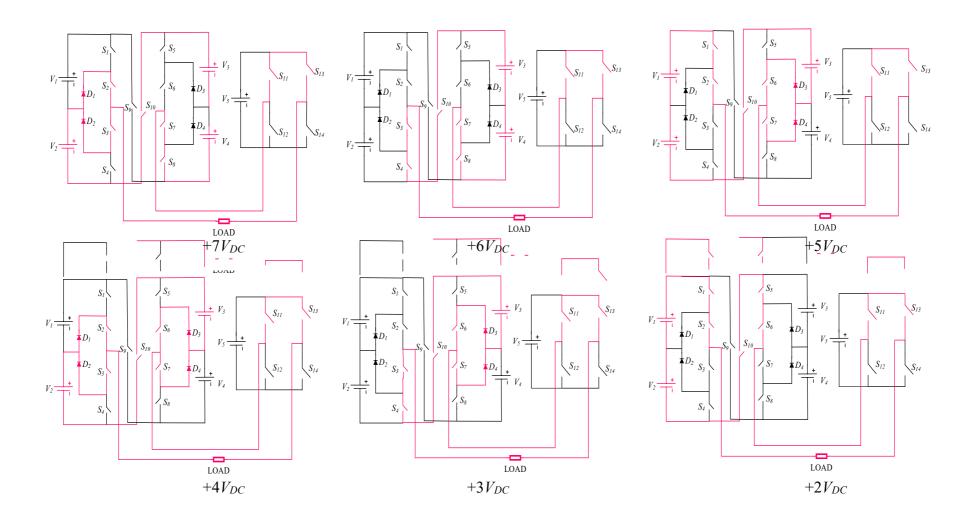

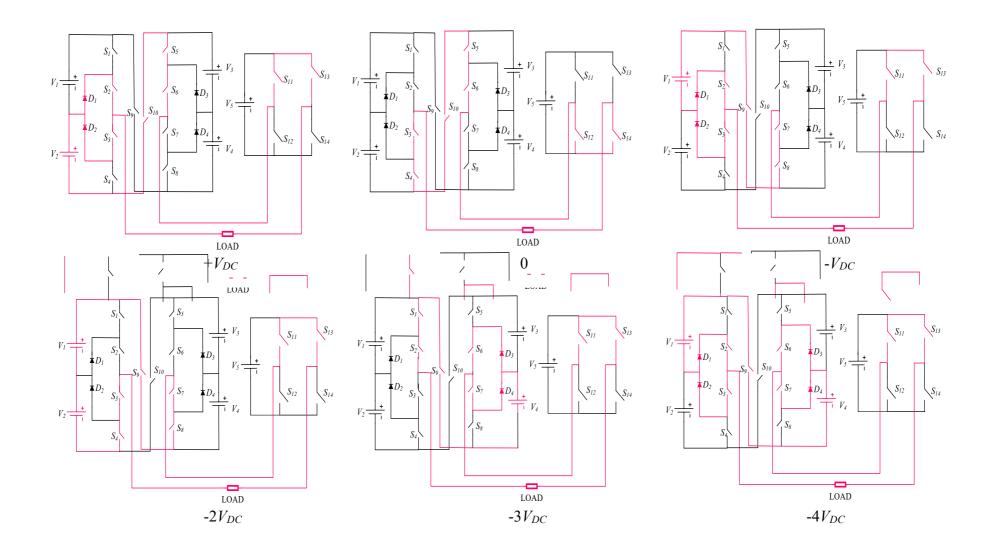

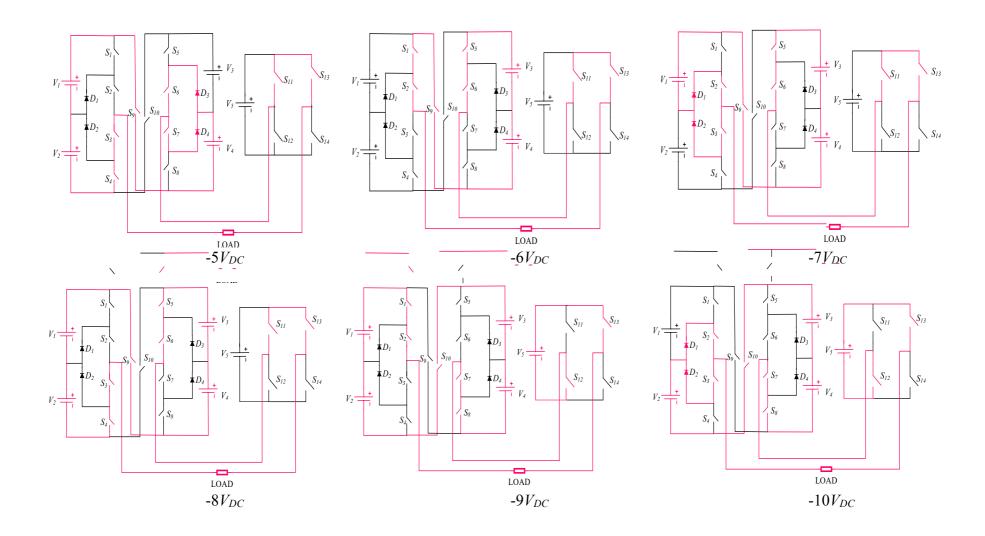

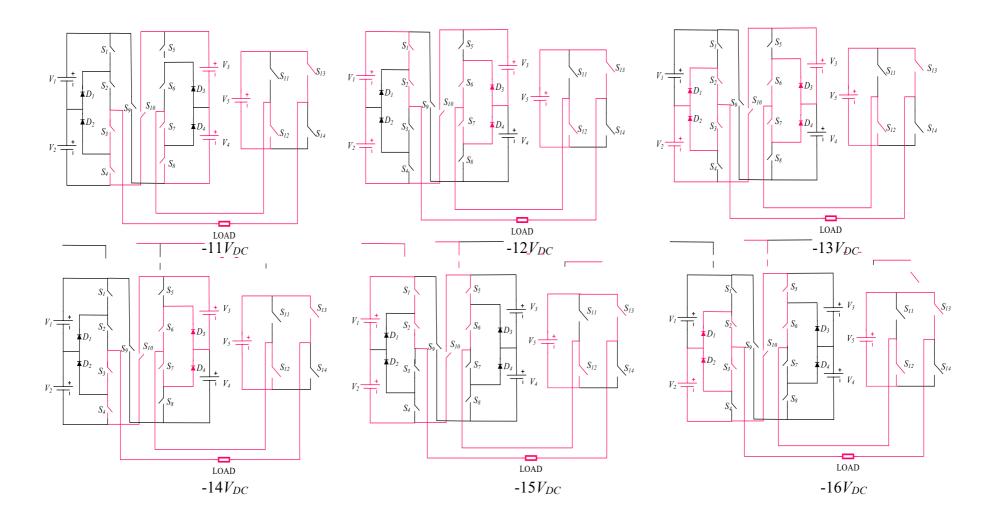

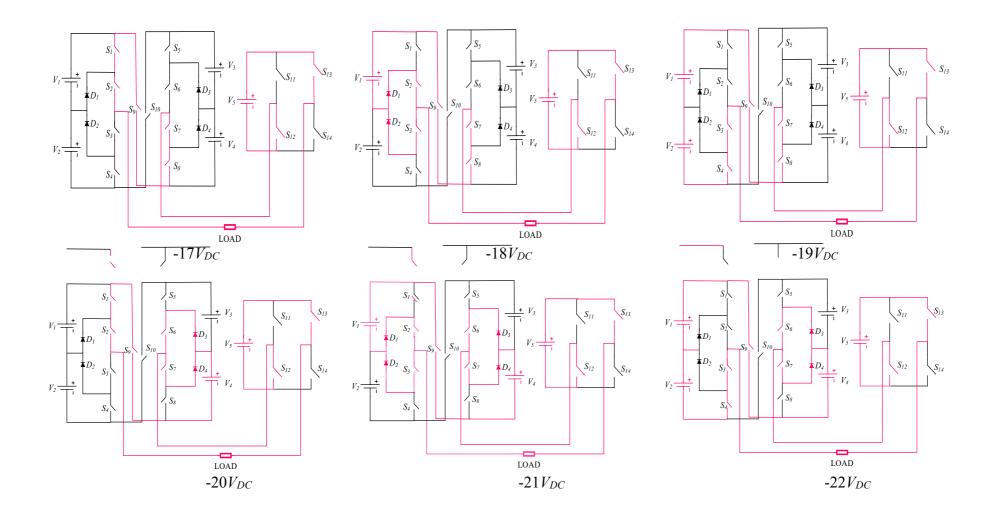

| Table 5.10: The switching states for 51-level configuration            | 63-64 |

| Table 5.11: The parameters from the 51-level configuration             | 68    |

| Table 5.12: The mean current and voltage for every switch              | 69    |

| Table 5.13: The comparison between simulation and experimental testing |       |

| for no-load condition                                                  | 73    |

| Table 5.14: The comparison between experimental testing and simulation   |     |

|--------------------------------------------------------------------------|-----|

| for loading condition                                                    | 75  |

| Table 5.15: The comparison between simulation and experimental testing   |     |

| for no-load condition                                                    | 79  |

| Table 5.16: The comparison between experimental testing and simulation   |     |

| for loading condition                                                    | 82  |

| Table 5.17: The comparison between simulation and experimental testing   |     |

| for no-load condition                                                    | 86  |

| Table 5.18: The comparison between experimental testing and simulation   |     |

| for loading condition                                                    | 89  |

| Table 5.19: The comparison between simulation and experimental testing   |     |

| for no-load condition.                                                   | 93  |

| 5Table 5.20: The comparison between experimental testing and             |     |

| simulation for loading condition                                         |     |

|                                                                          | 97  |

| Chapter 6                                                                |     |

| Table 6.1: The comparison between conventional MLIs and the proposed     |     |

| topology to produce 9-level of output voltage                            | 101 |

| Table 6.2: The comparison between conventional MLIs and the proposed     |     |

| topology to produce 13-level of output voltage                           | 101 |

| Table 6.3: The comparison between conventional MLIs and the proposed     |     |

| topology to produce 17-level of output voltage                           | 102 |

| Table 6.4: The comparison between conventional MLIs and the proposed     |     |

| topology to produce 51-level of output voltage                           | 102 |

| Table 6.5: Comparison between PT-9, (Mohapatra, et al., 2020), (Vineeth, |     |

| Mukundam, & Jayaprakash, 2021), and (Abdulhamed & Dr. A. H. Esuri,       |     |

| 2021)                                                                    | 105 |

| Table 6.6: Comparison between PT-17 and (Vineeth, Mukundam, &            |     |

| Jayaprakash, 2021)                                                       | 106 |

| Table 6.7: Comparison between PT-51, (Shankar, Edward, Kumar, &          |     |

| Raglend, 2017), (Hosseinzadeh, et al., 2019), and (Mondol, Biswas,       |     |

| Hosain, Samad, & Rahman, 2019)                                           | 107 |

| Table 6.8: The parameters used in the simulation                         | 109 |

### **Abbreviation List**

RES Renewable Energy Sources

GHG Green House Gas

AC Alternating Current

DC Direct Current

MLI Multilevel Inverter

CHB-MLI Cascaded H-Bridge Multilevel Inverter

DC-MLI Diode Clamped Multilevel Inverter

FC-MLI Flying Capacitor Multilevel Inverter

CCS-MLI Cross Connected Sources Based Multilevel Inverter

SV-PWM Space Vector Pulse Width Modulation

CB-PWM Carrier Based Pulse Width Modulation

SHE Selective Harmonic Elimination

THD Total Harmonic Distortion

$V_{DC}/E$  Source Voltage

PV Photovoltaic

*n* Number of levels

$V_{ref}/V_{REF}$  Reference voltage

V<sub>C</sub> Carrier Signal

*f* frequency

Fref Reference Voltage

*m* Modulation index

NLC Nearest Level Control

PF Power factor

VSC Voltage Sourced Converter

V<sub>C</sub> STATCOM voltage

$V_S$  System voltage

i Current L Inductor R Reactor

PCC Point of Common Coupling

DSP Digital Signal Processor

PCB Printed Circuit Board

V<sub>FND</sub> Fundamental voltage

$V_{RMS}$  RMS voltage

$V_{PH-PH}$  Phase to phase voltage

### **Chapter 1: Introduction**

Electrical energy has become the driving force for today's civilization and development. Generally, electrical energy is generated from (i) non-renewable sources (Non-RES) like fossil fuels, biomass, and nuclear energy; and (ii) renewable energy sources (RES) like solar, wind, geothermal and hydro. As the population growth and the demands escalated year by year, more power plants are built to cater to energy needs.

As the name suggested Non-RES are unsustainable, depleted in the long run, and believed to cause climate change. The increase in carbon footprint from the burning of hydrocarbon is one of the contributors to the increase in greenhouse gasses (GHG). The trapped GHG in the atmosphere results in climate change, specifically global warming that melts the ice caps in the arctic, increases the sea level, causes forest fires, as well as contributes to catastrophic and unpredictable weather change ("The Effect of Climate Change", 2021). It also cripples human health and economic growth making global warming no longer something that can be taken for granted. Hence, shifting to RES needs to be done promptly so that the environmental damage could be controlled, or at least be minimized.

Unlike Non-RES, RES is sustainable, clean, and not harmful to humans and the environment. Malaysia is a tropical country blessed with abundant RES, especially solar and hydro. According to (Sivaprasaad & Kumbhare, 2021, para. 9), RES is 18% of Malaysia's energy mix, with 86% of the capacity being dominated by hydropower. Unfortunately, the use of RES is still limited and less developed. A lot of studies need to be done to ensure RES deployment is a worthy investment for alternative energy sources.

Hence, to ensure RES is not an economic burden, it needs to be equipped with components that can fully utilize its potential. The inverter is one of the core components of RES power generation. It converts the direct current (DC) to alternating current (AC) so that it is usable to consumers. In addition, the output AC shall be as close as a sinusoidal waveform (i.e., ideal AC waveform) to produce a low harmonic or high power quality. A high harmonic AC reduces the system performance by increasing the power loss.

Before multilevel inverter (MLI) was introduced, a two-level inverter was used together with a step-up transformer and an output filter. The step-up transformer was required to step up the output to a suitable AC magnitude, while the filter was to filter harmonic. This design results in a bulkier system that is not preferable for medium to high voltage applications. On the other hand, MLI can produce a waveform greater than the two-level inverter and closer to a sinusoidal waveform. In addition, MLI also does not require a step-up transformer and output filter, which makes the system compact.

The first introduced MLI was Cascaded H-Bridge (CHB)-MLI, traced back to 1970 (Alishah, Nazarpour, Hosseini, & Sabahi, 2014). It produced higher output levels compared to a single H-Bridge that can only generate three output levels. It was followed by Diode Clamped (DC)-MLI which was introduced in 1980 and Flying Capacitor (FC)-MLI in 1990. These three early MLIs are grouped as 'conventional MLIs'. Conventional MLIs has gained instant fame and are widely used in low to high power application, including RES generation (Siddique, et al., 2020). However, researchers are still actively improving the conventional MLIs in the hope to extract a pure sinusoidal AC waveform.

## 1.1 Building Justification

#### 1.1.1 The Research Field

Cross-connected sources based (CCS)-MLI is a type of recently established MLI that has some resemblance with CHB-MLI. As compared to CHB-MLI, CCS-MLI uses fewer components to produce the same level of output. Hence, the size of the CCS-MLI is smaller and the production cost is expected to be smaller. This study will propose a new topology that utilized the benefits of CHB-MLI, DC-MLI, and CCS-MLI. A simple mathematical equation will also introduce to predetermine the total level of output voltage. This figure will be referred to determine the switching sequence and the appropriate magnitude for DC sources.

MLI configurations that are commonly used are symmetrical configuration, asymmetrical configuration, and hybrid configuration. The symmetrical configuration uses similar DC sources whereas the asymmetrical configuration utilizes unequal DC sources. Meanwhile, the hybrid configuration is the combination of several MLI topologies. Using these configurations can help the proposed topology yield different levels of output voltage. In addition, asymmetrical and hybrid configurations can

increase the level of output voltage without increasing the number of components used (Gupta & Jain, 2014).

The modulation technique is a method used to synthesize AC waveform from the DC supply. The modulation techniques that are commonly used are carrier-based pulse width modulation (CB-PWM), space vector pulse width modulation (SV-PWM), selective harmonic elimination (SHE), and nearest level control. As modulation techniques could affect the quality of the synthesized outputs, the techniques that give the best quality of output will be chosen.

## 1.1.2 The Research Gaps

Component counts are one of the major concerns in building MLI as they can affect size, complexity, system losses, and production cost. Continuous studies have been done and over the years, a lot of MLI with a reduced number of components have been introduced. Most of the presented topologies are made up of fundamental units that can be cascaded to yield a higher level of output voltage and separated parts for level generation and polarity. Despite their ability to produce a higher level of output voltage and eliminates the need for a transformer, the number of components used is still considerably high. On the contrary, unidentical DC sources (i.e., asymmetrical configuration) and hybrid configuration can be utilized to increase the level of output voltage without drastically increasing the component counts.

Harmonic problem is also a challenge in building MLI. Since MLI is widely used for non-linear loads, harmonics is unavoidable. However, like other power quality issues, failure to compensate harmonics can severely affect the whole system. Therefore, it is important to keep the total harmonic distortion (THD) percentage within the limit stipulated by IEEE standards. Theoretically, the higher the level of output voltage, the lower the THD percentage. However, not all MLI can keep the THD percentage within the stipulated standard. Hence, it may require an output filter for power quality enhancements which will add to the system size.

Modulation techniques that are commonly used to synthesize MLI output included CB-PWM, SV-PWM, SHE, and nearest-level control. These techniques can affect the synthesized output positively and negatively. Some can help to improve the quality of the synthesized output (Jani & Kapil, 2016) and solve voltage imbalance problems (Kang, Lee, Jeon, Kim, & Hyun, 2005) but some may have a difficult computation, high voltage drops, and high power loss at the switching devices.

### 1.1.3 Research Questions

The research questions are listed as follows:

- i. Does the proposed topology able to address the limitations of the conventional MLI in terms of the number of components and the total number of voltage output levels?

- ii. Does the proposed topology able to produce a THD percentage less than 5% for the application below 69 kV?

- iii. Does the proposed topology capable to be hybridized to produce a higher voltage output level without significantly increasing the number of components used?

## 1.2 Objectives

This study aims to develop a new MLI topology with better efficiency as compared to the existing MLI. The proposed topology is expected to have lower component counts for the sake of compact and simple design. It is also expected to produce a high level of output voltage to achieve an ideal AC waveform.

The specific objectives of this research study are outlined as follows:

- 1. To design and develop a new single-phase MLI topology based on DC-MLI and CCS-MLI with symmetrical, asymmetrical, and hybrid.

- 2. To discuss the results obtained from the testing in terms of total component counts, THD percentage, and total level of output voltage.

- 3. To perform a comparative study between the proposed topology and the conventional MLI as well as the MLI proposed recently by other researchers.

## 1.3 Outcome and Significance

The outcomes of this research work are as follows:

- i. A new topology that utilizes the benefit of DC-MLI is proposed. As explained in the literature review, DC-MLI is the least explored MLI as compared to its other two counterparts though it gained fame in industrial. Thus, through this study, the disadvantages of DC-MLI will be improved.

- ii. As this topology produces a high number of voltage output levels, the THD percentage is low or within the allowable limit set by the IEEE standard.Thus, there is no need for an output filter or transformer.

Then, the significance of this research is listed as follows:

- i. The proposed topology will improve the power quality thus resulting in a remarkable increase in the reliability of the MLI.

- ii. As the proposed topology uses fewer components, the MLI size will be more compact and simpler.

- iii. Compared to CHB-MLI and FC-MLI, DC-MLI is the least developed despite its advantages. The proposed topology will maximize the benefits of DC-MLI and open the path for further exploration in DC-MLI.

- iv. This study also can contribute to the study of RES in Malaysia's electricity generation as a part of the effort in reducing carbon footprint.

#### 1.4 Ethical Issue

This research does not involve any ethical issues.

### 1.5 Facilities and Resources

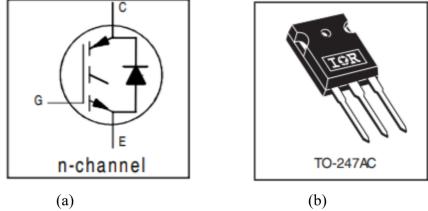

The materials for this project will include the IGBT transistor (or MOSFET) module, diodes, resistive, capacitive, and inductive load, protection elements, electrical measuring instruments, oscilloscope, real-time interface board, and real-time digital signal processing unit. The power rating of electrical and electronic components is subject to the operating power. This prototype will undergo several experimental testings.

The experiment, testing, and troubleshooting will be done in the electrical engineering laboratory of Curtin University Malaysia. The equipment that might be needed includes DC-power supplies, voltage, and current probes, oscilloscopes, digital multimeters, and micro-box controller. The equipment is readily available in Curtin Malaysia.

## 1.6 Data Storage

The research data that is being collected will be kept in the Network drive of Curtin Malaysia and will be retained in compliance with the Curtin Data Management Plan and the Western Australian University Sector Disposal Authority with a minimum storage of five years after the thesis is published.

### 1.7 Thesis Outline

This thesis is organized into 7 chapters:

- 1. Chapter 1 (Introduction) lists the problem statements, objectives, and the novelty of the study.

- 2. Chapter 2 (Literature Review on MLI, Modulation Techniques, and STATCOM) presents a brief background and the recent studies related to the topics.

- 3. Chapter 3 (Research Methodology) presents the research methodology in detail, including software and measuring instruments that were being used.

- 4. Chapter 4 (The Proposed Topology & Hardware Implementation) presents the proposed topology and the proposed topology prototype.

- 5. Chapter 5 (Simulation and Experimental Result Analysis) analyses the results obtained from simulation and experimental testing.

- 6. Chapter 6 (Comparative Analysis & STATCOM) presents the comparative study between the proposed topology with the conventional MLI and the topology proposed in the last 10 years. It also presents the proposed topology implementation in STATCOM.

- 7. Chapter 7 concludes the study and suggests a few recommendations that can be done in the future.

### Chapter 2:

## Literature Review on Multilevel Inverter & Modulation Techniques

## 2.1 Chapter Introduction

This chapter gives a general knowledge of multilevel inverter (MLI), modulation techniques, and STATCOM. The inverter or MLI is used to convert DC input to AC output that is useable and the consumer side. The conventional MLIs are CHB-MLI, DC-MLI, and FC-MLI. Meanwhile, modulation techniques are methods used by the inverter to synthesize the AC output and STATCOM is an example of MLI application in the industry.

#### 2.2 Inverter Overview

The ideal AC output is a smooth sinusoidal waveform. However, the MLI produces a staircase-like waveform. The ideal AC output is achievable by increasing the number of the staircase which subsequently will increase the THD percentage. Nevertheless, increasing the staircase may also increase the number of components used in building the MLI. This results in a bulkier, more complex, and more expensive MLI. Therefore, this study is conducted to propose an MLI topology that generates a high level of output voltage (i.e., the staircases) with a reduced number of components.

### 2.2.1 The Two-level Inverter

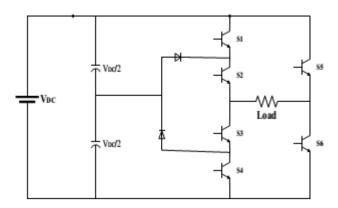

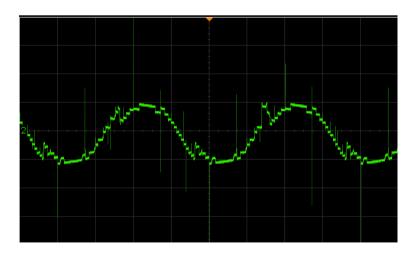

In the early years, a three-phase two-level inverter was used to produce an AC output. The general structure of this inverter is shown in Figure 2.1. This inverter produced a three-level of outputs, which are  $-V_{DC}$ , 0, and  $+V_{DC}$ . The output voltage was represented by a quasi-square waveform.

A quasi-square waveform is far from the ideal AC waveform, namely the sinusoidal waveform. High-frequency switching was introduced to smoothen the output waveform. However, this produces undesirable effects like high switching losses, high dv/dt, voltage doubling effect, and electromagnetic interference. In addition, the two-level inverter requires a step-up transformer and an output filter for grid integration to achieve the desired output voltage level and a better output (Blaabjerg, Chen, & Kjaer, 2004).

Figure 2.1: The three-phase two-level inverter

On the other hand, MLI produces a higher level of output voltage than the two-level inverter thanks to the increasing number of switches to share voltage stress. This results in the output waveform that is closer to the ideal waveform. The higher level of output voltage also increases the output quality. As a result, the step-up transformer and the output filter can be eliminated, and the switching frequency can be reduced to avoid severe electromagnetic interference to the system (Blaabjerg, Chen, & Kjaer, 2004; Welter, 1999).

The MLI gained instant fame especially in medium to high-voltage applications. High voltage applications might still need the transformer, but the size of this transformer is smaller than in the two-level inverter. Thus, the system is referred to as a 'transformerless' system (Agrawal & Jain, 2017).

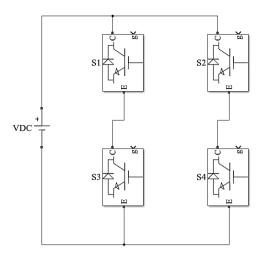

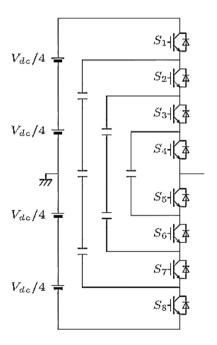

## **2.2.2** CHB-MLI

CHB-MLI is a term given to the MLI structure with several H-MLI cascaded. Each H-MLI consists of a DC source and 4 switches (Matsumoto, Shibako, & Neba, 2016). The configuration is shown in Figure 2.2. The switches are divided into two parallel legs: the left leg ( $S_I$  and  $S_3$ ) and the right leg ( $S_2$  and  $S_4$ ). These series-connected switches are operating in a complementary manner in every switching cycle. Hence, an H-MLI can produce three-level of output voltage; - $V_{DC}$ , 0, and + $V_{DC}$ .

Figure 2.2: H-MLI configuration

The total level of the output voltage can be increased by cascading more H-MLI or by using unequal DC sources. The latter method is known as asymmetrical configuration. The commonly used DC sources ratio is binary (1:2) and trinary (1:3) (Raj, Dash, Dhatrak, & Nema, 2015). Asymmetrical configuration helps the MLI to achieve a higher level of output voltage without increasing the number of components used. For example, the trinary-CHB-MLI used lesser components than the binary and symmetrical configured CHB-MLI (Mohapatra, et al., 2020; Patel & Sood, 2020). Even so, not all topologies can support trinary configuration as some of the output voltage levels may be 'skipped' when synthesizing the output (Raj, Dash, Dhatrak, & Nema, 2015).

(Davis & Dey, 2016; Du, Tolbert, Ozpineci, & N.Chiasson, 2009) had suggested several examples of hybrid CHB-MLI. (Davis & Dey, 2016) suggested a hybrid of FC-MLI and CHB-MLI where FC-MLI helped in reducing the number of isolated DC sources. In return, CHB-MLI helped in mitigating the voltage imbalance in FC-MLI. However, this topology does not reduce the number of components used.

Isolated DC sources would not be an issue if the DC sources are abundant, for example in solar PV applications. The DC source can be represented by a PV module or a string of a PV module. The string is equipped with a dc-link capacitor. However, this application needs a dc-link capacitor control (Noman, Al-Sharmma'a, Addoweesh, Alabuljabbar, & Alolah, 2017). Hence, in the case where DC sources are limited, CHB-MLI will become less practical.

Numbers of MLI topologies have been proposed based on CHB-MLI topology for its output stability purpose, modularity, and cascading features (Abdulhamed, Esuri,

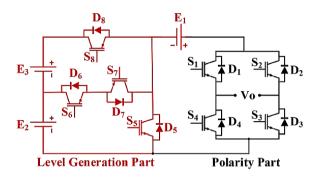

& Abodhir, 2021; Babaei, Laali, & Bayat, 2015; Nanda, et al., 2022; Muhammad, et al., 2017; Ponkumar, Rivera, & Kumar, 2017; Samsami, Taheru, & Samanbakhsh, 2017; S, Peddapati, & Naresh, 2020; Vineeth, Mukundam, & Jayaprakash, 2021). Generally, all these topologies consist of two parts: (i) the level generation part and (ii) the polarity part, as shown in Figure 2.3. A unit of H-MLI is normally used for the polarity part.

Figure 2.3: The basic suggested MLI unit for topology presented in (Samsami, Taheru, & Samanbakhsh, 2017)

As the name suggested, the level generation part generates the desired level of output voltage with a positive magnitude. Meanwhile, the polarity of the outputs is determined by the polarity part. Most of the presented topologies have a 'fundamental unit' that can be cascaded to yield a higher level of output voltage. Although these fundamental units have a reduced the number of components, the figure is still skyrocketed as the desired output level increase (Abdoli, Khorsandi, Ekandari, & Moghani, 2020; Babaei, Laali, & Bayat, 2015; Muhammad, et al., 2017; Ponkumar, Rivera, & Kumar, 2017; Samsami, Taheru, & Samanbakhsh, 2017).

Nevertheless, there is also topology with fixed designs for the level generation part like in (Nanda, et al., 2022; K., Pedapati, & Naresh, 2020; Vineeth, Mukundam, & Jayaprakash, 2021). These topologies normally have fixed levels of output voltage that they can achieve and are impractical to be cascaded. However, the level of output voltage can be increased by introducing asymmetrical configurations like in (Vineeth, Mukundam, & Jayaprakash, 2021).

(Barah & Bahera, 2021) has introduced a sub-multilevel structure that was derived from CHB-MLI. It consists of one DC source and two switches. The sub-multilevel structures need to be cascaded to achieve the desired level of output voltage.

This topology used lesser components than conventional CHB-MLI to produce the same level of output voltage.

### 2.2.3 FC-MLI

One of the disadvantages of using CHB-MLI is it requires multiple isolated DC sources to synthesize the output voltage level. As the level increases, the number of required DC sources will also increase. This increases the number of components and the complexity of the topology. Therefore, FC-MLI and DC-MLI are used to replace CHB-MLI when the availability of the DC sources is a concern. FC-MLI and DC-MLI used capacitors and diodes to maintain the voltage at presided voltage levels. In other words, they can use a single DC source and generate multiple output voltage levels by clamping the voltage.

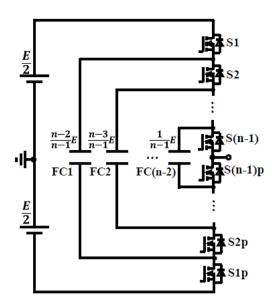

Figure 2.4: Five-level capacitor clamped converter (Fujita, 2012)

Figure 2.4 shows a typical five-level capacitor clamped inverter (Fujita, 2012). This converter can produce five-level of output voltage. Meanwhile, Figure 2.5 shows n-level FC-MLI. The numbers of power switches in the upper and lower half of the system are donated by (n-1), respectively. The (n-2) FC holds voltages that are varied by E/(n-1). The output voltage level is generated by combining the capacitor voltages and the source voltages which is by manipulating the switching state of the 2(n-1) power devices (Mochidate, Matsuo, Obara, & Sato, 2016).

Figure 2.5: Circuit configuration per phase for n-level FC-MLI (Mochidate, Matsuo, Obara, & Sato, 2016)

As reported in (Amini & Abedini, 2013; Rohner, Bernet, Hiller, & Sommer, 2010), FC-MLI addresses DC-MLI and CHB-MLI limitations. Its design has eliminated the requirement for isolated DC sources and clamping diodes. Plus, it does not need a snubber circuit to function and has the very least loss among the three conventional MLIs. Furthermore, the presence of a large number of capacitors provides extra ride-through capability during system imperils (Amini, Viki, Radan, & Moallem, 2016).

However, the presence of capacitors will significantly increase the size of the system as the desired level of output voltage increases. This results in a bulkier and more complex topology. In addition, it is demanding to maintain the voltage of floating capacitors at the appropriate level. Due to these undesirable conditions, FC-MLI becomes less attractive in the power industry despite its admirable improvement (Amini, Viki, Radan, & Moallem, 2016; Ohmer, Kumar, & Surjan, 2020).

(Huang & Corzine, 2006) introduced a prototype of a three-cell inverter to minimize the component counts. This prototype used a redundant switching state to generate more voltage steps by a definite number of components. The prototype had successfully reduced the THD percentage and the switching loss, but the conduction losses were fairly constant. Despite the noticeable merits, this method is less attractive due to its complex control scheme.

Meanwhile in 2020, (Chen, Fong, & Loh, 2020) cascaded two FC-cells are being cascaded to build a novel five-level inverter for PV systems. This topology reduced the total number of capacitors used, discard the use of the high voltage-rating capacitor, and provide a solution for voltage imbalance. It has significantly reduced the number of components, but the application is limited to five-level of output.

The voltage imbalance problem in FC-MLI is due to the difficulty in fixing the capacitor voltage at the appropriate level (Muhammad, et al., 2017). This problem can be solved by (i) the open-loop control, and (ii) the closed-loop control (Amini, Viki, Radan, & Moallem, 2016).

(Feng, Liang, & Agelidis, 2007; Kang, Lee, Jeon, Kim, & Hyun, 2005) introduced a few examples of open-loop control. This method is said to be simpler than the closed-loop control but it has a poor dynamic response in transients and a high inductive load (Rohner, Bernet, Hiller, & Sommer, 2010). In order to improve the dynamic response, requires additional components that will subsequently increase the cost and the power loss. Moreover, all the power devices are required to have the same characteristics as the switching cells operating at a similar duty cycle. Since this ideal condition is hard to compromise, the open-loop method is hopeless when using unequal DC sources (Beig, Kumar, & Ranganathan, 2004).

The control scheme that was presented in (Choi & Saeedifard, 2012; Defay, Llor, & Fadel, 2010; Khazraei, Sepahvand, Corzine, & Ferdowsi, 2012) for the closed-loop control method provides better performance than the open-loop method. However, the operation becomes more complex and tangled when the system is expanded to a higher level. The complicated algorithm and look-up table also may be necessary for this method. (Amini, Viki, Radan, & Moallem, 2016) has proposed a reliable solution for this problem but the method is still complicated.

(Mochidate, Matsuo, Obara, & Sato, 2016) stated that the FC-MLI performance can be improved by manipulating the modulation technique. For such, voltage ripple can be mitigated by introducing a high switching frequency. In addition, FC-MLI is not only restricted to power industry use. (Modeer, et al., 2017) suggested FC-MLI's active involvement in the aircraft industry. A new design of FC-MLI with a low inductance layout has been proposed to increase the performance of FC-MLI in the aircraft industry.

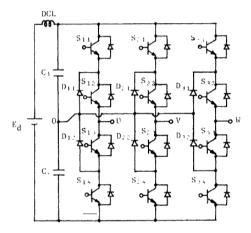

## 2.2.4 DC-MLI

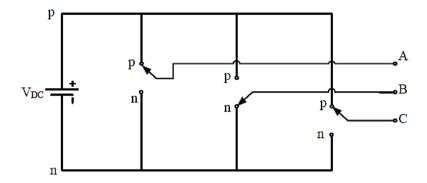

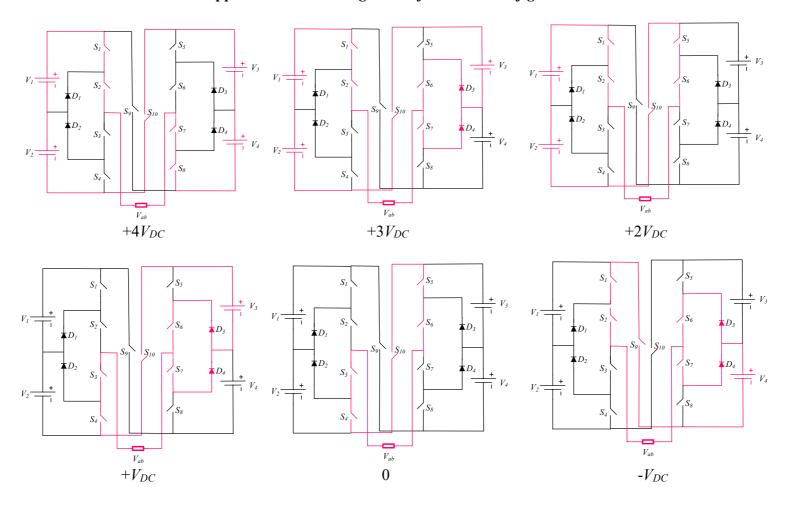

DC-MLI or also known as neutral point clamped (NPC)-MLI was first introduced in 1981 (Nabae, Takhashi, & Akagi, 1981). The structure of DC-MLI is inspired by the classical two-level inverter with the addition of a pair of semiconductors (Franquello, et al., 2008). The basic structure for the three-phase three-level DC-MLI is shown in Figure 2.6.

A pair of diodes is located in between the two switches. When the diode is reverse biased, the reverse bias voltage clamps the source voltage to generate the output voltage level. The diodes share the voltage stress with the switches when are in series with the applied voltage (Bhattacharya, Saha, Khan, & Nag, 2017; Boussada, Elbeji, & Benhamed, 2017).

Figure 2.6: The presented topology in (Franquello, et al., 2008)

The perk of using DC-MLI is the voltage sources sharing among the existing phases. This eliminates the need for additional voltage sources. As the result, the topology is practical to be used in high voltage applications (HVA) and the capacitors also can be pre-charged as a group (Boussada, Elbeji, & Benhamed, 2017). In (Dave & Bhagdev, 2016), a comparison has been made between the CHB-MLI topologies presented in (Beig, Kumar, & Ranganathan, 2004; Cui, Ge, Zhou, & Yang, 2017; Kang, Park, Cho, & Cheul U-Kim, 2005; Valderrama-Blavi, M.Munoz-Ramirez, J.Maixe, & Calvente, 2005) with the DC-MLI. In their papers, the authors believed that voltage source sharing mitigates the need for cabling and power losses at the input side. This can improve the reliability of the system.

However, DC-MLI is far from perfect. Among the three conventional MLIs, DC-MLI uses the greatest number of components. The figure skyrocket as the desired

output level increases. This results in design, conduction, and switching losses. In addition, the voltage balancing problem might occur in a higher level DC-MLI (Wang, Kou, Liu, & Sen, 2017). Despite the superiority of common DC sources, DC-MLI is not feasible as the desired level of output voltage increases (Ohmer, Kumar, & Surjan, 2020).

(Cui, Ge, Zhou, & Yang, 2017) suggested several methods for voltage balancing. (Cui, Ge, Zhou, & Yang, 2017) classified the method into three types: using improved SV-PWM, using modified CB-PWM, and adding a voltage balance circuit. It can be concluded that the balance voltage can be achieved by modifying the modulation techniques that are used in the presented topologies (Lange & Piepenbreier, 2017; Li, et al., 2017; Tamasas, Saleh, Shaker, & Hammoda, 2017).

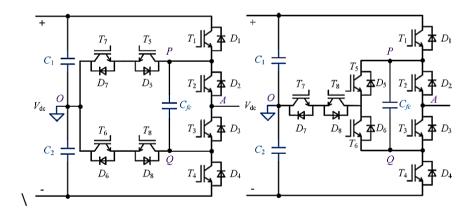

(Valderrama-Blavi, M.Munoz-Ramirez, J.Maixe, & Calvente, 2005) presented two DC-MLI topologies with a fewer number of components. The configuration is shown in Figure 2.7. The DC-MLI was coupled with FC-MLI to increase modularity and increase the level of output voltage. It is also believed to improve the voltage balance at the DC-link capacitor. Nevertheless, there is no significant improvement in the number of components and complexity.

Figure 2.7: (Left) The type 1 and (Right) type 2

Examples of DC-MLI with a reduced number of components are suggested in (Zolfaghar, Najafi, & Hasanzadeh, 2018), (Goopta, Dhar, & Bhattacharya, 2020) and (Jacobo-Palmer, Garridor, Escobedo-Trujillo, & Revuelta-Acosta, 2021).

Topology presented in (Zolfaghar, Najafi, & Hasanzadeh, 2018) attached a unit H-MLI to the upper and the lower switch of DC-MLI as shown in Figure 2.8. The H-Bridge acted as a polarity changer. Since the presented topology is modular, it can be extended to yield a higher level of output voltage.

Figure 2.8: Topology presented in (Zolfaghar, Najafi, & Hasanzadeh, 2018)

Topology in (Goopta, Dhar, & Bhattacharya, 2020) is divided into 2 portions; the upper portion is used for the positive level generation, and the lower portion for the negative level generation. Although it is proven to reduce the components, it may have a problem with voltage imbalance due to the DC-link capacitor.

Meanwhile, (Jacobo-Palmer, Garridor, Escobedo-Trujillo, & Revuelta-Acosta, 2021) used feedback diodes to reduce the number of components. The feedback diodes return the stored energy from the inductive loads to the sources instead of the switching gate. The drawback of this topology is the high number of isolated DC sources and the lack of flexibility.

## 2.2.5 **CCS-MLI**

Years later, (Gupta & Jain, 2014) presented CCS-MLI, a novel topology with reduced components. The name is given likewise due to the presence of floating input DC sources that connect the higher potential terminal of the preceding source to the lower potential of the succeeding sources. CCS-MLI had successfully addressed the disadvantage of conventional MLIs in terms of component counts. The topology also has a simple design (Gupta & Jain, 2014).

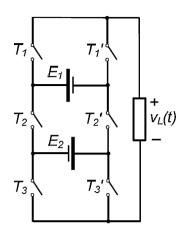

The CCS-MLI topology is illustrated in Figure 2.9. This topology produces five-level of output voltage which are, +2E, +E, 0, -E, and -2E. Similar to the H-bridge cell; the switches in each cell operate in a complementary manner to avoid short-circuit. Plus, the CCS-MLI structure also closely resembles CHB-MLI. They do not require any clamping devices and they can be cascaded to achieve a higher level of output voltage.

Figure 2.9: A five-level CCS-MLI as being presented in (Gupta & Jain, 2014)

CCS-MLI used fewer components than the other conventional MLIs. The comparison between the components used to produce a 5-level of output voltage between CCS-MLI and conventional MLIs is tabulated in Table 2.1. The number of components can be further reduced with the use of unequal DC sources or simply an asymmetrical configuration. However, using the asymmetrical configuration will eliminate the modularity of CCS-MLI. In this case, it is demanding to cascade. On the contrary, a symmetrical configuration can retain the modularity but the number of components will soar (Kangarlu, Babaei, & Sabahi, 2013).

Table 2.1: The comparison of total component counts for five-level output

| Type of MLI Components  | DC-MLI | FC-MLI | CHB-MLI | CCS-MLI |

|-------------------------|--------|--------|---------|---------|

| No. of switches         | 24     | 24     | 24      | 18      |

| No. of clamping diodes  | 16     | 0      | 0       | 0       |

| No. of DC sources       | 4      | 4      | 6       | 6       |

| No. of flying capacitor | 0      | 18     | 0       | 0       |

| Total component counts  | 88     | 70     | 54      | 42      |

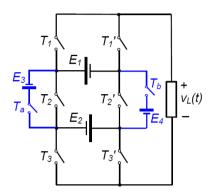

(Dewangan, Gurjar, Ullah, & Zafar, 2014) has suggested a way to improvise CCS-MLI by adding the additional switches known as the bidirectional-conducting-unidirectional blocking (BCUB) and the bidirectional-conducting-bidirectional-blocking (BCBB). The configuration is shown in Figure 2.10. This topology is known as Level Doubling Network (LDN). It produced a 12-level of output voltage with less number of components than a standard CCS-MLI and the conventional MLIs.

However, this topology failed to reduce the number of DC sources. Plus, as the level increase, the link network will increase the complexity of the circuit.

Figure 2.10: The proposed CCS-MLI in (Dewangan, Gurjar, Ullah, & Zafar, 2014)

Meanwhile, a new topology called Packed U-Cell (PUC) was also introduced in (Ounejjar, Al-Haddad, & Gregoire, 2011). This topology consists of DC sources and flying capacitors. It is said to be successfully reduced the number of components. PUC has almost a similar structure as CCS-MLI apart from the capacitors. Although PUC is a good candidate to reduce the component counts, its undesirable features like lack of modularity, disability to produce the summation of DC link voltage, difficulty to maintain the DC capacitors voltage as well as the high switch rating had significantly reduced the competency of PUC.

To improve the reliability of PUC, two crossed switches were added for DC input summation (Kangarlu, Babaei, & Sabahi, 2013). (Babadi, Salari, Mojibian, & Bina, 2017) suggested a topology that utilizes asymmetrical configuration and cascading features. This topology is said to be capable to address the limitations of PUC in (Ounejjar, Al-Haddad, & Gregoire, 2011). As compared to PUC, CCS-MLI is somehow more attractive as it has a simpler structure and a straightforward operation. A complex topology will be less attractive as it will indirectly increase the size and complexity of the inverter.

## 2.3 Modulation Techniques

Modulation techniques are methods used to synthesize the AC output from the DC input. Examples of modulation techniques that are commonly used are CB-PWM, SV-PWM, SHE, and Nearest Control Method. It is important to choose an appropriate modulation technique as it may affect the quality of the output.

### 2.3.1 **CB-PWM**

Generally, the gating signals of CB-PWM are generated by comparing the sinusoidal reference signal,  $V_{ref}$  with the carrier signal,  $V_c$ . The output frequency and the amplitude are given by the reference frequency,  $F_{ref}$ , and the modulation index, m. There are three categories of modulation: (i) ideal modulation where m = 1, (ii) overmodulation where m > 1, and (iii) undermodulation where m < 1. Overmodulation can help to boost the output voltage. However, this method is rarely used due to the presence of low-order harmonics. Meanwhile, undermodulation can deteriorate the reliability of the system.

In general, an MLI with n-levels of output requires  $(n-1)V_c$ . The PWM can be generated either using analog control or digital control. However, digital control provides better stability, noise immunity, and flexibility.

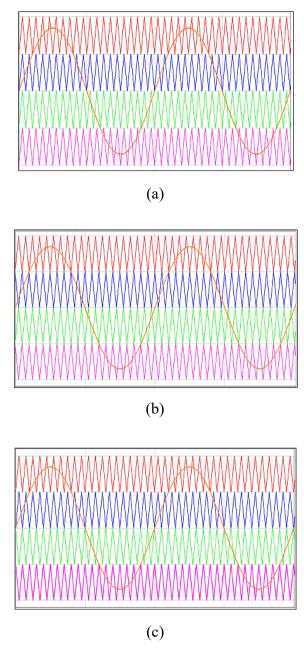

CB-PWM can be further divided into phase-shifted modulation and level-shifted modulation. As for the phase-shifted modulation,  $V_c$  and  $V_{ref}$  have similar frequencies and peak-to-peak amplitude. The level-shifted modulation shared a similar trait. However, in phase-shifted modulation, a phase shift between any two adjacent  $V_c$  by  $\varphi_{cr} = 360^{\circ}/(m-1)$  is required to determine the gating pulse.

In level-shifted modulation, carrier signals are vertically disposed of such that the bands that they are occupied become contagious. There are three common types of level-shifted modulation namely;

- i. Phase/in-phase disposition (PD): all the carrier signals are in phase.

- ii. Alternative phase opposite disposition (APOD): all the carrier signals are alternatively in opposite disposition.

- iii. Phase opposite disposition (POD): the carrier signals are opposite above the zero references and the zero references.

The gating pulse of level-shifted modulation is gained by comparing the reference signal,  $V_{ref}$  with the carrier signals,  $V_c$ .  $V_{ref}$  must be greater than  $V_c$  to generate a signal above zero references and vice versa for the signal below zero references. Figure 2.11 (a) to Figure 2.11 (c) show the different types of level-shifted modulation. The sinusoidal waveform indicates the  $V_{ref}$  whereas the multicolours triangular waveforms indicate  $V_c$  (Jani & Kapil, 2016).

Figure 2.11: (a) Phase/in-phase disposition, (b) Alternative phase opposite disposition, and (c) Phase opposite disposition.

## 2.3.2 SV-PWM

SV-PWM is the most preferable real-time modulation technique. The switching state for SV-PWM is denoted by  $n^3$  where n is the level of output voltage. For example, a two-level inverter will have a total of eight switching states. Six of the total states are considered active states or simply, the ON state. Meanwhile, the remaining two are known as the zero states or simply OFF states. The switching states of the two-level inverter are tabulated in Table 2.2. The zero states are given by [PPP]

or [OOO]. This redundancy can be utilized to minimize the switching frequency or to perform other functions.

Table 2.2: The switching state for a two-level inverter

| Space          | Switching states         |       |

|----------------|--------------------------|-------|

| Zero vector    | [PPP]<br>[OOO]           |       |

| Active vectors | $\overrightarrow{V_1}$   | [POO] |

|                | $\overrightarrow{V_2}$   | [PPO] |

|                | $\overrightarrow{V_3}$   | [OPO] |

|                | $\overrightarrow{V_4}$   | [OPP] |

|                | $\overrightarrow{V}_{5}$ | [OOP] |

|                | $\overrightarrow{V}_6$   | [POP] |

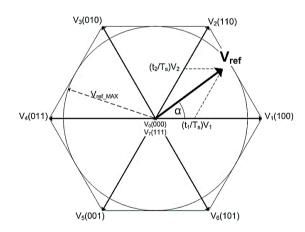

. The switching diagram is shown in Figure 2.12. The active vectors form a regular hexagon with six equal vectors while the zero vectors lie at the center of the hexagon. Both active and zero vectors are stationary, and the switching state is determined by the reference voltage,  $V_{ref}$  rotation. Although SV-PWM is preferable in real-time modulation, this method is less favorable as it becomes more complex as the level of output voltage increases. Thus, it is only preferable for a low level of output voltage.

Figure 2.12: The switching diagram for a two-level inverter (Space Vector Modulation, 2017)

#### 2.3.3 SHE

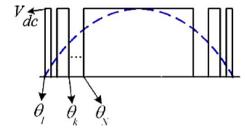

SHE is introduced to improve the quality of the classical pulse width modulation method. This idea was proposed by Turnbull in 1964. In this technique, harmonic components are explained in terms of switching angles in the trigonometric components. Figure 2.13 shows the switching angles of PWM (Ahmadi, Zou, Li, Huang, & Wang, 2011).

Figure 2.13: Multiple switching angles of PWM (Ahmadi, Zou, Li, Huang, & Wang, 2011)

While referring to Figure 2.13, given S is the total number of switching transitions, the Fourier series expansion of the PWM waveform can be expressed in (1);

$$V(\omega t) = \sum_{m=1,3,5}^{\infty} \frac{4V_{DC}}{m\pi} \left( \cos(m\theta_1) - \cos(m\theta_2) \dots + \cos(m\theta_2) \sin(m\omega t) \right)$$

(1)

Where m is the order of the harmonics and  $\theta_k$  are the  $k^{th}$  switching angle. A group of polynomial equations, such as (2) can be utilized to calculate the N switching angles. It also can realize the selective elimination up to  $m^{th}$  order of harmonics (Ahmadi, Zou, Li, Huang, & Wang, 2011). Hence, by calculating the S switching angles, S-1 number of harmonics can be eliminated.  $V_F$  in (2) is defined as the fundamental amplitude.

$$\begin{cases}

\frac{4V_{DC}}{\pi} \left(\cos \theta_{1} - \cos \theta_{2} \dots + \cos \theta_{S}\right) = V_{F} \\

\cos 5\theta_{1} - \cos 5\theta_{2} \dots + \cos 5\theta_{S} = 0 \\

\cos 7\theta_{1} - \cos 7\theta_{2} \dots + \cos 7\theta_{S} = 0

\end{cases}$$

$$\vdots$$

$$\cos m\theta_{1} - \cos m\theta_{2} \dots + \cos m\theta_{S} = 0$$

(2)

However, the drawback of using SHE is the longer computation time to solve the transcendental equation as soft computing methods are used to obtain the optimized switching angle. It is demanding as it is not doable in real-time computation.

#### 2.3.4 Nearest Control Method

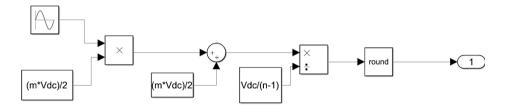

The nearest control method is capable to cater the problem faced in SHE. The nearest control method can be classified into two types: (i) nearest vector control (NVC) and (ii) nearest level control (NLC). This technique operates with low fundamental frequency and produces less distorted output.

NVC is an advanced adaptation of SV-PWM with a similar logical approach with the switching pulses manipulated only based on the vector duration. Thus, NVC will generate pulses by comparing the reference vector position with the existing vectors. NLC shares a similar approach with NVC, but instead of comparing the vectors, NLC compares the actual output voltage level with the rounded reference output voltage level. The NLC computational is very straightforward and easier to be comprehended than NVC (Jonnala, Eluri, & Choppavarapu, 2016).

The nearest voltage level selection in NLC is based on the simple expression per phase. It is determined using (3) where  $V_{RN}$  is the nearest voltage level,  $V_{DC}$  is the voltage source,  $V_{ref}$  is the reference voltage, and f-round is the rounded function (Jonnala, Eluri, & Choppavarapu, 2016).

$$V_{RN} = V_{DC} \times f\text{-round} (V_{ref})$$

(3)

The output voltage is rounded to the lower voltage level when the output voltage is less than 0.5. Meanwhile, when the output voltage is greater than 0.5 or equal; the voltage output is rounded to the nearest higher level. Hence, the power loss for this technique is equal to  $0.5V_{DC}$ . Despite its simple computational, NLC is only suitable to produce a level of output voltage as it cannot eliminate the low-order harmonics. The low-order harmonic is naturally eliminated when the level of the output voltage is high.

#### 2.4 STATCOM

Static compensator or STATCOM is an example of MLI application. This section briefly explains STATCOM and its control scheme.

# 2.4.1 STATCOM Overview

The development in the power industry has increased the dependency on induction loads, induction motors, and power electronic devices. These devices have positive impacts on the power industry, but they also contribute to the power quality problem (Hingorani & Gyugyi, 2000; Tummakuri, Kasari, Das, & Chakraborti, 2018). Power quality problems like voltage imbalance, voltage sag/swell, harmonic distortion, flickering, and low power factor (PF) can reduce the systems' performance if left untreated (Lian-gui, 2016). Hence, they need to be swiftly compensated to maintain the reliability of the system at the optimum rate (Subramaniam, Ramkumar, Amudha, & Kuppusamy, 2017; Hui, 2014).

STATCOM is an advanced version of the VAR compensator. It was introduced in the 1990s. STATCOM is significantly different from the conventional VAR (i.e., thyristor switched capacitor (TSC), thyristor switched reactor (TSR), and the manually switched capacitor) as STATCOM does not have any rotating part. It is also equipped with a new generation high power force commutated semiconductor valve-based inverters, DC capacitors, and an output transformer. Other merits of STATCOM include quick and accurate dynamic response, minimum construction cost due to small size, wide operating range, high efficiency, and high decoupling ability (Haw, Dahidah, & Mariun, 2011). It is widely used for reactive power compensation, voltage regulation like in D-STATCOM, and harmonic compensation like in active power filters (Moran, Dixon, Espinoza, & Wallace, 1999; Pezeshki, .Arefi, Ledwich, & Wolfs, 2018; Zhu, Jiang, & Lian, 2011).

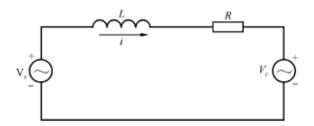

Generally, STATCOM is a shunt-connected voltage sourced converter or simply VSC (Subramaniam, Ramkumar, A.Amudha, & Kuppusamy, 2017) that is commonly used to control the reactive power in the power line; either by injecting or absorbing the reactive power (Kumar & Nagaraju, 2007; Rode, Gaigowal, & Patil, 2018). The single-phase equivalent circuit of a STATCOM is presented in Figure 2.14. From Figure 2.14,  $V_C$  is defined as the generated voltage of the STATCOM,  $V_S$  is the system voltage and i is the current drawn by the STATCOM. L and R are defined as the AC inductance and reactance, respectively (Sharma & Gidwani, 2018).

Figure 2.14: The single-phase equivalent circuit of the STATCOM system (Subramaniam, Ramkumar, A.Amudha, & Kuppusamy, 2017)

The STATCOM operation can be divided into 3 modes which are the capacitive mode, the inductive mode, and unity. When  $V_S$  is lower than  $V_C$  (i.e., the capacitive mode), the STATCOM will generate and inject reactive current into the electric line. On the contrary, when  $V_S$  is greater than  $V_C$  (i.e., the inductive mode), STATCOM will absorb the reactive current. The system is said to be in unity when  $V_S$  is equal to  $V_C$ . At this point, the net flow of reactive current is zero (Kadu, Jawale, & Muni, 2020; Sharma & Gidwani, 2018).

According to (Sharma & Gidwani, 2018), the first STATCOM manufactured in China was equipped with a multi-pulse inverter and zig-zag transformer. This technology is still widely used today. However, the credibility of the zig-zag transformer is questionable as the said transformer is bulky, high loss, spacy, and difficult to control.

The MLI's ability to produce a high level of output voltage has eliminated the need for a transformer. Furthermore, the MLIs' power quality improves as the level of output voltage increases. This also eliminates the need for the filter as the output enhancer. MLI is also convenient for STATCOM applications due to low semiconductor voltage stress, electromagnetic interference, and switching loss. These advantages made MLI for power systems and power quality enhancement applications like STATCOM. MLI-based STATCOM is convenient for high power applications (Gultekin & Ermis, 2013; Kangarlu, Babaei, & Sabahi, 2013; Kangarlu & Babaei, 2013).

#### 2.4.2 The Control Scheme

STATCOM output voltage control method can be classified into (i) phase angle control where the phase angle is varied while the modulation index and pulse width modulated VSC are kept constant, and (ii) hybrid control where both phase angle and modulation index are varied (Chatterjee & Joshi, 2010).

The typical double loop method in (C.Schauder & Mehta, 2002) is an example of hybrid control. The two loops are the outer loop and the inner loop. The outer loop is responsible to give the desired active and reactive currents to the control point of common coupling (PCC). Meanwhile, the inner loop controls the inverter currents in zero steady-state error. This control scheme required a total of four PI controllers, resulting in a complex and demanding realization.

The direct output voltage (DOV) control that utilized only two PI controllers was introduced to reduce the former's complexity. This control scheme was designed based on the instantaneous power theory proposed by (Chen & Hsu, 2003). DOV can be divided into direct control and indirect control. For direct control, STATCOM utilizes a constant DC-link voltage that is high enough to produce output voltage at any desirable value. Meanwhile, the indirect control varies the magnitude of the output voltage by shifting the switching pattern to partially charge and discharge the DC-link capacitor.

Although this control method is less complex, dealing with the non-linear characteristics of the STATCOM like the accuracy and the speed of voltage control is demanding. Thus, more advanced controllers like fuzzy PI control scheme, particle swarm optimization based self-tuning PI control scheme, and genetic algorithm-based PI controlled were introduced (Ajami & Hosseini, 2006; Eshterhardiha, Poodeh, & Kiyoumarsi, 2007; Wang, Zheng, Li, Wang, & Yao, 2011).

Among the advanced method, particle swarm optimization has successfully achieved a satisfactory dynamic response under the balance load. In addition, the control strategy is simpler than the formal fuzzy approach. The strategy also does not depend on the evaluation function to determine the control gain. Instead, it used Runge-Kutta, a numerical method to specify the performance in real-time. Even so, the fuzzy method and particle swarm optimization require complex formulation that will be troublesome to deploy into DSP (Haw, Dahidah, & Almurib, 2014).

#### 2.5 Conclusion

This literature study is to facilitate the understanding of MLIs. In this study, CHB-MLI, FC-MLI, and DC-MLI are regarded as conventional MLIs. They have their fair share of pros and cons, but their common limitation is the number of components used. In order to produce the output voltage close to the ideal waveform, the MLI must have the ability to produce a high level of output voltage. This will become a liability

to conventional MLIs. Therefore, a lot of new topologies had been proposed over the years to reduce the number of components.

The literature study also includes modulation techniques and STATCOM. Modulation techniques are used to synthesize the AC output from the DC input. Each technique has its pros and cons. It also can affect the reliability and complexity of the MLI. Meanwhile, STATCOM is an example of MLI application in the power industry. The topology proposed in this study will be implemented into a STATCOM to demonstrate its usability in the industry.

#### Chapter 3:

### Research Methodology

## 3.1 Chapter Introduction

This chapter provides an outline of the research methodology to propose a new topology of cross-switched MLI. It includes the designing process, data collection process, data analysis techniques used, and the limitation of the chosen research method.

### 3.2 Research Methodology